# Arithmetic Units: Data Manipulation

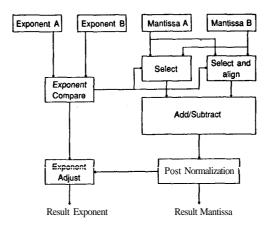

If one considers that a computer is "one that computes," then perhaps the principle function of the machine is to operate on data. That is, we want to manipulate information in a predetermined fashion, according to some rules and methods that make sense. The earliest computers were built to do arithmetic at a higher rate than previously attainable, at an accuracy providing the detail needed. These machines were often used in some military capacity, such as building tables for ballistics operations. In the last chapter we examined some of the methods for information representation, and the limitations of those methods. In the **next** chapter we will discuss the instructions that the machines utilize, that is, instructions to manipulate the information and instructions to control the computer system itself. In this chapter, we **are** concerned with the design of the circuitry for doing the actual data manipulations, that is, hbw does one design circuitry for performing additions, multiplications, and divisions?

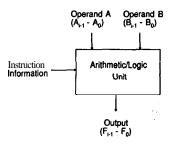

Many times in the discussion of a computer system we gather all of these functions together and consider them to be performed by a single block of logic called an **arithmetic/logic** unit (ALU). Such a block is shown in Figure 3.1. This diagram is directly applicable to LSI ALUs, such as the '181 or '381; however it is also applicable to dedicated units such as the THCT1010 Multiplier/Accumulator. Some ALUs may require additional lines to provide a carry input or to handle status bits on output. In the figure, the source of the operands is left unknown, as is the destination of the result. The interconnection of the components is a function of the type of computer and its intended application, as we will discuss later. But now our concern is with the ALU. Logical functions are achieved by gating the appropriate function to the output. For example, the function A AND B is achieved by having each A<sub>1</sub> ANDed with the corresponding B<sub>1</sub> to derive F<sub>1</sub>. The logic operations can be achieved with minimal gate delays and is therefore a relatively fast operation. The more interesting operations are those required for the arithmetic manipulations.

Figure 3.1. Connections for an Arithmetic/Logic Unit.

#### 3.1. Addition: the Universal Data Operation

One of the favorite questions asked by **instructors** teaching basic logic design is. what is a universal logic gate? The basic premise demonstrated by this question is that a NAND gate is considered a universal logic gate because all of the basic functions — AND, OR, EX-OR, and so on — can be derived by different combinations of NAND gates. In a similar fashion. NOR gates **are** also universal logic gates. The same type of statement can be made concerning arithmetic operations and the add function. All of the various arithmetic operations — add, subtract, multiply, and divide — can be implemented by appropriate combinations of it, then we will consider the look-ahead carry **process** that can be used to speed up the **add function. Other applications of add functions, such as the** carry save adder or the Wallace tree adder. will be treated with other functions such as multiply.

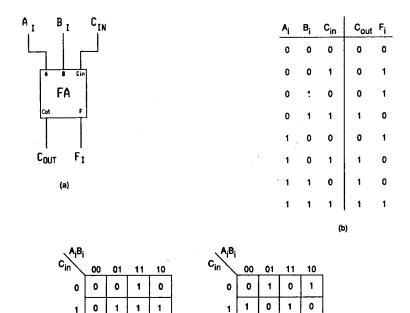

A basic cell that can be used to perform additions is the full adder (FA). shown diagrammatically in Figure **3.2(a)**. As shown, the function of the FA is to add two bits (**A**<sub>1</sub> and **B**<sub>1</sub>) and the **carry** fmm a stage of lower significance ( $C_{IN}$ ) to produce a single bit of output (**F**<sub>1</sub>) and a carry out to the next stage of higher significance ( $C_{OUT}$ ). The **tuth** table for this function is shown in Figure **3.2(b)**. Several observations can be made after examination of the truth table. For example, the function of a FA is to take three bits of equal significance as the three input bits, and  $C_{OUT}$ , which is one bit more significant. Another observation is that the output **forms** a 2-bit number ( $C_{OUT}$ , **F**<sub>1</sub>) which indicates how many "one" bits there are in the three input bits. The four possibilities (0, 1, 2, 3) are the permissible number of asserted bits on the inputs.

Figure 3.2 also contains **Karnaugh** maps for  $C_{OUT}$  and  $F_1$ , and the resulting logic equations in sum-of-products form. The sum bit ( $F_1$ ) is also shown in an **exclusive-OR** representation. The equations are then implemented with the appropriate logic. The implementation of the sum bit is shown in the **sum-of**products NAND implementation as well as the **exclusive-OR** implementation. In either case, the output bits **are** formed from two levels of logic. That is, between any input and an appropriate output there are two gates, and hence two gate delays. (One set of gates is for the AND function; the other set of gates is for the OR function.) This is true for **any** combinational circuit: if one is willing to utilize enough gates, each of which has the requisite number of inputs, it is possible

$\textbf{F}_{i}=\overline{\textbf{A}}_{i}\overline{\textbf{B}}_{i}\textbf{C}_{in}+\overline{\textbf{A}}_{i}\textbf{B}_{i}\overline{\textbf{C}}_{in}+\textbf{A}_{i}\textbf{B}_{i}\textbf{C}_{in}+\textbf{A}_{i}\overline{\textbf{B}}_{i}\overline{\textbf{C}}_{in}$

$\mathbf{F_i} = \mathbf{A_i} \oplus \mathbf{B_i} \oplus \mathbf{C_{in}}$

(c)

Figure 3.2. Design of a Full Adder (FA).

to accomplish any logical function in two gate delays. It may not be desirable or practicable, but it is possible. We will utilize this fact as we examine the times required to **perform** various functions. Thus, to perform the addition of the two bits  $A_I$  and  $B_I$  with carry, requires two gate delays **from** the time that the inputs **aze**, stable.

At this point it is useful to comment on the design methodology for combinational circuits, which is exemplified by the full adder. **The** first step in the design of any combinational system is to understand the problem at hand, which is a nontrivial **requirement**. Once the problem is understood, the problem and its solution can be stated succinctly in prose, identifying the input and output variables. From the problem statement, truth tables can be established, equations derived, and gating networks developed. When the solution is complete, simple tests can be performed to ascertain that the outputs do indeed perform the desired function, and that the requirements of the initial problem **are** satisfied.

For the full adder, the basic requirement is the addition of two numbers. As we discuss the various arithmetic operations in this chapter, we will first seek to understand the requirements of the underlying process, then proceed to determine a design which will perform the required work and meet the other needs of the system. The simplified block diagram shown in Figure 3.2(a) seems innocuous in appearance, but before progress can be made toward a reasonable design. the process which is being performed must be understood. One demonstration of the understanding required is a correct truth table, as shown in Figure 3.2(b). A designer's concept of what the device should do is identified by this table. If a design does not function properly, the usual debugging approach is to see if the wiring matches the logic as described by equations, and that the equations were correctly obtained from the truth table/Karnaugh maps. This approach will find errors that are implementation errors. However, it is often the case that the logic is an accurate implementation of the logic equations, and that the logic equations themselves are incorrect. This may be true not because the Boolean algebra was done incorrectly, but rather because the designer's understanding of the pmblem was flawed. And one place where that understanding will be displayed is in the truth table; thus, this step should also be examined in detail in both the design and checkout process.

In the design process, the logic equations are derived from the truth table representation of the problem. Each minterm can be written down individually from the truth table, and rules of logic utilized to find the minimal form. Or some other method can be used to find an acceptable logic equation. The Kamaugh map method is exemplified by Figure 3.2(c). From the equations, the proper arrangement of logic gates can be derived. The exact implementation techniques will be dictated by the design constraints established by the problem itself.

Portions of the process — from understanding to truth table to Kamaugh maps to logic equations to implementation — can be aided by CAE (computer aided engineering) systems or CAD systems (Computer Aided Design). However, it is imperative that a designer be able to understand the results of CAE/CAD systems, and be able to ascertain correctness of the final result. The computer aided systems will do a speedy and precise job. but the underlying algorithms used by the computer system may not coincide with the desires of the system designer. Therefore, care must be taken to assure that the final results provide a reasonable solution to the initial problem.

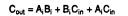

In general, we **are** not interested in computers operating on a single bit at a time. Rather, we **are** concerned with computers that operate on a collection of

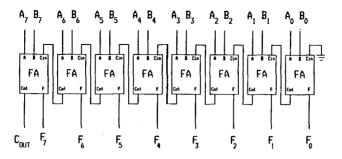

bits. Full adders can be cascaded to the width of the system, as shown in Figure 3.3. In the figure, two 8-bit numbers are added to produce an 8-bit result. An additional input is the carry in  $(C_{IN})$ , which may come from a status register or other source; and the carry out  $(C_{OUT})$  from the addition is available for the system.

This is not the fastest method to perform an addition, as we will see, but it will provide the correct answer. The time required to perform addition by this method, as measured from the time that all inputs **are** stable. is **directly** proportional to the number of bits in the word. This kind of addition process can be **called** a ripple carry adder (**RCA**), since the **carry** at each stage is propagated to the next stage. We will label the time required by this type of addition **as**  $T_{ADDec}$ , and this time is given **as**:

$$T_{ADD_{RCA}} = N \times T_{FA}$$

$$= N \times (2 \times G)$$

That is, the time for an *N*-bit addition is just *N* times the time for a single bit addition ( $T_{FA}$ ), and the time for a single bit of addition is two gate delays. Thus, the time for a full adder implementation of an addition module is linear in the number of bits to be added.

The details mentioned above are often hidden inside integrated circuits. However, in designing or understanding the circuitry embedded in **ICs**, this information may be very beneficial. Full adders can be purchased in IC form, such as the '80. Or one can consider that four such stages **are** cascaded in a single unit. such as the '83, a 4-bit adder. However, if one examines the circuitry internal to the '83, the carry out of the chip is generated in a different fashion than the FA method just described. This method is the look-ahead method, which we will examine later. But first let's apply the add technique described above to a **sub**-tractor.

*Example 3.1:* Full *subtractor:* Using the methods described above, design a full subtractor (FS).

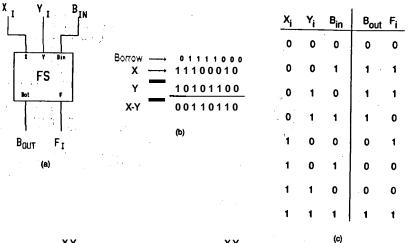

The first step in this process is to understand the requirements of the design. Figure 3.4(a) is a diagram that indicates the function of the full

Figure 33. A Word Adder Composed of Full Adders.

(d)

Figure 3.4. Design of a Full Subtractor (FS).

subtractor. Two bits from the data word  $(X_i, Y_i)$  are inputs to the FS, as is a line from the previous stage. This line is the **borrow** in  $B_{IN}$ . The outputs are the subtract output for this stage.  $F_{I_1}$  and the borrow output to the next stage,  $B_{OUT}$ . The algorithm for doing subtraction in base 2 is exactly the same as the algorithm used for the base 10 taught in grade school. One

"borrows" bits (digits) from places of higher significance **as** needed to be able to perform the subtraction of a bit. Figure **3.4(b)** is an example of a binary **subtraction**; this example is given **becau**:e all of the information necessary to create the complete truth table is present. Figure **3.4(c)** is the truth table for the full subtractor, which **has** been derived by examining the subtraction of Figure **3.4(b)** and filling in the table **as** needed.

A good thing to do in unfamiliar circumstances (base 2 subtraction is not a daily occurrence for most people) is to **convert** to a familiar system and do the subtraction. The base 10 representation of this operation is 226 – 172 = 54; and since 001101102 =  $54_{10}$ , we feel much better about the accuracy of the results. Alternative derivations of an answer provide methods for checking the results of an algorithm, and should be employed as necessary to build confidence and purve correctness.

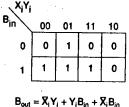

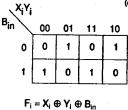

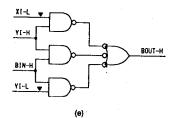

The Kamaugh maps for the subtractor are shown in Figure 3.4(d), as well as the resulting logic equations. Finally, the gating function for the borrow is given in Figure 3.4(e). The gating is not given for the subtract output since  $F_i = X_i \oplus Y_i \oplus B_{iN}$  is exactly the same formula as the sum out for a full adder. The same circuitry can be used for both functions. Note also that the logic equation for the **borrow** has the same form as the logic equation for the carry out of the full adder. but the inputs are different. Thus, with a little ingenuity and some gating functions, the same circuitry could be used for the A + B, A - B, B - A, and  $A \oplus B$ . The latter function is achieved by disabling the carry function; forcing the **carry** to a logical zero allows  $A \oplus B \oplus C$  to reduce to  $A \oplus B$ .

The timing for a multiple bit full subtractor is exactly the same as the timing for the carry propagate adder,

# $T_{\rm SUB} = N \times T_{\rm FS} = N \times 2 \times T_G$ .

Subtraction of two values can be accomplished by a system of subtractors created as described here. However, a subtraction system can also be created by using **an** adder system (composed, for example, of '283s) and the complement-and-increment method of negating a value. The value to **be** subtracted is complemented with a set of inverters, and the increment is supplied by asserting the carry-in of the adder system.

The similarity between the subtraction process and the addition process is not really surprising. but it points out a situation that often arises. In many circuits, both combinational circuits, such as those discussed here, and sequential circuits, such as direct multiplication methods discussed later, there **are opportunities** to utilize some of the same elements of the circuit for more than one function. Here, one set of gates can be utilized for both the addition and subtraction functions. The same concept applies in some sequential circuits, where counters (or other components) can be reused for different functions. The key to the effective use of system resources is to achieve a complete understanding of the functions to be performed by the system, and to combine that with a knowledge of the logic requited to perform those functions and the capabilities of that logic. This combination will allow a designer to trade off system resources against system requirements to achieve an effective design.

Word adders composed of full adders are an example of a minimal gate solution to a pmblem, but the time required for the result may provide an

unacceptable limit to system performance. Another approach is to add more complexity to the add process to do the function faster. In order to do this, we look **again** at the logic equations for the addition process:

$$F_I = A \oplus B \oplus C_{IN}$$

$C_{\text{OUT}} = AB + AC_{\text{IN}} + BC_{\text{IN}}$

$$= AB + C_{IN} \cdot (A + B)$$

Looking at these equations we make the following observations, some of which have been made before. The creation of the  $f_1$  signal requires but two gate delays from stabilization of input to output stable. The same can be said for the first form of the carry equation, but the second form requires three gate delay?. However, the second form allows the addition process to proceed in a different fashion. Here the data inputs (as opposed to the carry input) are grouped into two terms: AB is called the carry generate (CG) function since if this term is asserted there will be a carry (hence, the carry is "generated") regardless of the value of the carry input. The A + B term is called the carry propagate, since if this term is asserted have fast any carry which is supplied to this stage is passed on to the next. (Note that the function  $A \oplus 6$  would also be a valid carry propagate function. Why?) Arrangement of the add operation to include the carry generate (CG) and carry propagate (CP) functions results in a module which produces:

$$F_{I} = A \oplus B \oplus C_{IN}$$

$$CG = AB$$

$$CP = A + B$$

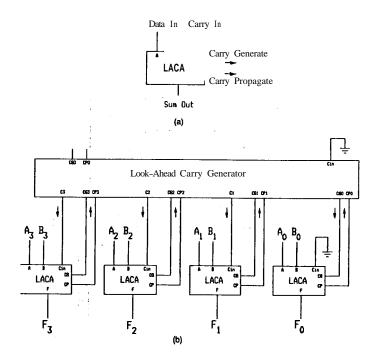

Figure 3.5(a) shows a diagram of such an adder. Note that the time required to create the carry generate and carry pmpagate is a single time delay. But more importantly, note that the carry generate and carry propagate lines are not functions of the carry input. This means that if we arrange several look-ahead carry adder (LACA) modules as shown in Figure 3.5(b), then all of the CG and CP lines will be stable one gate delay after the inputs are stable. In Figure 3.5(b) these lines are inputs to another module, called a look-ahead carry generator (LACG). The LACG has the responsibility of creating the cany for each stage; it does this by **looking** at the carry generate and cany propagate signals from all of the stages. If  $C_{IN}$  is asserted then  $C_0$  will be asserted.  $C_1$  will be asserted if the carry generate of the previous stage (CG<sub>0</sub>) is asserted. OR if CP<sub>0</sub> is asserted AND C<sub>IN</sub> is asserted. As the carries become more significant, the amount of logic needed to generate the carry becomes larger. But it is important to note that, if the designer of the LACG is willing to supply a sufficient number of gates, then *all* of the carries will be generated in two gate delays. Thus, the addition shown in Figure 3.5(b) requires 5 gate delays: one to generate the CG and CP for each LACA, two to generate all of the appropriate carries, and two more to propagate the effect of the carries to the outputs. This is faster than the 4  $\times$  2  $\times$  G = 8 gate delays required for the FA implementation.

It is apparent that much of the complexity has been moved to the LACG. which becomes more complex as the number of modules that it services increases. **A** LACG that provided the carries for all 64 bits of an adder would be

Figure 35. Look-Ahcad Carry Adder (LACA) and its Connection in an Adder Circuit.

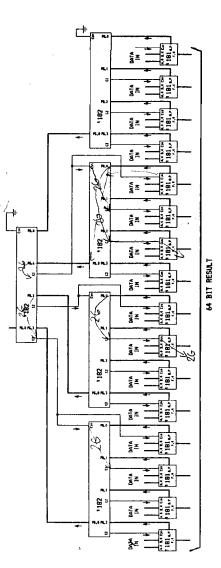

prohibitively expensive in terms of numbers of gates, or IC real estate. So, the LACGs are designed to cascade in exactly the same fashion as the LACAs. That is, in addition to the carries, the LACG generates a CG and CP that can be utilized by a second stage of LACG; the process continues as far as necessary to perform the work required. Such a system is shown in Figure 3.6. This figure shows the connection of '181s, which are 4-bit ALUs that generate the CG and CP signals required, and '182s, which are the LACGs. These units are both 4-bit units; that is, the ALU performs the addition of 4 bits, as well as generating the CP and CG signals for those 4 bits, and the LACG handles the CG and CP signals from 4 modules. Because of this added complexity in the ALU module, the CG and CP signals will require a minimum of two gate delays to create, as opposed to the single gate delay for a single bit unit. The time required for a carry lookahead addition is then given by:

$$T_{\text{LACA}} = 2 + 4 \times (\lceil \log_b(N) \rceil - 1)$$

where there **are** N bits to be added, and the number of bits handled by the **ALUs** and LACGs is **b**. When no LACG is needed (up to b bits), then the time required

is simply two gate delays. Then, as the number of bits increases, the **LACGs** are added in a tree type of structure, where the **fanout** of each node of the tree is b. This gives rise to the second term in the above equation. As the number of bits (*n*) increases, each time the term  $\log_b(N) - 1$  crosses a b boundary, that is, when the number of bits to be added crosses an exponential integer (*b*'), then the depth of the tree increases by one, and the number of gate delays required increases by four. By utilizing the look-ahead process, the time required for addition has been changed from function linear in the number of bits to a process that is logarithmic in the number of bits. And the base of the logarithm is the number of bits handled by the LACAs and LACG; a larger b results in a faster adder for a given number of bits. For the adder shown in Figure 3.6, the time would **be**:

$$T_{LACA} = 2 + 4 \times (\lceil \log_4(64) \rceil - 1)$$

= 2 + 4 × (3-1)

= 10 gate delays

The 10 gate delays for the look-ahead process of Figure 3.6 are a limit, which will not, in general, be fully attained by commercial parts. This is because parts such as the **'181** and **'182** will reduce the number of gates required for the final function by allowing three or four levels of gates, instead of the theoretically possible two. Nevertheless, the look-ahead method for addition is much faster than addition with chains of full adders. At this time we will introduce another term for the add process: carry propagate adder, abbreviated CPA. By this term we indicate that the carry will propagate all the way through the addition, but the method of carry implementation, whether ripple carry or **Carry** look-ahead, is not specified.

The addition function provides an example of the tradeoffs available in creating a system. A carry propagate adder will perform a function with a minimal number of gates, but the time will **be** correspondingly long. A carry look-ahead adder will perform an addition in a minimal amount of time, but the number of gates required for the function has correspondingly increased. Each system designer must examine the resources available (time, gates, silicon real estate, etc.) and allocate those reaources in an appropriate manner.

## 3.2. Status: Results of Arithmetic Operations

Often when arithmetic operations are performed, some information about the answer is as important as the answer itself. That is, many operations are performed simply to find out how things compare: is A larger than B? Is A equal to B? Is A negative? Many of these questions are answerable if certain information is available concerning arithmetic operations. For example, is A equal to B? Well, subtract A from B (or B from A); if the result is zero, then A is indeed equal to B. In general, four pieces of information are produced by these arithmetic operations, and these pieces can be used to form bits in a status register. The four bits are zero, sign, overflow, and carry. We should hasten to add that other types of information are often available in a status register, and we will deal with this type of information in Chapter 4. At this time, we are interested in the arithmetic operations and status that can result from them.

The sign bit is perhaps the easiest to generate: it is the sign of the result of whatever operation was performed by the ALU. For two's complement numbers, this is the **MSB** of the result; for most floating point number systems. This is also the most significant bit. In either case, the sign of the number is fed directly to the status register. Instructions that manipulate arithmetic values (ADD, SUB-**TRACT, COMPARE, etc.)** will modify this bit; instructions that do not do arithmetic (JUMP-CALL, etc.) will not modify the bit. For a precise list of the instructions that do modify the various bits of the status register of an existing machine, the instruction set definition for that machine must be consulted. The opposite is true for a system architect in the process of creating a set of instructions. That is, based on the application area of the machine, the arithmetic operations required. and the number systems utilized, the system designer can, at the time of the definition of the system, identify which operations will have an effect on the status register.

In addition to the sign bit, t h h is also readily available **from** the ALU. If an arithmetic operation resulted in a carry. then this bit is asserted in the status register. Again, the instructions modifing the bit are obtained from the instruction set definition. The hardware of the system, then, must prevent instructions that cannot modify the bit (as defined by the instruction set) **from** actual modification capability. This is accomplished by disabling the load function of the status register bit (carry bit, in this case) within the status register.

The zero bit is also easy to visualize, conceptually. If the result of the operation is zero, then the bit should be set. Often this operation will be utilized by more instructions than strictly the arithmetic ones. For example, in some systems MOVE instructions will test the value being moved to see if it is zero. As before, the exact list of instructions that modify the zero bit will be obtained from the instruction set definition. The logic required is a test on each line to check its assertion level. For ALUs not providing this information on a separate status line, then all of the output lines must be checked. However, some ALUs provide a single line that will be asserted if any of the ALU lines are not zero. The advantage of this method is that these lines are constructed with open collector technology, and can be tied together without external gating. Thus, when all ALU outputs are zero, none of the lines is asserted, and the recognizable output is high, which is exactly what is needed by the status register.

<u>The overflow bit</u> is the condition that requires more than rudimentary logic. When should the **overflow** bit be set? The overflow bit indicates that the operation performed has exceeded the ability of the number system to represent information. Thus, one of the basic pieces of information needed (or assumed) is the number system being utilized. Our examples will concentrate on the two's complement number system. Other number systems may call for other conditions to identify an **overflow**. For example, consider an **8-bit**, two's complement number system. From our previous considerations we know that this number system can represent values from -128 to +127. If we add  $61_{10}$  to  $45_{10}$ :

| 00111101 | This is 61 in base 2.                                |

|----------|------------------------------------------------------|

| 00101101 | This is 45 in base 2.                                |

|          | Now add them together.                               |

| 01101010 | The result is equivalent to 106, the correct answer. |

This operation does not exceed the ability of the number syslem to represent information. However, if we add  $75_{10}$  to  $58_{10}$ :

| 01001011 | This is 75 in base 2.            |

|----------|----------------------------------|

| 00111010 | This is 58 in base 2.            |

| 10000101 | In 2's complement. this is -123. |

If the **pattern** is considered an unsigned integer, then the answer is correct (**133**<sub>10</sub>). But as a two's complement number, the ability of the number system to represent information has been exceeded. Two positive numbers have been added together, and the result was a negative number. The same thing will happen if two large negative numbers are added together: a positive number will **be the apparent result**. Again, the ability of the system to represent information has been exceeded: an overflow has occurred. When this happens in an arithmetic operation, then the overflow bit of the status register will be set. If a number system other than the two's complement number system is to be used, then a similar set of operations must be checked, identified by the number system itself.

Example 3.2: Overflow *circuit*: Design a circuit that will detect the occurrence of an overflow condition for a two's complement system.

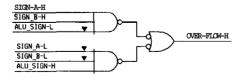

As stated above, the overflow will occur when two positive numbers **are** added together and a negative number results, or when two negative **numbers** are added together to form a positive result. So the observation points **are** the sign bits: if the two input sign bits **are** positive (zero), and the output sign bit is negative (one), then an overflow has occurred. Likewise, if the two input sign bits are negative (one), and the output sign bit is positive (zero), then an overflow has occurred. **A** circuit to detect this condition is shown in Figure 3.7.

If the **internal carries** of the addition process are available, this circuit can be replaced by a single exclusive-OR gate. The **exclusive-OR** gate would detect a difference between the carry-in and the carry-out of the most significant stage; these two lines will differ when the overflow condition exists.

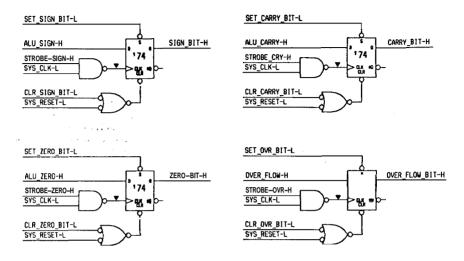

The arithmetic bits included in the status register **are** set and cleared as directed by the control logic for the system. That is, not all of the **instructions** will **be** allowed to modify the status bits, and some status bits will be modified by more instructions than other bits. This will require a system which is capable of selectively controlling each of the bits. If we limit ourselves to fairly standard **TTL** parts, then such a circuit is shown in Figure 3.8. Note that each of the bits is individually **setable** and clearable, as well as being reset jointly by a system reset. If the instruction set does not require the ability to individually set and clear each of the bits, then the amount of logic required for this function will be reduced.

Figure 3.7. Circuit for **Overflow** Detection (Two's Complement System).

Figure 3.8. Arithmetic Bit Formation for a Status Register.

Some manufacturers provide many of these functions in a single IC, such as the **AM2904**. This reduces the number of chips required but not the control lines: The AM2904 has 17 control lines associated with this function.

These status bits form both a source and a destination of information in the performance of computer functions. Arithmetic operations often require a carry input, which is provided from the status register. Addition operations may change all four of the bits discussed above. Logical operations can also affect the **ZETO** bit. And program control operations can test **status** bits to control the flow of control in the system. Thus, these four bits can form a portion of a status register, which performs a central function in the overall system operation. We will include other kinds of status information in the discussion of instruction sets in Chapter 4.

# 3.3. Iterative Multiplication Methods

Fmm the very early days of computers one of the things needed was a multiplication capability. Many of the early machines were funded by defense needs, such as calculation of ballistics tables and other strictly computational tasks. For these tasks a multiply was required, and many early machines had a hardware multiply **instruction**. Later, when memory speeds improved dramatically, subroutines could be used to do the multiply and still accomplish the function faster than the previous hardware systems. This allowed a sizeable reduction in hardware for the computer. Still. hardware multiplication capabilities have been utilized more and more as the relative cost of hardware has decreased. Let us examine some of the methods for doing multiplication.

First, let us define the problem in exact terms, then select a sample problem to follow through the various methods of multiplication. What we want to find is **the** product.  $P_i$  of two values, A **and** B.

#### $P = A \times B$

A and *B* are called the multiplicand and multiplier; let us assume that they are both 5-bit numbers:  $A_4A_3A_2A_1A_0$  and  $B_4B_3B_2B_1B_0$ . We know from Chapter 2 that these can assume values from 0 to  $2^5 - 1 = 31$ . So, the largest product would be  $31 \times 31 = 961$ . To represent the number 961 requires  $\left[\log_2 (961)\right] = 10$  bits; hence, we say that the product of two N-bit numbers requires  $2 \times N$  bits to represent. With our assumption of a positional notation system, the **product can** be repersented as:

$$P = A \times B$$

=  $A \times B_4 B_3 B_2 B_1 B_0$

=  $A \times B_4 \times 2^4 + A \times B_3 \times 2^3 + A \times B_2 \times 2^2 + A \times B_1 \times 2^1 + A \times B_0 \times 2^0$

In practice. we write this as follows:

|                                     |       |                                                                  |                                                               | ×                             | A <sub>4</sub><br>B <sub>4</sub>                              | А <sub>3</sub><br>В <sub>3</sub> | A2<br>B2 | A <sub>1</sub><br>B <sub>1</sub> | А <sub>0</sub><br>В <sub>0</sub>      |

|-------------------------------------|-------|------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------|---------------------------------------------------------------|----------------------------------|----------|----------------------------------|---------------------------------------|

| PP₀→<br>PP₁→                        |       |                                                                  |                                                               | A R.                          | $\begin{array}{c} A_4 \cdot B_0 \\ A_3 \cdot B_1 \end{array}$ |                                  |          | $A_1 \cdot B_0$<br>$A_2 \cdot B$ | <b>A</b> <sub>0</sub> ∙B <sub>0</sub> |

| PP₂→                                |       |                                                                  |                                                               | A <sub>3</sub> B <sub>2</sub> | $A_2 \cdot B_2$                                               | $A_1 B_2$                        |          | 10 DI                            |                                       |

| $PP_3 \rightarrow PP_4 \rightarrow$ | A₄·B₄ | A <sub>4</sub> ·B <sub>3</sub><br>A <sub>3</sub> ·B <sub>4</sub> | $\begin{array}{c} A_3 \cdot B_3 \\ A_2 \cdot B_4 \end{array}$ |                               |                                                               | A0.B3                            |          |                                  |                                       |

| PR→                                 |       |                                                                  |                                                               | Sun                           | n of all a                                                    | rows                             |          |                                  |                                       |

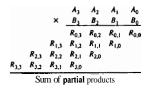

The five rows labeled **PP**<sub>0</sub> to **PP**<sub>4</sub> are known as the partial product **array**. For this **multiplication**, the rows of the partial product array are composed of 5 bits, and each bit is an AND function of a bit from the A input and a bit from the *B* input. The product itself (PR) is the sum of the **rows** of the partial product array. when the **rows** have been aligned appropriately for bit significance. The effect of the multiplication by powers of two in the above equation is accounted for by the shifting of the rows in the partial product array. This is the same situation as that taught in grade school for base 10:

| 1324    |

|---------|

| 2435    |

| 6620    |

| 3972    |

| 5296    |

| 2648    |

| 3223940 |

In the base 10 example, each mw in the partial product array is the result of the multiplication of the first number by one digit in the second number. As

explained above, in the base 2 system this product is very easy to obtain, since multiplication in base 2 is accomplished on a bit-by-bit basis. Therefore, the creation of the partial product array for a base 2 example is very simple: merely AND each bit in the multiplicand with the appropriate bit in the multiplier. Then the rows of the partial product **array** are summed in some fashion. Let us examine some methods for accomplishing this.

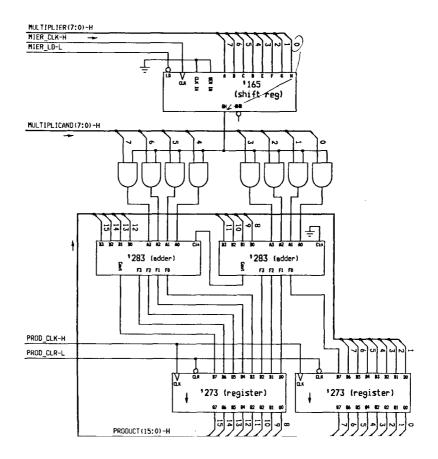

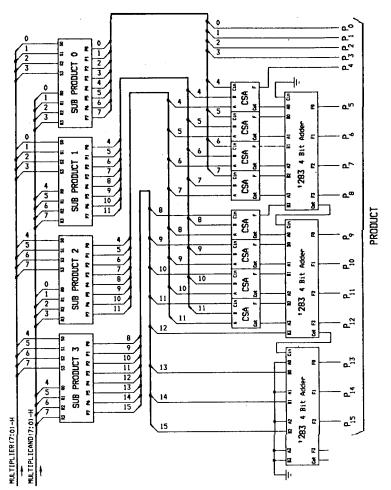

The most straightforward method for doing the multiply is the traditional "shift and add" method. One implementation of this is shown in Figure 3.9. The multiplier shown in the figure is set up to do an 8x8-bit multiply. Several

Figure 3.9. Data Path Logic Diagram for Simple Multiplier.

observations can be made concerning this system. Fist of all, the adder used is an **8-bit** adder; this will function properly since the partial product addition is done from the least significant partial product to the most significant **partial** product. There is nothing magic about the order of partial product addition, so long as the bits **are** added in their appropriate significance. **That** is. for an N-bit multiply, the partial products **PP**<sub>0.1</sub> to **PP**<sub>0</sub> could be added in the order shown (**PP**<sub>0</sub> first to **PP**<sub>0.1</sub> last). in the reverse order (**PP**<sub>0.1</sub> first to **PP**<sub>0</sub> last), or in any order deemed convenient because of design considerations.

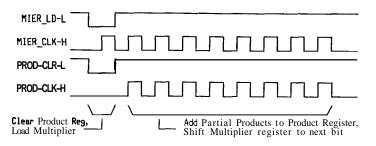

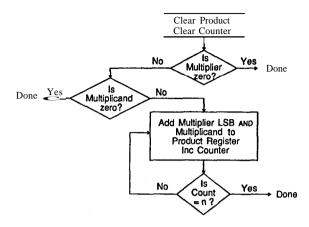

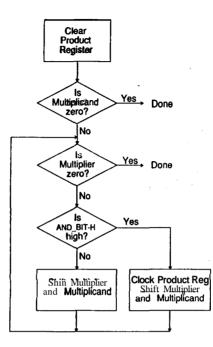

In Figure 3.9, the shifting of the result is accomplished by hard wiring the accumulating sum to line up with the appropriate bit positions in the partial product. And the partial product is created exactly as shown in the above expansion of a binary multiplication: AND gates are used to generate the **partial** product from the multiplicand. The multiplier bit to be used is obtained from a shift register. A timing diagram that will assert the control signals in an appropriate fashion to do the work is shown in Figure 3.10. The timing diagram shows a set of control signals that will work in all cases; however, the resul: can be obtained faster in some circumstances if the control section is modified to look for specific conditions. One such condition is that either the multiplier or the multiplicand is **zero**; in such a case, the result is zero, and the answer can be given immediately. A flow diagram showing such a set of decisions is shown in Figure 3.11. The design of a control section that will create the appropriate signals is the topic of Chapter 5 and will not be covered here.

The circuit shown in Figure 3.9 is only one of a variety of implementations that will accomplish the work of multiplication. Other solutions to the problem would **try** to create the "best" design based on some criteria of the designer. For example, in the design shown in Figure 3.9 two chips **are** required for the AND function; these can be removed by using a slightly more complicated product register capable of shifting internally as well as loading from **an external** source. This reduces the number of chips (and hence board area required) for the function. but will necessitate a slightly more complex control. Another type of design may test for the condition that the remainder of the multiplier is all zero, hence the multiplication is essentially complete. The challenge in that type of design is to **be** sure that the final product bits **are** in the correct bit positions.

No matter what type of data path is selected, and its appropriate algorithm devised, the designer is faced with the problem of proving correctness. Several methods **are** available to do this, **from** simulation of the hardware if such a

Figure 3.10. Timing of Control Signals for Simple Multiplier.

Chap. 3: Arithmetic Units: Data Manipulation

Figure 3.11. Flow Diagram for Data Dependent Multiply Algorithm.

simulation system is available, to examples worked through by hand. Before the design is fabricated, the designer should select several appropriate examples and show that the system will provide proper results.

*Example 3.3: Multiplier Design:* Design a data path for a multiplier that will add the partial products in "reverse" order, from the most significant to the least significant. What are some of the benefits and penalties of doing this?

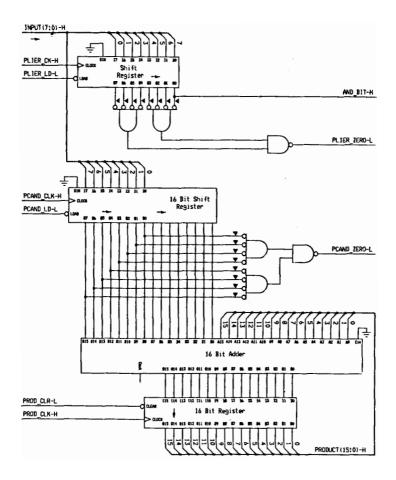

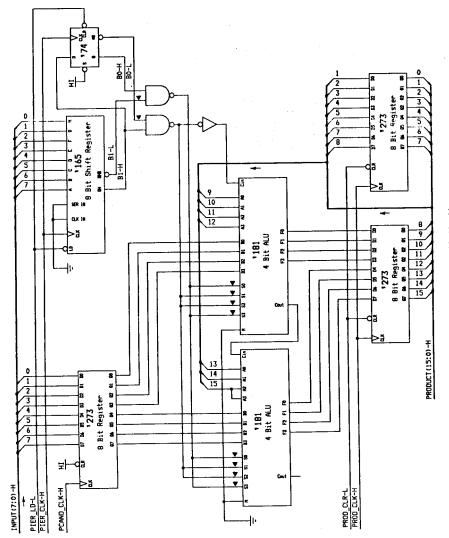

This could be accomplished in a number of ways, one of which is shown in Figure 3.12. The figure shows the parts and principal interconnections needed; a more detailed schematic representation is found in Appendix B. This method requires an adder **as** wide **as** the final product. For simplicity this is shown as four '283s; faster add times could be attained by using an adder with **lookahead** capabilities. The product register is constructed out of '273s, which are 8-bit edge triggered registers. The bits from this register are fed back to one set of inputs on the adders. The inputs to the product registers come from the same bit positions in the adder.

The multiplier register is composed of two '195s which have been configured to be a shift register. The control section will be responsible for asserting the clock line (PLIER\_CK-H) when data is available to be loaded. and also when the multiplication is proceeding. The output of the multiplier register is constantly checked to see if it is zero (PLIER\_ZERO-L).

The multiplicand register is composed of two types of shift registers: '195s and a '164. The '195s provide for the load of the multiplicand value, at the same time clearing the '164 (PCAND\_LD-L). Again note that the control section will be responsible for asserting the load and clock lines in the proper sequence to cause the data to be loaded at the appropriate time, and then shifted during the execution of the multiplication itself. As the multiplicand is shifted out of the '195s, it will be shifted toward lower significance in the '164. This is the method whereby the stated design

Figure 3.12. Data Path for Multiplier of Example 3.3

objective of "reverse" order of partial products will be accomplished. The multiplicand can also be checked for a zero value (PCAND\_ZERO-L) when it is loaded, but this will only be effective at the beginning of the algorithm.

A flow diagram for implementation of the multiplication algorithm is shown in Figure 3.13. This diagram indicates how the algorithm proceeds. and identifies **some** of the benefits of this organization. The first step is to clear the product register; this is the correct answer if the multiplicand is zero, which is checked next. It is also the correct answer if the initial value

Figure 3.13. Flow Diagram for Multiplier of Example 3.3.

in the multiplier is zero, which is the next condition checked. Then the iterations begin in earnest. The value in the multiplicand register is added to the value in the product register; this result may or may not be placed into the product register. That decision is based on the most significant bit in the multiplier register (AND-BIT-H); if the bit is asserted. then the product register is loaded. In either case, the multiplier and multiplicand registers are shifted by one bit position. If the number of iterations is N (8 in this case), then we are done. If not, check the multiplier register to see if we have added in all of the appropriate values. If we have, then the algorithm is finished. As this description points out, the time required for this algorithm is data dependent. It is not necessary to check for zeros, since the algorithm would function correctly with an iteration counter and no data checks. However, by testing the values during execution of the multiply. the number of iterations will depend on the arrangement of one's and zero's in the data. By doing the additions in the "reverse" order, the product bits are in the correct position whenever all the required additions have been performed. Thus, the time to complete the instruction will vary according lo the data. which will speed up the processing.

Another benefit fmm this method is the absence of AND gates to do the individual **partial** product multiplications. The **partial** product is always

added to the accumulating product, but this value is conditionally loaded into the product register, based on the appropriate bit in the multiplier. Thus the **AND** function is supplied by control of the product load line, rather than an **AND** line on every bit.

One of the obvious tradeoffs with this method is that the speed benefits and the reduction in gating (no AND gates) have **been** obtained at the expense of a larger adder and multiplicand register. So, before a designer declares this method **better/worse** than another method, he needs to ascertain the various costs of the method and decide if the **tradeoffs** match his system resources.

The multiplication methods discussed to this point are listative includes: line same adder system is used a number of times until the **correct** result is obtained. One of the questions to be addressed is the time required for the multiplication. The time that we worry about here does not include the time required to load the multiplier and multiplicand registers, and, in an actual implementation, those times need to be included in any timing estimates. The multiplication time.  $T_{MULT}$ , can be grouped into two contributing factors: the setup time.  $T_{SETUP}$ , and the iteration time.  $T_{TEFR}$ .

# $T_{\text{MULT}} = T_{\text{SETUP}} + N \times T_{\text{ITER}}$

The setup time includes the time required to clear the product register and perform any initial checks identified by the algorithm. This is reflected in the "is multiplicand zero" condition in the algorithm of Example 3.3. The iteration time is the time required to create the partial product (**perform** the **AND** function), to add the partial product to the **running** sum, and to load the resulting value into the product register. These times are reflected in the following equation:

# $T_{\text{FTER}} = T_{\text{AND}} + T_{\text{SUM}} + T_{\text{REG}}$

The first term (T<sub>AND</sub>) is the time needed by the algorithm to form the partial product. Note that in some algorithms, such as that described in Example 3.3, this time will be zero, since the same effect is obtained by conditionally loading the product register. The second term  $(T_{SUM})$  accounts for the time required to form the sum of the partial product with the product register. This time will be determined by the adders being used and the interconnection method (carry propagate adders or carry look-ahead adders). The term should reflect the time required fmm all data inputs stable to all outputs stable. The last term  $T_{RFG}$  is a combination of the times required for the register being used, which can be obtained from the data sheet for the device. These include the setup time (the time that the data must be stable prior to the assertion of the clock), the hold time (the time the data must be stable after the assertion of the clock), and propagation delay (the time for stable outputs, from the assertion of the clock). All of these times must be accounted for in deciding on the time required for the clock cycle of the unit. However, if a designer is willing to provide for nonequal clock times, then the time required by the system of Example 3.3 can be reduced. That is, if the AND\_BIT-H is not asserted, then the add will not be needed, and the system can move on to the next bit (shift multiplier and multiplicand) without waiting for T<sub>SUM</sub>.

These multiplication methods can be used to build multipliers out of commercially available parts, such as the system shown in Figure 3.12. Or they can be used to implement multiplications by using resources (adders, registers, and data paths) **internal** to a chip. such as a microprocessor. Since these methods are iterative in nature, they can be readily implemented with microcode methods. We will lwk more closely at microcode in Chapter 5, but an understanding of the iterative nature of the system helps to explain why some manufacturers identify the times required by multiplication instructions in numbers of cycles. And why some multiplication instructions indicate that the time for instruction completion is dependent on the data being used.

Before we move on to direct methods of multiplication, we will note that in the considerations thus far we have carefully avoided any mention of negative numbers. Without any modification, the techniques mentioned will not function for negative numbers. A number of techniques have been used to allow use of negative as well as positive numbers. The technique we will describe here is called Boot's algorithm, after a pair of British th but similar techiques are used elsewhere. These techniques are classified as recoding techniques. since the multiplication is modified by a recoding scheme. Let us see how this is applicable to the problem of multiplication signed numbers.

First of all, we **need to** remember from Chapter 2 that the bits in the number have a different meaning for signed numbers. That is, the most significant bit has a different **meaning**. The five bit numbers which were used earlier for an example had the form and meaning:

> $B = B_4 B_3 B_2 B_1 B_0$ =  $B_4 \times 2^4 + B_3 \times 2^3 + B_2 \times 2^2 + B_1 \times 2^1 + B_0 \times 2^0$ =  $B_4 \times 16 + B_3 \times 8 + B_2 \times 4 + B_1 \times 2 + B_0 \times 1$

The difference for a two's complement number is shown in the following fashion:

$$B_{2's \text{ COMP}} = B_4 \times (-16) + B_3 \times 8 + B_2 \times 4 + B_1 \times 2 + B_0 \times 1$$

As can be seen from the equation, the most significant bit is different in its weighting formulation and must be treated accordingly. The Booth's algorithm approach can be understood by first doing some algebra on the number. In a step-by-step fashion, we can express the two's complement number in a new form:

$B_{2's \text{ COMP}} = (-16) \times B_4 + 8 \times B_3 + 4 \times B_2 +$

$$2 \times B_1 + 1 \times B_0$$

$$= (-16) \times B_4 + (16-8) \times B_3 + (8-4) \times B_2 +$$

$$(4-2) \times B_1 + (2-1) \times B_0$$

= (-16) \times B\_4 + 16 \times B\_3 - 8 \times B\_3 + 8 \times B\_2 - 4 \times B\_2 +

4 \times B\_1 - 2 \times B\_1 + 2 \times B\_0 - 1 \times B\_0

= (-16 \times (B\_4 - B\_3) - 8 \times (B\_3 - B\_2) - 4 \times (B\_2 - B\_1) - 2 \times (B\_1 - B\_0) - 1 \times (B\_0 - 0)

The values in parentheses in the above equation are composed of the subtraction of two bits. and can have the values +1, 0, or -1. Note that the weights **are** what we would expect in that all are powers of two. Therefore, multiplication by the weighting factors can be, achieved by the shifting used in the first algorithm. The complexity comes in that now, instead of strictly adding, we need the ability to add, subtract, or do nothing. However, once a subtraction(addition) has been performed, the next operation will be an addition (subtraction). (This can be easily seen by examining possible bit patterns and the resulting order of operations.) This alternate nature of the operations guarantees that the size of the **adder/subtractor** will be limited to N bits. The easiest way to visualize this process is to work through an example:

Example 3.4: Signed multiplication with recoding: Utilize the Booth's algorithm recoding scheme to perform the multiplication: 25<sub>10</sub> x -19<sub>10</sub>. The bit patterns for the two numbers are:

> **011001** Let  $A = 25_{10}$  be the multiplicand. **101101** And  $B = -19_{10}$  be the multiplier.

The **recoding** algorithm works on pairs of bits a shown below. Note that the product is sequentially formed; the steps shown below to form  $P_0$  to  $P_4$  correspond to the cumulation of the **partial** products to that point.

```

\begin{array}{rcl} -1 \times (b_0 - 0) & = & -1 & \text{Subtract A from 0 to form } P_0. \\ -2 \times (b_1 - b_0) & = & +2 & \text{Add } 2 \times \text{A to } P_0 \text{ to form } P_1. \\ -4 \times (b_2 - b_1) & = & -4 & \text{Subtract 4 x A from P, to form } P_2. \\ -8 \times (b_3 - b_2) & = & 0 & P_3 = P_2. \\ -16 \times (b_4 - b_3) & = +16 & \text{Add } 16 \times \text{A to } P_3 \text{ to form } P_4. \\ -32 \times (b_5 - b_4) & = -32 & \text{Subtract 32 } \times \text{A from } P_4 \text{ to form } P_5. \end{array}

```

These steps can **be** followed as identified to ascertain that the answer is 475 as expected. The multiplication by powers of two called for here is achieved by the appropriate shift of the operand A. The hardware that would perform this kind of a multiplication can be visualized as shown in the following example.

*Example 3.5: Hardware for recoding multiplication:* Design the *data* path for a multiplier that will perform multiplication according to **Booth's** algorithm. Assume that the input values are 8 bits each.

One solution to the problem is shown in Figure 3.14. The multiplicand register and the product register are formed using '273s, which are 8-bit registers. The multiplier is loaded into a '165, which is a parallelinherial-out shift register. Note that, when the **nultiplier** is loaded, the

Figure 3.14. Multiplication by Booth's Algorithm.

flip-flop for storing the previous bit in sequence is cleared. The **add/subtract/do-nothing** requirement of the algorithm is handled by a pair of **'181s**, which are capable of performing all of the functions. The determination of the function of the '181s is handled by the arithmetic select lines (S3-SO), and the desired function is identified by the bits of the multiplier, as seen in the previous example. The appropriate bits are called simply **B0**-H and B1-H in the diagram. As the multiplier shifts through the register during the execution of the algorithm, the appropriate bits will appear on these lines. The function of the **'181s** should then be determined by the following table:

|   | r <b>B</b> its<br>BO-H | S3H |   | / Scl<br>\$1-Н | SO-H | Function                    |

|---|------------------------|-----|---|----------------|------|-----------------------------|

| 0 | 0                      | 0   | 0 | 0              | 0    | Pass product value.         |

| 0 | Ι                      | Ι   | 0 | 0              | Ι    | Product plus multiplicand.  |

| Ι | 0                      | 0   | 1 | 1              | 0    | Product minus multiplicand. |

| Ι | 1                      | 0   | 0 | 0              | 0    | Pass product value.         |

This logic is implemented in the few gates in Figure 3.14. **Like** the first **multiplication** method, this one will require a fixed number of clock pulses on the control lines to complete. Of course, it would **be** possible to check for a zero input condition, but it will not function properly if it is stopped in the middle of a multiply.

As can be seen from the example, the logic required for multiplication of negative as well as positive **numbers** does not greatly increase, but more care must be taken in the design and verification of the system. Nevertheless, the iterative approach will produce the proper result if enough caution is used in its implementation. Some of the many references for design techniques and examples of iterative methods of multiplication are listed at the end of this chapter. This is by no means intended to be an exhaustive explanation of multiplication methods, but rather it should identify some practical systems that can be used to perform the needed operations. For systems requiring more speed, then are faster methods for accomplishing the multiply, as we see in the next section.

# 3.4. Direct Multiplication Methods

All of the above methods require that the product be **formed** by combining the partial product with a value that will eventually form the final result. One of the reasons that an iterative approach is desirable from a resources standpoint is that it requires a single adder to perform the entire multiplication. The **tradeoff** has been made to sacrifice speed in favor of minimal logic resources. But in what way could more resources be applied to the problem? That is, given the situation where a designer is willing for purposes of speed to include a great number of gates, how should those gates be configured? We have already seen that, by examining the addition problem and using a different technique, the addition time could be changed from a linear function to a logarithmic function. Now we will analyze the multiplication function and identify methods that can be used to decrease the multiplication time.

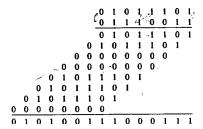

Consider the following multiplication:

| Multiplier $\rightarrow$   | 01101001         |

|----------------------------|------------------|

| Multiplicand $\rightarrow$ | 01011010         |

| $PP_0 \rightarrow$         | 00000000         |

| <b>PP</b> <sub>1</sub> -4  | 01101001         |

| $PP_2 \rightarrow$         | 00000000         |

| $PP_3 \rightarrow$         | 01101001         |

| $PP_4 \rightarrow$         | 01101001         |

| $PP_3 \rightarrow$         | 0000000          |

| $PP_6 \rightarrow$         | 01101001         |

| <b>PP</b> , -4             | 00000000         |

| Product $\rightarrow$      | 0010010011101010 |

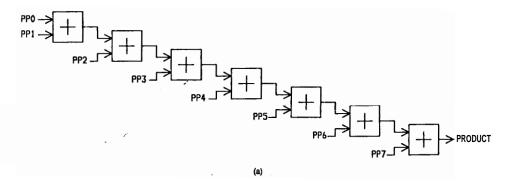

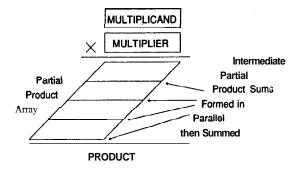

The multiplication process requires two separate functions: forming of the partial products and adding all of the partial products together. The formation of all the partial products ( $PP_7 - PP_0$ ) can be done in a single gate delay from the time **that** the data is stable. The hardware cost in the above example is 64 two-input AND gates, but, with that gate investment, the partial product **array** can be generated in parallel. Once the partial products are available, they can be **summed** as before. However, our objective here is speed, so rather than have a single adder and iterate to a register, let's use multiple adders and feed the result of one adder directly into another. The system resulting from this is shown in Figure 3.15(a), and it would require N-1 adders for N rows of partial products.

In the previous section,  $T_{MULT}$  was a function of a setup time and a multiple number of iteration times,  $T_{ITER}$ . The system shown in Figure 3.15(a) reduces the time by changing  $T_{ITER}$  to be simply the add time,  $T_{SUM}$ . The adders shown in the figure are **carry** look-ahead adders, but any kind could be used. The point here is that the time for a direct method with a linear connection of adders.  $T_{MULT_{DIRECTARN}}$ is given by:

# $T_{\text{MULT}_{\text{DIRECT-LIN}}} = (N-1) \times T_{\text{SUM}}$

The time is linear in the number of rows (bits), which is a situation that will only get worse for more bits. The obvious solution is to get a time reduction to a logarithmic function by arranging the adders in a tree fashion, such as that shown in Figure 3.15(b). This would change the time from a linear function to a logarithmic function:  $T_{MULT_{OBECT, REE}} = \lceil \log_2(N) \rceil \times T_{SUM}$  where there are N bits in the multiplier. This system will indeed obtain the product in a smaller time than the linear system, but other methods can achieve even higher speed.

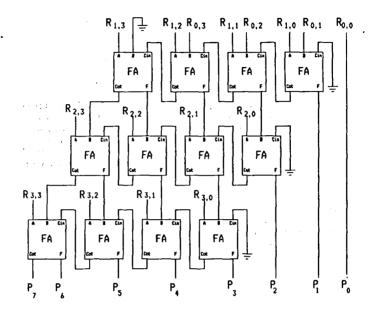

The next method to consider has received several names, but we will call it row reduction. To understand what is going on, let us **return** to a simple example, a 4x4-bit multiplication for positive values only. The problem setup is exactly as we have seen' it before, with the elements of the partial product array being formed as the AND of the appropriate bits. Here we want to emphasize the rows formed in the partial product array, so we will consider the multiplication by labeling elements in the partial product array as  $R_{X,Y}$ , where X gives the row number and Y is the element in the row. Thus, a **4-bit** multiplication becomes:

Each row of the partial product array forms a more significant portion of the final product. as seen by the shifting nature of the information. Now let's put together a set of full adders to do this multiplicationaccording to the above setup. That is, we will do a multiplication in the method of  $T_{DIRECT-LIN}$  above, but use full adders for this simple case. This is shown in Figure 3.16. As expected, the partial product bits ( $R_{X,Y}$ ) are added into the product by shifting them appropriately and

Figure 3.15. Multiplication by Direct Methods: Linear and Tree.

Figure 3.16. Partial Product Addition with Full Adders.

using full adders to add to the running sum. Now we ask the question, what is the function of the full adder? We often see a symbol for a full adder as shown:

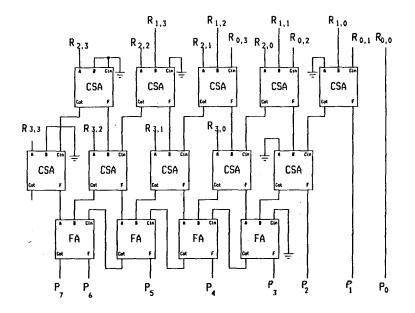

We mentioned earlier that the outputs form a 2-bit number that gives the number of one's on the input lines. The three inputs (A. B,  $C_{IN}$ ) all have the same significance; the sum output has the same significance, and the carry out has a significance of one higher bit position. There is no reason that the carry needs to be added into the sum in *the same row* that it is generated; that is, the carry can be saved for **the** next level of adders. The benefit of passing the **carry** to the next set of adders is that the work accomplished by the first stage no longer requires a time based on the number of bits in the word; the time is always two gate delays. The policy of saving the carry to the next stage gives rise to the name "**carry** save adder." or CSA. The multiplier of Figure 3.16 is redone to utilize this feature, and the result is shown **in** Figure 3.17.

Figure 3.17. Partial Product Addition with Carry Save Adders.

The use of carry save adders to speed up the addition process reduces the time required for the intermediate steps to two gate delays. but the carry process cannot be put off forever. The final stage of such a system must be an adder that implements the carry process the width of the final result. The effect is that the intermediate stages can be designed with a relaxed resource criteria, and more design effort can be directed toward speeding up the final stage. One way of looking at what is happening is to recognize that using adders as shown above (saving the carry to the next level of addition) reduces the number of rows that need to be added. The carry save adder, then, is a 3-row-to-2-row reduction unit: 3 rows of bits are reduced to an equivalent operation that requires only 2 rows. For example, in the first level of CSAs in Figure 3.17. 3 mws of bits fmm the partial product array  $(R_{0,x}, R_{1,x})$ , and  $R_{2,x}$  are reduced to 2 mws of bits. Then, the 2 rows of bits obtained by that process, plus the remaining row of bits from the partial product array  $(R_{3,x})$  are reduced to 2 rows of bits. Finally, these 2 mws form the input to a set of full adders, which does the final addition. Thus, Figure 3.17 shows an implementation of two 3-2 (3-row-to-2-row) reduction units and a final CPA stage.

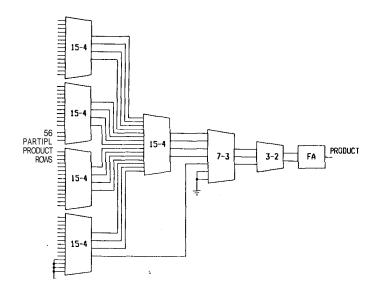

The output for any bit position of a row reduction unit contains a value that identifies the number of "ones" found in that bit position of a number of mws. Thus, a row reduction unit with k outputs will be able to represent numbers from zero to  $2^{k} - 1$ . Hence, a row reduction unit with k outputs will be able to reduce  $2^{k} - 1$  rows; therefore, **7-3**, 15-4, 31-5, and so on, are all possible configurations

however. that the complexity of the 15-4 reduction units will be much larger than the carry save adders, which form the **3-2** reduction stage. The final stage is a carry look-ahead adder that will produce the 112-bit result. We will assume that each row reduction unit requires only two gate delays. Thus, the time required for signals to propagate from the data inputs to the final addition stage is 9 gate delays (one for formation of partial products, two each for the four stages of row reduction units). From the equation for time required for carry look-ahead addition, the final addition process will require

$$T_{LACA} = 2 + 4 \times (\lceil \log_8(112) \rceil - 1)$$

= 2 + 4 × (3-1)

= 10 gate delays

So, the final result will require 19 gate delays. The cost of doing this is an enormous amount of hardware. This is not really practical in systems made of individual gates; however, this could be done in a reasonable fashion internal to an integrated circuit.

To better understand the multiplication mechanism, let us consider what is happening at each stage of the above process. The action being **performed** is to group portions of the partial product array together, and to then provide a number that is a count of the number of "1"s in the appropriate columns. This sectioning of the partial product array can be done in any manner that will produce the same results as the lengthy "normal" process. Thus, portions of the partial product array can be formed and summed, and then these intermediate sums combined to produce the final result. Any consistent mechanism can be used to identify portions of the multiply process for sectioning. The simplest example of this is the 3-2 reduction unit (CSA), which provides a count on the two output lines of the number of "1"s on the input lines. Other types of sectioning can be **performed** by using special purpose ICs, or by using similar techniques in multipliers that are intermal to processor chips.

An example of the concept of subdividing the partial product **array** into sections can be found in the **stepwise** creation of the final result by considering only portions of the original problem. That is, using special purpose integrated circuits, portions of the partial product array are formed (the **ANDing** is done inside the chips) and the resulting elements combined in the fashion described above. The output of these chips is a number that is a sum of parts of the partial product array. Conceptually, this is shown in Figure 3.19. The figure indicates that some of the bits of the partial product array are formed, and then summed in an initial step in the multiplication process. These partial sums are then combined together to produce the final result. Using these techniques, large multipliers can be built using multipliers that work only on portions of the input values, as shown by the following example.

*Example 3.7: Multiplication with sectioning:* Design *an* **8x8** multiplier. using 74284 and 74285 4x4-bit multipliers.

These devices jointly form the 8-bit product of two 4-bit numbers: the **'285** produces the four least significant bits; the '284 produces the four most

for row reduction units. One additional benefit of **row** reduction is the ability to do portions of the partial product addition in parallel. That is, since all of the partial products can be generated simultanwusly, the row reduction **process** can begin **immediately** to reduce the N rows of bits to 2 rows, which will then be added to form the final result. And independent **row** reduction units can operate on different rows of the partial product **array** simultaneously. This is demonstrated in the following example:

**Example 3.6:** Multiplication with row reduction: The DEC floating point number system has a double precision configuration with a mantissa length of 56 bits (including the hidden bit). Design a high speed multiplier to do a 56x56-bit multiply. Assume that the largest row reduction unit you have to work with is a 15-4 row reduction unit. Also assume that there is an adder at the last stage organized in **8-bit** units for carry generate and carry propagate. How long will the multiplication take?

The formation of the partial product results in 56 rows of bits that need to be added together. These **are** then fed into row reduction units to reduce the total number of **rows** from 56 to **2**. The overall design approach for this system, using **15-4**, **7-3**, and **3-2** reduction units, is shown in Figure **3.18**. As can be seen from the figure. this requires two stages of 15-4 mw reduction units, one stage of **7-3** row reduction, and a stage of **3-2** row reduction. These steps can all be accomplished in **8** gate delays. Note,

Figure 3.18. 56-Bit Multiplication Using Row Reduction.

Figure 3.19. Partial Product Reduction by Sectioning.

significant bits. Therefore, an 8x8 multiply will be able to effectively **use**. four pairs of devices. First, let's **look** at what one pair will produce:

So, the organization of an 8x8 multiply will be exemplified by the following configuration:

Note that the pattern established above is utilized four times, and that the various portions of the partial product overlap. So some type of an adder tree would be needed to do the summation of the partial products. This is accomplished with a carry save adder stage (**3-2** reduction) and an adder. The schematic for this is shown in Figure **3.20**. This works rather well, but doesn't handle large multiplications without a corresponding large number of chips. Texas **Instruments** is no longer making this part; however, this same method of building portions of the partial product **array** can be utilized using larger multipliers. For example, several manufacturers make a 16x16

multiplier (like **TDC1010)**, which could **be** cascaded in exactly this **fashion** to create a 32x32-bit multiply.

This example works on the basis of a "normal" partial product array; **the** respective portions of the array **are** generated internal to the multiplier chips, **ard** partial sums **formed**. **Then** these sums can **be** combined to form the **appropriate** result. This same type of organization, forming portions of the partial **product** array from multiplicand and multiplier bits, can also use the **recoding** ideas in — duced with Booth's algorithm. Indeed. the 74261 is a 2x4-bit multiplier that requires **three** bits of the multiplier in order to do the **recoding** necessary. But the system handles both positive and negative numbers, and the results are **correct** two's complement numbers. Like the system of Example 3.7, several sections **d** the parts can be combined to handle larger numbers.

All of these algorithms for high speed multiplies attempt to form the appropriate portions of the partial product **array** in parallel, then do as much of the partial product addition in parallel as possible. This includes delaying the find stage of the addition, where the carry will need to propagate all of the way **across** the output, as long as possible. Therefore, much of the design emphasis can be placed on this stage, which will be the speed bottleneck.

The multiplication process, then, adds into the final result the **appropriate** number of copies of the multiplicand. This can **be** accomplished by using a **single** adder and a register, and iterating through the necessary calculations. This type d system consumes considerable time resources (takes a relatively long time), **but** few hardware resources. One advantage to this approach is that it can be **easily** incorporated into a microprogrammed machine. Another multiplication method **s** to organize the calculation to use parallel application of partial product **generation** hardware. and then sum the final result with mw reduction elements and **high** speed adders. This design consumes little time, but requires many hardware **der**ices. The type of design selected will **be** dictated by the intended application. **and** the relative cost of system resources.

# 3.5. Direct Division: Basic Division Algorithm

Whereas multiplication finds the sum of multiple copies of an operand, division is concerned with finding out how many times one value can be found in **another** value. The numbers involved **are** the divisor,  $D_S$ , the dividend,  $D_D$ , the **quotient**, Q, and the remainder **R**. Mathematically, these elements **are** easily related to **ore** another:

# $D_D = Q \times D_S + R$

The division operation determines the quotient and the remainder. One of the assumed requirements on R is that it has a smaller magnitude than  $D_S$ . In the process of designing a system to do division, care must be taken to provide hardware that will do the work required by the system. That is, magnitudes should be considered, the number of bits to be provided in the operands, the bits required in the answers, and the placement of the radix point. All of this information must be considered in the design process.

One of the most straightforward methods to use in the approach to the design of the system is to mimic the operations of paper-and-pencil long division

for positive numbers. Consider, for example, the steps required for dividing 58 by 5:

| Divisor 8                  | 101                 | Quotient, Q<br>← dividend, D <sub>D</sub> |

|----------------------------|---------------------|-------------------------------------------|

| Divisor. $D_s \rightarrow$ | 101 ) 111010<br>101 | $Q_3 \times D_S$                          |

|                            | 10010               | R > D <sub>s</sub> , continue             |

|                            | 000                 | Q2 x D5, shifted                          |

|                            | 10010               | $R > D_s$ , continue                      |

|                            | 101                 | Q, x D <sub>s</sub> , shifted             |

|                            | 1000                | $R > D_{S}$ , continue                    |

|                            | 101                 | Q <sub>0</sub> x D <sub>s</sub> , shifted |

|                            | 11                  | $R < D_{\rm S},$ done                     |

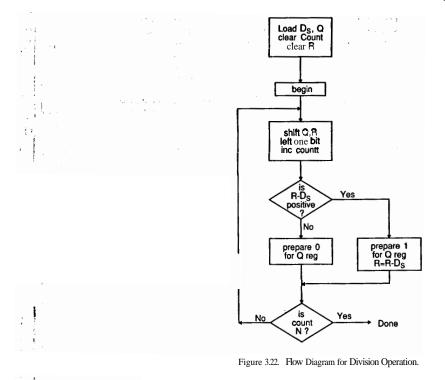

This operation proceeds in the same fashion as paper-and-pencil, long division. The base 10 algorithm with which we are familiar will produce a new base 10 digit at each iteration; the base 2 equivalent exemplified here will produce a new base 2 digit (bit) at each iteration. This is accomplished by subtracting the appropriate shifted divisor from the remainder value. The result of the subtraction determines the value of the bit in the quotient. A block diagram of such a divider is shown in Figure 3.21. The division process involves repetitive shifts and arithmetic operations, so the hardware is organized to accomplish that. The operation begins by placing the divisor in the register marked  $D_{S_1}$  the dividend in the Q register, clearing the R register. In each iteration another bit of the answer is created, and this bit is shifted into the Q register as the dividend is shifted into the R register to be used in the calculations. As seen in the above example, the most significant bits are used in the first comparisons, so the shifting is configured to do least-to-most significant shifts. And this is exactly what is needed for the final result, since the quotient is generated most significant bit first and shifted into Q one bit at a time. At the completion of the process, the remainder will be found in R, and the quotient will be in Q.

The basic algorithm for the direct divide is very simple. After the operands are in place, the division process begins by subtracting the divisor from the value in R, which is the accumulating remainder. If the subtraction would result in a positive number, that number is loaded back into the **R** register and conditions are set up to introduce a "1" into the Q register. Otherwise, the R register is not changed and a "0" is readied for the Q register. Then the Q and R registers are shifted left, and the process is continued. We make the observation that since we

NPUT

NPUT

control

Figure 3.21. Block Diagram for Basic Division.

are working with positive numbers in this system, the subtraction will not change the bits in the lesser significant places. This observation indicates why the results of the subtraction are loaded only into the R register, and do not affect the Q register. Thus, the only information loaded into the Q register, once the **process** has begun, are the individual bits as they are generated and shifted in.

A flow chart for the divide operation is given in Figure 3.22. As can be seen from the flow chart, two decisions need to be made in the execution of the operation. The first concerns the action at the R register: should the value available from the subtraction be loaded into the R register or not? This decision is made based on the results of the subtraction: if the result is a positive number, then it is loaded and a "1" is setup for loading into the Q register. **Otherwise,** the result is not loaded, and a "0" is readied for loading. Then a count is checked to see if we are done with the operation.

The algorithm shown in Figure 3.22 conditionally loads the results of the subtraction  $(R - D_D \rightarrow R)$  based on the value to be loaded. This is easily accomplished if the hardware is set up specifically to accomplish the divide. However, note that the hardware to do the direct multiply is very similar to that required for the divide. Hence, some systems are so configured that the **ALUs** and registers can be used for either function, and the **control** is slightly more complicated. In

Chap. 3: Arlthmetic Units: Data Manipulation

104

such a system. it may be that the subtraction result must be stored (ALU out  $\rightarrow R$ ) in order to set bits to be tested by **microcode**, or some other control mechanism. The algorithm shown in Figure 3.22 must then be changed accordingly. The net effect is that as well as setting up to put a "0" in Q, the value which was subtracted out must be restored, requiring another addition operation. This kind of an algorithm is called a restoring algorithm; another algorithm, called the **nonrestor**ing divide, is so configured that the value is not restored, but set up to contribute the appropriate value for the next iteration of the process. The net result is fewer overall ALU operations.

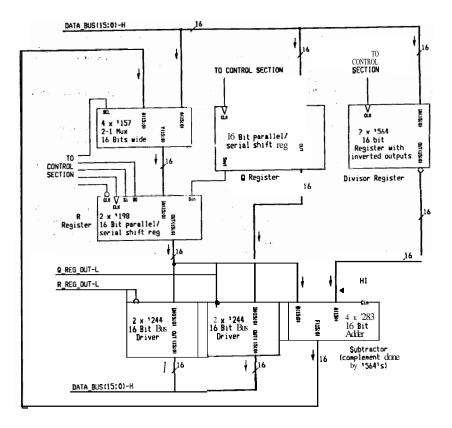

**Example 3.8: Hardware system for direct division:** Design a set of hardware that will accept data from a bus and perform a 16-bit division using the operations identified by the flow chart of Figure 3.22.