# Instruction Set Processing

Thus far we have been dealing with the blocks **from** which computers are built. Chapter 2 described some of the decisions involved with choosing a method for representing the information within the computer. Chapter 3 is a discussion of the issues involved in doing some of the arithmetic operations required of a machine. In both cases, tradeoffs must be made to assure that the system resources are utilized in an efficacious manner. Representation ranges of number systems must be effectively weighed against the cost of those representations, and the targeted applications of the machine. Similarly, the methods used for doing the arithmetic must be balanced in such a way that the speed and complexity match the intended uses of the system.

In this chapter, we will look at how the arithmetic building blocks can be combined with other functional units, such as registers and memories, to create computing systems. Here we seek to address some of the basic questions concerning data manipulation methods. What are some of the issues involved in choosing an instruction set? What basic operations should be included? How do we specify the operations to be performed, and identify the operands to be used in that operation? What are the steps required to accomplish the specified work? What are the costs associated with the specification and execution of these instructions?

Let us first look at some of the basic tools used to describe machine structure and **data** manipulation methods. The tools are very simple: diagrams to identify **structure** and a register transfer language to specify data movement within that **structure**. Then we will identify some of the methods utilized by different machines to accomplish their work. Often what is considered "good" depends on several factors, and good design practices using one set of constraints will not be considered good design practices using a different set of constraints. Like the other ideas explored in the previous chapters, engineering choices are made after a careful examination of the alternative methods of doing the work. The key is to choose appropriate metrics or measurement **methods** and to apply the metrics uniformly to the various alternatives.

The first area of interest concerns the data manipulation instructions and related topics: single address machines, two address machines, operand specification methods, and so on. Then we will look at program flow instructions: jumps, branches, subroutine calls, and the like. In a related area we will look at the machine reactions when exception conditions occur: interrupts and traps. This will necessitate some discussion of I/O programming methods as well. Finally, we will identify some of the issues in the ongoing RISC/CISC dehate, and explore reasons that the two methods are alternately considered good and bad.

#### 4.1. Basic Building Blocks for Instruction Specification

As the computers space expands, the distinction between the responsibilities of the individual pans becomes more and more blurred. So, we will begin by looking at some of the concepts utilized in the early machines, and then as the operations and methods become more complex, we can recognize the parentage of the ideas, and see possible applications and design methods.

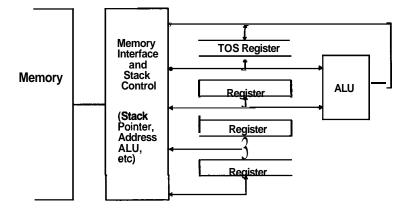

The building blocks used by the earliest machines comprised a very small set: registers, **ALUs**, memory. and data paths. In this discussion we will assume that the ALU model is as shown at the beginning of Chapter 3: two different inputs and an output. The ALU is assumed to be as wide as the machine; the word width is a decision based on what needs to be represented. We will assume that the ALU is capable of all of the arithmetic and logic operations **which** are required by the instructions.

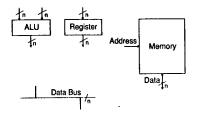

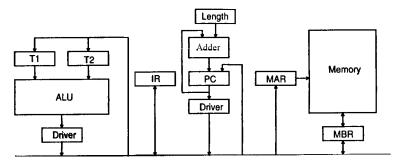

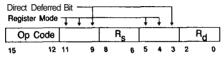

Figure 4.1 shows the basic building blocks we will use in consideration of machine operation. The ALU we have already mentioned; it is used for data manipulation. Missing from the diagram are some very necessary lines, and in that sense the representation is incomplete. The missing lines include the control lines, which specify the action of the ALU (add, subtract, AND, etc.) and the data lines that do not form part of the designated inputs and output. These additional data lines often connect directly to a status register and include such things as the **carry** (in and out), the sign bit, **overflow** bit, and the like. Thus, for operations needing this additional interaction, we will assume that the connections do indeed exist and that the bits are transferred appropriately.

Figure 4.1. Basic Building Blocks for Instruction Set Processing: ALU, Register. Memory, and Communication Paths.

The data to be manipulated by an ALU is first stored in a memory, and such an element is shown in the figure. For our purposes we will say that the memory is as wide as the data path, but we will see later how this may **be**, altered as part of the machine design. Our model for the memory element is simply that there are *M* memory locations, and these **are** arranged in such a way that they can **be** accessed by an address supplied on  $\lceil \log_2(M) \rceil$  address lines. The data path allows reading and writing of data in these locations. As with the ALU, some lines are missing from the memory block as shown in Figure 4.1. These lines are the control lines used to cause the actual write or read of data from the memory devices. These lines **are** system-specific, and we will assume that the designer is aware of the required lines and handles them in an appropriate fashion.

Much of our current practice of memory system design and utilization is the result of the ideas explored by Von Neumann and his colleagues in the late 1940s [BuGo46]. Some of the earliest memory systems were organized such that the instructions could be held in one memory, and the data in another, and that these two memories were disjoint in function and fabrication. However, Von Neumann observed that the memories organized in that manner were not always effectively used; some tasks would leave the data **memory** practically empty while crowding the program memory, or vice versa. So he reasoned that since both instructions and data were basically information, both could be stored in the same memory space. Organizing the memory system in this manner brought a number of benefits, since programs could be treated as data. Instructions could be selectively altered to allow different functions or addresses as required, or data values could act as instructions if the conditions permitted. By organizing the memory in this fashion, only one memory element was needed, with its associated addressing and data retrieval capabilities. The two types of information, data and instructions, were combined into the same memory. The principal drawback to the arrangement was that interaction with the memory element was now needed for both types of information, and hence the path between computational functions and storage functions became a primary impediment to the effective processing speed. This has become known as the Von Neumann bottleneck, and we will present some of the suggestions made to minimize its effect. However, we will still treat memory as a linear array of storage locations, accessed by an appropriate address.

Another element shown in the figure is the data path. The width of the data path is assumed to be the same as the machine, but, as with most generalizations, exceptions can be found. We will use that width as a natural value, and later we will discuss ways to use widths other than the basic machine width for transferring information. These interconnections can be **point-to-point** wires from one element to another (containing the appropriate number of individual wires), or they can be buses, which are capable of **transferring** information between several distinct elements. Direct connections allow for high speed, but have low versatility. With tri-state logic readily available, a number of alternative busing arrangements can be made. We will discuss various types of buses in Chapter 6.

The final element shown in Figure 4.1 is the register. For our purposes, this is an element that is as wide as needed to match the buses, memories, and **ALUs**, used for storing information. This is another basic device that needs additional control lines not included in the figure. A register will require a clock line identifying when data is stable on the input line, and the register should load that data into its collection of storage elements. Other control lines may also be needed, such as output control lines for tri-state devices, or **shift/load** control lines for multifunction registers. Again, we will assume that the designer of the system is

aware of the capabilities of the registers being used, and that appropriate control lines are included in the machine.

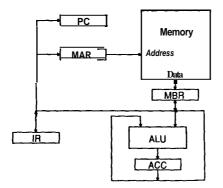

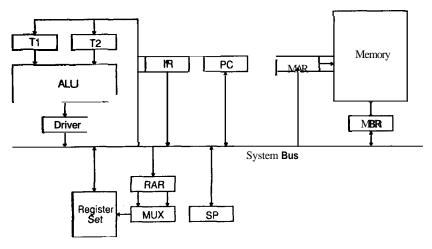

Registers are used for a variety of applications, and generally receive names that denote their function. Figure 4.2 shows a block diagram that will serve as a vehicle for describing how the various registers and other elements function together to accomplish work. By work we mean the information transfers required to do some task. The registers shown in the figure form a fairly minimal set:

- *Memory Address Register (MAR).* This collection of storage elements bas the responsibility of identifying the memory location of the information to **be** transferred. The transfer could be either into or out of memory.

- Memory Buffer Register (MBR). The memory buffer register is used to store information moved into and out of memory. With destructive readout devices, such as core memory, it is a requirement; reading the value of a memory location destroys the contents of that location, and to preserve what was there it must be written back. The value to be restored is obtained from the MBR as the value is being used by the other parts of the circuit. With most semiconductor memories, the storage of the data going into and out of the memory is not required, and this register is optional, and used only in systems where there is a specific requirement to maintain the data after it is read.

- Program Counter (PC). The program counter is used to identify the location of the instruction to execute next. For machines that store one instruction per memory location, this register will increment by 1 during the execution of an instruction, which is why it has become known as a program "counter." Other organizations will have differing requirements for updating the PC value. For now, we will assume that the program counter will increment as needed to specify the next value needed from the instruction stream.

- Instruction Register (IR). The instruction register is used to store the instruction currently being executed. This allows the control portion of the machine to assert the control lines of the registers, memories, and arithmetic elements in an appropriate manner to cause the action needed. The design of the control section will be the subject of the next chapter. The IR may only be as wide as

Figure 4.2. Block Diagram of Simple Machine.

needed to store the operation code of the instruction, or it may be wide enough to keep a temporary copy of all of the information associated with an instruction.

• *Accumulator* (ACC). The accumulator is shown here as the receptacle of the action of all of the data manipulation instructions. In the next section we will discuss the implications of the use of an accumulator for doing arithmetic.

This collection of resources (registers, **ALUs**, memory, and data paths) provides a sketchy view of the system, but it is sufficient to represent transactions that occur within the machine. We also need some method of describing those transactions. To do useful work we will need to specify the work to be done, and this work will be directed by the control section. The user of a computer system has a view of what the capabilities of the computer system are, and this view results directly from the instructions that the machine can execute. This view of the machine, or the appearance of the machine as seen by the assembly language programmer, is sometimes called the instruction set architecture of the system. By the use of the instructions included in this set, the user specifies the action which should occur on the data.

This work of an instruction is accomplished by a fetch-decode-execute mechanism: the instruction is fetched from memory and placed in a register specifically designated for that purpose (the **IR**), the required decoding is performed, and then the data transfers required by that instruction are executed. At the completion of this action, the machine starts over again, requesting another instruction, decoding it, and performing the needed action. The process continues until the machine has completed all of the designated instructions.

The action of an instruction can be described by identifying the data transfers needed to do the requested work. The specification of this work is done by a register transfer language (RTL); the transfers occur along the permissible data paths in the machine from one major component to another. Only transfers that can actually occur, given an accurate block diagram of the system, are permissible components of the specification for an instruction. For example, transfers from the PC or MAR to the MBR of the system shown in Figure 4.2 would not be possible, since the data paths between those elements do not permit data transfer in that direction. Thus, RTL descriptions specify the order of register transfers and arithmetic action required to carry out the work of an instruction. This information can then be utilized by the designer of the control system to identify the order of activation of control lines to actually cause the desired transfers. This points out one of the basic divisions of the computer design process: the data path (with its appropriate arithmetic capabilities) is specified. and then in a quite separate process the control section for the data path is designed. The design of the data path section is done in such a way that data manipulation goals are met. The design of the control section is then carried out so that the timing requirements of the system are met.

A register transfer language can become as simple or as complex as needed to specify the transfers required in the system. Since we will be using an RTL to describe the action of systems in this chapter and in the remainder of the book, we will describe the few primitives which will follow. The basic operation is the transfer of the contents of one register to another:

$PC \rightarrow MAR$

specifies that the contents of the program counter are transferred to the memory address register. If the data paths of the system are rich enough to allow multiple operations in the same time period, these can be represented by specifically linking the transfers together:

$$\stackrel{PC+1}{_{MBR}} \overrightarrow{L}_{IR}^{PC}$$

identifies that in the same time period the value of the program counter is **incre**mented and the contents of the **MBR** are transferred to the IR. **Normally**, all of the information is involved in the transfer. However, if a subset of the information is to be transferred, then the specific bits are identified by the use of pointed brackets:

specifies that bits 3 to 0 of the instruction register are directed to the ALU. Similarly, locations of memory or a set of registers are specified with square brackets:

# $REG[2] \rightarrow MEM[MAR]$

indicates that the contents of register 2 in a general register set **(REG)** is transferred to the location in memory identified by the memory address register. Finally, for operations that are conditional in nature, we include an "if' facility patterned after the C language if construct:

if (carry == 1)

$$PC - 24 \rightarrow PC$$

else  $PC + 1 \rightarrow PC$

identifies that if the **carry** is equal to 1, the program counter is adjusted by a factor of -24; otherwise the program counter is incremented.

Using the above constructs, a wide variety of instructions can be specified. For example, consider the following add instruction:

fetch: These register transfers get the instruction. Instruction location to MAR. PC  $\rightarrow$  MAR Put instruction in MBR.  $M[MAR] \rightarrow MBR$  $MBR \rightarrow IR$ And then put it in the IR. Bump the program counter to next instruction.  $PC + Ilen \rightarrow PC$ decode The decode process identifies the instruction. execute: and the execute portion performs the needed work.  $IR < adr > \rightarrow MAR$ Address of operand to MAR.  $M[MAR] \rightarrow MBR$ This is value to add to ACC. ACC + MBR → ACC Do the actual work of instruction.

At this point we will pause to consider briefly some of the timing considerations. All of the operations identified by the RTL require some finite time to accomplish. Exactly how much time is required depends on the technology of implementation and the electrical characteristics of t's system. A simple register transfer in a **tri-state** bus system requires time for the source register to be enabled, **time** for the data **to** become stable on the bus, and a setup time and a hold time for the data at the destination register. These times become very important to the designer of the control system, as all of the appropriate timing requirements must be met. In this chapter, we will assign times for the operations specified by the **RTL** for some of the instructions. These times, when added together. identify the total time required for the execution of the instruction. The times required for operations specified in **RTL** statements will be identified by a number in parentheses with the statement, and that number represents the execution time in nanoseconds.

By identifying the times required for the actions specified by the **RTL** statements, time can be used as a metric for the comparisons that need to be made in system evaluations. The overall instruction rate is then the inverse of the average instruction time. It is possible to increase the instruction rate (decrease the instruction time) by increasing the complexity of the system. For example, concurrent register transfers can be possible if multiple data paths exist within the system. Note, however, that the increased complexity may also result in longer machine cycle times, and this must be considered in the process of creating a system. As before, the tradeoffs involving complexity and speed must be made by the system architect using reasonable engineering judgements based on metrics that **demonstrate** the effective use of system resources.

Another piece of information used in the **RTL** descriptions included here is a statement number, which allows identification the steps of an instruction. This identification is often needed in the description of the process.

With the ability to represent the machines at the register level, the data paths connecting the registers and the transfers of data between the major components, let us examine some of the methods used to organize machines and perform useful work.

## 4.2. Single Address Machines

The first machines constructed made very judicious use of registers since registers required a nontrivial amount of system resources. One of the registers was designated as the one that would be utilized in arithmetic and logic operations; others were also involved as needed. The register involved in these operations was most often called the accumulator, as we have indicated in Figure **4.2**. This same technique has been used in many different machines, and provides insight when compared to techniques more prevalent in newer architectures.

On machines that operate in this manner, operations requiring only one operand, such as complement, increment, clear, and the like, find the operand in the accumulator. And the result remains in the accumulator. Functions requiring two operands also use the value in the accumulator as one of the operands. The other operand is identified by a single address in the instruction; hence the name single address machine. To demonstrate how these machines might perform each kind of instruction. let us use the block diagram shown in Figure **4.2** and identify the transfers needed for a negate instruction and a subtract instruction. We are assuming that the machine in question uses the two's complement number system, s o forming the negative of a given value can be accomplished by complementing and incrementing. The following **RTL** description implements the negate instruction:

|   | fetch:                                   |                                               |

|---|------------------------------------------|-----------------------------------------------|

| 1 | $PC \rightarrow MAR$                     | Instruction location to MAR.                  |

| 2 | M[MAR] → MBR                             | Put instruction in MBR.                       |

| 3 | $MBR \rightarrow IR$                     | And then put it in the IR.                    |

| 4 | <b>PC</b> + Ilen $\rightarrow$ <b>PC</b> | Bump the program counter to next instruction. |

|   | decode                                   |                                               |

|   | execute:                                 |                                               |

| 5 | $\overline{ACC} \rightarrow ACC$         | Complement value in ACC.                      |

| 6 | $ACC+1 \rightarrow ACC$                  | And then increment it.                        |

All instructions start as does this one, with the fetch cycle. The address **from** the program counter, which identifies the location of the next instruction to execute, is placed in the memory address register (step 1). The value **pointed** to by this address is fetched from memory (step 2), and placed in the instruction register (step 3). The machine then readjusts the program counter to point to the next instruction (step 4). To correctly do this, the machine must be aware of the length of the instruction. That is, it is possible that machines have instructions of different length, and when the program counter is adjusted to identify the next instruction, the amount of that adjustment (Ilen) is information which is associated with the **instruction**. For example, the 68020 has instructions ranging in length from 2 to **14** bytes.

The actual work of the instruction is accomplished by steps 5 and 6 above: the value in the accumulator register is fed to the **arithmetic/logic** unit, **where** it is first complemented and that result is then incremented. In general, the exact steps utilized to do the work of an instruction depend on the capabilities of the ALU in the system. (Alternatively, the capabilities of the ALU can be based on the requirements of the instruction set.) Usually two iterations through the unit will not be needed. However, this is a good example of some of the possible methods that can be used to accomplish work: the system resources are used as required to complete the tasks of an instruction. These transfers are coordinated by the control unit in agreement with the technology demands of the system.

The subtract instruction requires two operands. One question is the order of operands: which should be the subtracted value? We will assume that the instruction SUB X means, subtract the value stored in the location X from the value currently in the accumulator and store the result in the accumulator. We will further assume that the address X is adequately contained in the instruction itself, so no additional information beyond the instruction will be **required**. With those assumptions, a set of data transfers that will perform the work of the subtract instruction follows:

|   | fetch:                      |                                               |

|---|-----------------------------|-----------------------------------------------|

| 1 | $PC \rightarrow MAR$        | Instruction location to MAR.                  |

| 2 | $M[MAR] \rightarrow MBR$    | Put instruction in MBR.                       |

| 3 | $MBR \rightarrow IR$        | And then put it in the IR.                    |

| 4 | PC + Ilen $\rightarrow$ PC  | Bump the program counter to next instruction. |

|   | decode                      |                                               |

|   | execute:                    |                                               |

| 5 | $X \rightarrow MAR$         | Put address X in the MAR.                     |

| 6 | $M[MAR] \rightarrow MBR$    | Value at memory address X to MBR.             |

| 7 | ACC – MBR $\rightarrow$ ACC | Subtract it from value currently in ACC.      |

The fetch cycle of this instruction is identical to the other fetch cycles: get the instruction and bring it into the instruction register, then bump the program

counter. The real work begins in step 5, where the address of the operand is transferred to the MAR. The intended operand of the instruction, the value stored at location X, is then transferred (step 6) to the memory buffer register. Since the address is contained in the instruction, the value of X needed for step 5 can come from either the instruction register or the MBR. Finally, the value is subtracted (step 7) from the value currently in the accumulator, and the result left there. This mechanism for doing the subtraction assumes a more capable ALU than did the negate instruction above. If the ALU needed to form the negative of the value in the MBR by a complement and increment fashion, then additional operand storage facilities would be required.

A number of variations of this method have been made, while the machines have remained basically single address machines. The IAS, Von Neumann's machine built in 1946-7, utilized a word length of 40 bits. The word length was capable of storing more information than required for a single instruction and a single address, so two 20-bit instructions were placed in a single 40-bit word. Each instruction was composed of an 8-bit op code and a 12-bit address; up to 256 operations could be specified, and, if needed, the single address could identify one of 4,096 data locations. But although each word of storage was capable of handling two addresses, the instruction format was limited to a single address machine of IAS was not restrictive since the total addressable memory was only 4,096 words. However, this limit is generally not acceptable, so different mechanisms have been implemented to extend the permissible range of the operands.

One of the mechanisms utilized for storing addresses needed to identify the location of operands is to place them directly after the operation code (op code) that identifies the work to be done. This method has several advantages that make it an attractive alternative. If there is no need for an address (such as the negate instruction above), then no **room** is taken up in the instruction itself for a value (address), which will not be used. If multiple length addresses are permitted, that is, addresses of 1, 2, or more bytes depending on addressing mechanism, then only the requisite number of bytes after the op code are utilized to identify the address. And after the fetch portion of the instruction the program counter identifies the location of the address itself. An **RTL** implementation of this type of subtract instruction is shown in Figure 4.3. Notice the change that results if the assumption is made that the operand address is located in the instruction **strcam** directly following the bits specifying the instruction.

The **RTL** included in Figure 4.3 indicates that the program counter is used twice, once for the address of the instruction to be executed, and once for the address of the operand. In the first instance, it was incremented by the length of the instruction; in the second, it was incremented by the length of the address. We **are** making the assumption here that the decoding of the **instruction/address** identified the appropriate lengths and treated the program counter appropriately. By separating the op code fetch from the address fetch in this manner, the number of bits needed to specify the operation is allowed to expand to meet the appropriate requirements.

*Example 4.1: RTL and timing calculations for ADD:* How much time is required to execute an ADD instruction for a machine organized as demonstrated above?

The time required for execution of the instruction will include the time necessary to obtain the instruction from memory, decode it, and **exe**-

|    | fetch:    |               |     |                                                                               |

|----|-----------|---------------|-----|-------------------------------------------------------------------------------|

| 1  | PC        | $\rightarrow$ | MAR | Instruction location to MAR.                                                  |

| 2  | M[MAR]    | $\rightarrow$ | MBR | Put instruction in MBR.                                                       |

| 3  | MBR       | $\rightarrow$ | IR  | And then put it in the <b>IR</b> .                                            |

| 4  | PC + Ilen | $\rightarrow$ | PC  | Bump the program counter to next value                                        |

|    |           |               |     | the PC will then point to memory location holding the address of the operand. |

|    | decode    |               |     |                                                                               |

|    | execute:  |               |     |                                                                               |

| 5  | PC        | $\rightarrow$ | MAR | PC is needed again.                                                           |

| 6  | M[MAR]    | $\rightarrow$ | MBR | Address at this location to MBR.                                              |

| 7  | MBR       | $\rightarrow$ | MAR | This is address of operand.                                                   |

| 8  | M[MAR]    | $\rightarrow$ | MBR | And this is operand.                                                          |

| 9  | PC + Alen | $\rightarrow$ | PC  | Now bump PC by length of address.                                             |

| 10 | ACC - MBR | $\rightarrow$ | ACC | Subtract it from value currently in <b>ACC</b> .                              |

Figure 43. **RTL** Implementation of a Subtract Instruction for a Single Address Machine.

cute the necessary steps. To determine the time required for instruction execution, we must first develop an appropriate RTL implementation of the operations. One such implementation is shown in Figure **4.4**.

Each of the items involved in Figure 4.4 will take time to accomplish, and the time for the operation will be implementation dependent. We will assume for the purposes of this example that the accesses to memory **cost** 300 nsec, the access to a register cost 50 nsec, and that the add itself can be done in 100 nsec, not including the register time. The amount of time for each of the operations identified above is given in the RTL itself. Note thal we have assumed that the bumping of the PC can be done in the **time** it takes to load the register. Also note that step 10 accounts for both the add time and the register delay time. With these figures, we can see that the **total** time is 1.1 µsec. The instruction fetch itself requires 450 nsec, which is **almost** half of the total time. If we look only at the time metric, we can draw some conclusions concerning the efficient use of time to accomplish

|    | fetch:                      |        |                                      |

|----|-----------------------------|--------|--------------------------------------|

| 1  | $PC \rightarrow MAR$        | (50)   | Start by loading MAR.                |

| 2  | $M[MAR] \rightarrow MBR$    | (300)  | And get instruction                  |

| 3  | $MBR \rightarrow IR$        | (50)   | into the IR.                         |

| 4  | $PC + Ilen \rightarrow PC$  | (50)   | Bump the program counter.            |

|    |                             |        | PC now points to address of operand. |

|    | decode                      |        |                                      |

|    | execute:                    |        |                                      |

| 5  | $PC \rightarrow MAR$        | (50)   | PC is needed again.                  |

| 6  | M[MAR] → MBR                | (300)  | This is really address of operand.   |

| 7  | MBR → MAR                   | (50)   | So put in MAR.                       |

| 8  | $M[MAR] \rightarrow MBR$    | (50)   | And get operand to MBR.              |

| 9  | $PC + Alen \rightarrow PC$  | (50)   | Now bump PC by length of address.    |

| 10 | $ACC + MBR \rightarrow ACC$ | (150)  | ADD value in MBR to value in ACC.    |

|    |                             | (1100) |                                      |

Figure 44. RTL Implementation and Timing Considerations an ADD Instruction.

the work of the system. If we now ask how many bits are required, and what are the costs involved in storing and moving data, a different type of conclusion may **be** available. However, this demonstrates that the fetch of an instruction from memory is definitely not free. It also demonstrates one of the mechanisms that can be used to obtain information about the execution time for **instructions**.

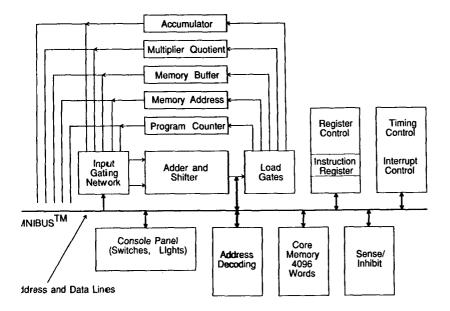

One of the single address machines built in the mid-1960s that enjoyed wide popularity was the **PDP** 8, made by Digital Equipment Corporation. This was a 12-bit machine, a block diagram of which is shown in Figure 4.5.

The instruction format called for a 3-bit op code, which left 9 bits of the 12-bit instruction for the address. With 3 bits for specifying the action of the instruction, the possible operations were limited to 8, and these 8 were chosen with care. One of them was an ADD instruction, which added to the accumulator the value identified by the single address included in the instruction. The 9 bits of address specification in the instruction limited the number of addressable operands, so different operand specification mechanisms, such as indirect addressing, were used to increase the number of accessible values. We will discuss alternative addressing methods in Section 4.4. The instructions that required an address for operand identification, such as **DCA** (deposit value currently located in the ACC to the memory location identified and clear accumulator). TAD (two's complement add), and ISZ (increment and skip if zero), used the 9 address bits to specify the location of the operand. Instructions that did not require an address, such as CLA (clear accumulator), INA (increment accumulator), and CLE (complement accumulator), expanded on one of the eight available op codes to specify the action to take place.

Figure 4.5. Block diagram of the PDP 8 Computer.

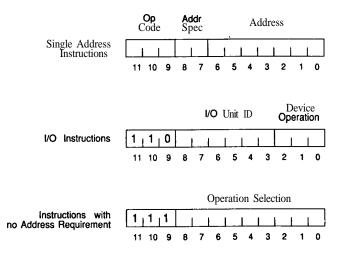

The format of the PDP 8 instruction set is given in Figure 4.6. At the time of the creation of the system, memory was a very expensive system resource, and hence the word length was limited to 12 bits. As the relative costs of memory and other system components change and diminish, uses of those system resources will also be appropriately change. The designers of the PDP 8 system, with a limited number of bits to work with, chose the operations of the system with care. A 3-bit op code limited the number of instruction patterns to 8. Six of the possible instructions required an address, and this address was determined by the 9 LSBs of the instruction. These six instructions were logical AND, add, increment-and-skip-if-zero, deposit-and-clear-accumulator, subroutine jump, and unconditional jump. Another of the eight patterns identified an UO instruction, and the remaining 9 bits specified one of 64 I/O devices, and one of eight operations. The operations were defined by the design of the UO device itself. The final pattern identified instructions that needed no address, and hence could all share a common instruction code in the op code bits. This allowed a number of operations to be specified, such as clear the accumulator, or increment the accumulator, and so on. One of the most challenging tasks facing a computer architect is to identify the instructions to be incorporated into a new machine, and then encode the specification of those instructions in a format acceptable for the new system. We will examine some more examples of instruction formats later in this chapter, each of which demonstrates a different view of the optimal utilization of system resources.

All of the above examples have a common operational mode: the instruction **stream** provides a single address, and this address is utilized to identify the **loca-tion** of an operand. For data operations, that operand is used in conjunction with whatever is needed in an assumed location (the accumulator), and the result is left in a predefined place, usually the accumulator. With this type of a machine all of the operations needed by a system can be performed, but the result may not be as efficient as desired. With the fetch utilizing a large fraction of the instruction time, one approach would be to try to utilize more effectively the information fetched from memory. One method proposed for this is to make the system more

Figure 4.6. Instruction Formats for the PDP 8 Computer.

efficient by using more than one address in a single instruction to specify a greater variety of operations and operands.

#### 4.3. Multiple Address Instructions

Multiple address instruction formats **carry** with them both benefits and added specification requirements. With a single instruction more operations **art** identified, so fewer instructions are required to implement a string of arithmetic. At the same time, the instructions must identify all of the work to do, since no assumptions will be made concerning the location of the data. Thus, multiple address instructions will identify both source and destination of the information. The myriad possibilities are exemplified by the following formats:

| ADD2 | A,B   |

|------|-------|

| ADD3 | A,B,C |

Although the system architect can choose any reasonable specification mechanism. the assumption we will make concerning the syntax of these **instructions** is that the final address specified is the destination of the function. With this assumption, the **ADD2** instruction adds the value in the location identified with the **A** address to the value in the location identified by the B address, and the result is returned to the location specified by the B address. Thus, this instruction changes the value identified by the B address. The **ADD3** instruction obtains the operand identified by address A. adds to it the value stored at the location specified by address B, and places the result at the location identified by address C. In a machine that utilizes this type of capability. the op codes must differentiate between the various types of operations.

That is. a separate code must be available for each instruction; ADD2 and ADD3 will be specified by different patterns. This results in a larger operation code field, since many different codes must be representable. And it also results in different length instructions. since some instructions will require three addresses, while others will require only two. Consider the following example, in which we compare two and three address add instructions.

**Example 4.2:** Two ond three address instructions: Compare the operation of the ADD2 and ADD3 instructions, using the times identified in Example 4.1. Assume that the operation codes require the same number of bits to represent as the addresses. (Is this a valid assumption?) What is the execution time required for each of the instructions?

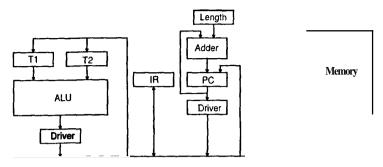

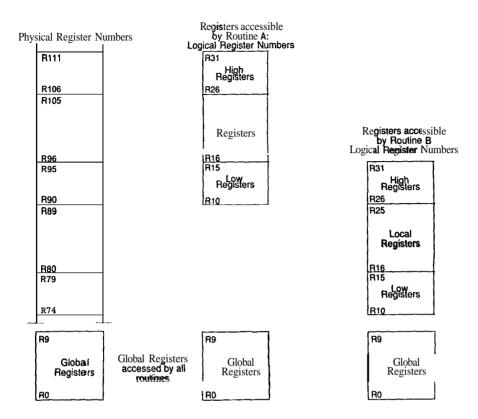

In order to address these questions, we need to identify some of the details of the system. That is, before the RTL of **implementation** can **be determined**, we need to understand what mechanisms are being utilized. Let us assume that the **first** value obtained from memory at the location identified by the PC is the appropriate op code, and that the next values are the respective addresses. This is somewhat simplistic, as we shall see a little later. But it will help to identify some of the underlying issues. The next problem to **be** dealt **with** needs a little more detailed consideration. This consideration is the mechanism for the addition: how is it to be carried out. In order to visualize the transfers necessary and the order of events, we need to know the available registers and their interconnection. **The** basic elements required for this example are given in Figure 4.7. The figure has

Figure 4.7. Block Diagram of System for Example 4.2.

two registers, TI and T2, which are not pan of the instruction set architecture. That is, the system as defined by the instruction set does not include these storage elements. However, they are very useful when doing instructions that require holding information to be utilized by the system. Armed with this knowledge about the underlying **structure**, let us examine RTL representations of the instructions.

The **RTL** statements describing one implementation of the two address ADD instruction is found in Figure 4.8. The figure also contains timing information with the RTL statements, indicating the time required to complete the task.

The RTL for the three address case is included in Figure 4.9. Note the similarity with the two address version in the initial stages of the instruction

|    | fetch:    |               |        |        |                                           |

|----|-----------|---------------|--------|--------|-------------------------------------------|

| Ι  | PC        | <b>→</b>      | MAR    | (50)   | Address of instruction to MAR.            |

| 2  | M[MAR]    | $\rightarrow$ | MBR    | (300)  | Instruction to MBR.                       |

| 3  | PC + Ilen | $\rightarrow$ | PC     | (50)   | Bump the PC to point at address.          |

| 4  | MBR       | →             | IR     | (50)   | Instruction finally to IR.                |

|    | decode    |               |        |        |                                           |

|    | execute:  |               |        |        |                                           |

| 5  | PC        | →             | MAR    | (50)   | Go get address of operand.                |

| 6  | PC + Alen | $\rightarrow$ | PC     | (50)   | Bump PC to point at next address.         |

| 7  | M[MAR]    | $\rightarrow$ | MBR    | (300)  | This is address of first operand.         |

| 8  | MBR       | →             | MAR    | (50)   | So put in MAR.                            |

| 9  | M[MAR]    | $\rightarrow$ | MBR    | (300)  | And get the value there. first to MBR.    |

| 10 | MBR       | →             | TI     | (50)   | And then to TI.                           |

| 11 | PC        | →             | MAR    | (50)   | This is to get address of second operand. |

| 12 | PC + Alen | $\rightarrow$ | PC     | (50)   | Bump PC to next instruction.              |

| 13 | M[MAR]    | $\rightarrow$ | MBR    | (300)  | Address of second operand to MBR.         |

| 14 | MBR       | →             | MAR    | (50)   | And then to MAR.                          |

| 15 | M[MAR]    | →             | MBR    | (300)  | The second operand goes to MBR.           |

| 16 | MBR       | →             | T2     | (50)   | And then to T2.                           |

| 17 | TI + T2   | →             | MBR    | (150)  | Do the add. results to MBR.               |

| 18 | MBR       | -             | M[MAR] | (300)  | Put results where operand two used to be. |

|    |           |               |        | (2500) | Total time: 2.5 µsec                      |

Figure 4.8. RTL Implementation of a Two Address ADD Instruction.

efficient by using more than one address in a single instruction to specify a greater variety of operations and operands.

#### 4.3. Multiple Address Instructions

Multiple address instruction formats **carry** with them both benefits and added specification **requirements**. With a single instruction more **operations** are identified, so fewer instructions are required to implement a string **ot** arithmetic. At the same time, the instructions must identify all of the work to do, since no assumptions will be made concerning the location of the data. Thus, multiple address instructions will identify both source and destination of the information. The myriad possibilities are exemplified by the following formats:

Although the system architect can choose any reasonable specification mechanism, the assumption we will make concerning the syntax of these instructions is that the final address specified is the destination of the function. With this assumption, the ADD2 instruction adds the value in the location identified with the A address to the value in the location identified by the B address, and the result is returned to the location specified by the B address. Thus, this instruction changes the value identified by the B address. The ADD3 instruction obtains the operand identified by address A, adds to it the value stored at the location specified by address B. and places the result at the location identified by address C. In a machine that utilizes this type of capability, the op codes must differentiate between the various types of operations.

That is. a separate code must be available for each instruction; ADD2 and ADD3 will be specified by different **patterns**. This results in a larger operation code field, since **many** different codes must be representable. And it also results in different length instructions, since some instructions will require three addresses, **while** others will require only two. Considei the following example, in which we compare two and three address add instructions.

Example 4.2: **Two and three address instructions:** Compare the operation of the ADD2 and ADD3 instructions, using the times identified in Example 4.1. Assume that the operation codes require the same number of bits to represent as the addresses. (Is this a valid assumption?) What is the execution time required for each of the instructions?

In order to address these questions. we need to identify some of the details of the system. That is, before the RTL of implementation can be determined, we need to understand what mechanisms are being utilized. Let us assume that the first value obtained from memory at the location identified by the PC is the appropriate op code, and that the next values are the respective addresses. This is somewhat simplistic, as we shall see a little later. But it will help to identify some of the underlying issues. The next problem to be dealt with needs a little more detailed **consideration**. This **consideration** is the mechanism for the addition: how is it to be carried out, In order to visualize the transfers necessary and the order of events, we need to know the available registers and their interconnection. The basic elements required for this example are given in Figure 4.7. The figure has

Figure 4.7. Block Diagram of System for Example 4.2

two registers, **T1** and **T2**, which are **not part** of the instruction set architecture. That is, the system as defined by the instruction set does not include these storage elements. However, they are very useful when doing instructions that require holding information to be utilized by the system. Armed with this knowledge about the underlying structure, let us examine RTL representations of the instructions.

The RTL statements describing one implementation of the two address ADD instruction is found in Figure 4.8. The figure also contains timing information with the RTL statements, indicating the **time** required to complete the task.

The RTL for the three address case is included in Figure 4.9. Notr the similarity with the two address version in the initial stapes of the instruction

| 1<br>2<br>3<br>4 | M [MAR]<br>PC + Ilen<br>MBR<br>decode | PC     | (50)<br>(300)<br>(50)<br>(50) | Address of instruction to MAR.<br>Instruction lo MBR.<br>Bump the PC to point at address.<br>Instruction finally lo IR. |

|------------------|---------------------------------------|--------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 5                | execute:<br>PC                        | MAR    | (50)                          | Go get address of operand.                                                                                              |

| 6                | PC + Alen -                           |        | (50)                          | Bump PC to point at next address.                                                                                       |

| 7                | M[MAR] -                              | MBR    | (300)                         | This is address of first operand.                                                                                       |

| 8                | MBR -                                 | MAR    | (50)                          | So put in MAR.                                                                                                          |

| 9                | M[MAR]                                | MBR    | (300)                         | And get the value there, first lo MBR,                                                                                  |

| 10               | MBR -                                 | • TI   | (50)                          | And then to TI.                                                                                                         |

| 11               | PC -                                  | MAR    | (50)                          | This is to get address of second operand.                                                                               |

| 12               | PC + Alcn                             | PC     | (50)                          | Bump IC to next instruction.                                                                                            |

| 13               | M[MAR] -                              | MBR    | (300)                         | Address of second operrnd to MBR.                                                                                       |

| 14               | MBR -                                 | MAR    | (50)                          | And then to MAR.                                                                                                        |

| 15               | M[MAR]                                | MBR    | (300)                         | The second operand goes lo MBR.                                                                                         |

| 16               | MBR                                   | • T2   | (50)                          | And then to T2.                                                                                                         |

| 17               | TI + n                                | MBR    | (150)                         | Do the add, results to MBR.                                                                                             |

| 18               | MBR -                                 | M[MAR] | (300)                         | Put results where operand two used lo be.                                                                               |

|                  |                                       |        | (2500)                        | Total time: 2.5 µsec                                                                                                    |

Figure 4.8. RTL Implementation of a Two Address ADD Instruction

|    | fetch:                     |        |                                             |

|----|----------------------------|--------|---------------------------------------------|

| 1  | $PC \rightarrow MAR$       | (50)   | Address of instruction to MAR.              |

| 2  | $M[MAR] \rightarrow MBR$   | (300)  | Instruction to MBR.                         |

| 3  | $PC + Ilen \rightarrow PC$ | (50)   | Bump the PC to point at address.            |

| 4  | MBR 3 IR                   | (50)   | Now, instruction to IR.                     |

|    | decode                     |        |                                             |

|    | execute:                   |        |                                             |

| 5  | $PC \rightarrow MAR$       | (50)   | This is to get first address.               |

| 6  | $PC + Alen \rightarrow PC$ | (50)   | And bump PC by address length.              |

| 7  | $M[MAR] \rightarrow MBR$   | (300)  | Now the address to the MBR.                 |

| 8  | $MBR \rightarrow MAR$      | (50)   | And then to the MAR.                        |

| 9  | $M[MAR] \rightarrow MBR$   | (300)  | This is the first operand.                  |

| 10 | MBR → TI                   | (50)   | So put it in TI.                            |

| II | $PC \rightarrow MAR$       | (50)   | Now, go get the second address.             |

| 12 | $PC + Alen \rightarrow PC$ | (50)   | Bump the PC appropriately.                  |

| 13 | $M[MAR] \rightarrow MBR$   | (300)  | This is the address itself.                 |

| 14 | $MBR \rightarrow MAR$      | (50)   | So, put it in the MAR.                      |

| 15 | M{MAR} → MBR               | (300)  | Now, get the second operand.                |

| 16 | $MBR \rightarrow T2$       | (50)   | And put it in T2.                           |

| 17 | $PC \rightarrow MAR$       | (50)   | Gotta go get the final address.             |

| 18 | $PC + Alen \rightarrow PC$ | (50)   | Bump PC to point to next instruction.       |

| 19 | $M[MAR] \rightarrow MBR$   | (300)  | Get the address of the result.              |

| 20 | MBR → MAR                  | (50)   | And put in the MAR.                         |

| 21 | $T1 + T2 \rightarrow MBR$  | (150)  | This is actual work of the instruction.     |

| 22 | MBR 3 M[MAR]               | (300)  | Put in location specified by third address. |

|    |                            | (2950) | Total time: 2.95 µsec                       |

Figure 49. RTL Implementation of a Three Address ADD Instruction.

implementation. Then, when fetch has been completed and the actual work of the instruction begins, the statements in the RTL reflect the different action of the two instructions.

Since the addresses of the operands are stored in the instruction stream, obtaining and storing information requires two memory references for each value: one to obtain the appropriate address, and another to utilize that address for a fetch or store. Each of these interactions requires time to complete, resulting in seemingly long instruction times, 2.5  $\mu$ sec for the ADD2 instruction and 2.95  $\mu$ sec for the ADD3 instruction. As would be expected, the ADD3 instruction takes longer than the ADD2 instruction, since one more address is involved in the operand specification. This requires modifying the PC to point at the address, and an additional memory access to fetch to get the appropriate address. The resource utilization of these instructions can be viewed in number of ways. If one simply looks at the time required for the instruction. However, if one looks at the time required to implement a set of operations, such as

$$\mathbf{X} = \mathbf{Y} \cdot \mathbf{Z} + \mathbf{W} \cdot \mathbf{V}$$

then the differences become more apparent:

| With ADD2 | With AUUS |       |  |

|-----------|-----------|-------|--|

| MOVE Y,X  | AND3      | Y,Z,T |  |

| AND2 Z,X  | AND3      | W,V,Y |  |

| MOVE W,Y  | RUGA      | f,Y,X |  |

| AND2 V,Y  |           |       |  |

| ADD2 Y,X  |           |       |  |

The stream of instructions that utilize the ADD2 method require 15 memory locations to store and 12.5  $\mu$ sec to execute; the ADD3 method requires 12 memory locations, and executes in 8.55  $\mu$ sec. In contrast to the above methods, a single address implementation of the equation would require 14 memory locations to store, and be executed in 8.95 psec, making similar assumptions about the address storage and execution mechanisms. To more appropriately evaluate the merits of one, two, and three address instruction mechanisms, a more complete set of example instructions and system usage is required.

It is possible to generate examples in which each of the mechanisms discussed thus far — single address machines, two address machines, and three address machines — has a better time characteristic than the other two. Among other things. this indicates that the metric we have chosen for comparison, combined with the underlying assumptions, is not a sufficient test. To make a more realistic comparison, further analysis and additional criteria are required. Nevertheless, the above example illustrates a viable method: when a choice between different alternatives is to be made, a metric is chosen that demonstrates the use of the appropriate system resources, and the associated costs are determined. Caution must be exercised to ascertain that the costs not included in the metrics will not undermine the effectiveness of the comparison.

One observation that could be made concerning the system is that a great deal of the execution time for the ADD2 and ADD3 instructions, as shown above, is consumed in fetching addresses of operands and the operands themselves. A similar comment can be made concerning the number of bits required to store the addresses: if the range of addresses can be limited in some fashion, the number of bits required for addresses (and hence the entire instruction) can be greatly reduced. For both of these reasons — the time required for operand access and the number of bits needed for address specification — register sets have been included in machines.

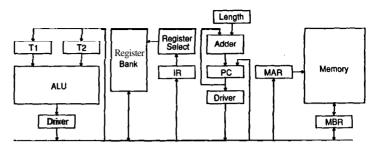

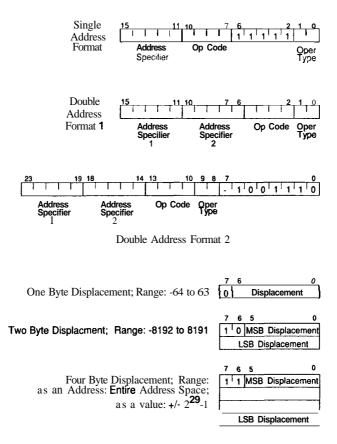

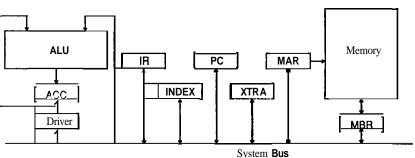

The use of a register set reduces the time required for instruction performance. One demonstration of this is to rework Example 4.2, this time assuming that the add instructions deal with values in registers, rather than values that reside anywhere within the memory space of the machine. The block diagram for this example is given in Figure 4.10. Note the similarities and differences with Figure 4.7. The main difference is the inclusion of a **set** of registers, shown here to contain 8 different storage locations. Thus, to represent the operand location requires only 3 bits, and this field can be incorporated into the instruction format. The net result is a reduction in the number of memory references required by each instruction to get information.

*Example 4.3: ADD2 and ADD3 instructions with registers:* Again compare the operation of the ADD2 and ADD3 instructions, but this time assume that the operands reside in registers, and that the register specification is **con**-

Figure 4.10. Block Diagram of System for Example 4.3.

**tained** within the instruction itself. That is, an additional memory cycle to obtain addresses is not required, since the identification of the appropriate register is accomplished by using a multiplexer (register select MUX) to select the appropriate bits from the instruction register, as shown in Figure 4.10.

The RTL required for this example follows the RTL for the previous example, with the obvious differences:

| ADD2 R <sub>A</sub> , R <sub>B</sub> |       | ADD3 R <sub>A</sub> , R <sub>B</sub> , R <sub>C</sub> |       |

|--------------------------------------|-------|-------------------------------------------------------|-------|

| $PC \rightarrow MAR$                 | (50)  | PC -4 MAR                                             | (50)  |

| $M[MAR] \rightarrow MBR$             | (300) | $M[MAR] \rightarrow MBR$                              | (300) |

| $PC + Ilen \rightarrow PC$           | (50)  | $PC + Ilen \rightarrow PC$                            | (50)  |

| $MBR \rightarrow IR$                 | (50)  | MBR -4 IR                                             | (50)  |

| $R_A \rightarrow TI$                 | (50)  | $R_A \rightarrow T1$                                  | (50)  |

| $R_B \rightarrow n$                  | (50)  | R <sub>B</sub> -4 T2                                  | (50)  |

| $TI + T2 \rightarrow R_B$            | (150) | $T1 + T2 \rightarrow R_C$                             | (150) |

|                                      | (700) |                                                       | (700) |

Note that the operands are in the registers, and the resulting instruction times reflect the reduced requirements for operand access. Both instructions now require 700 nsec, but we must recognize that the storage requirements are different for both instructions. That is, the ADD2 instruction must be wide enough to include two addresses, while the ADD3 instruction must be even wider, sufficient for three addresses. If all instructions are to be the same width, it must be the wider of the two formats. That is, if instructions are to be a common width (to match a memory constraint. for example), then the word width must match the widest instruction. For a system utilizing this technique, an instruction that requires fewer than three addresses will waste some of the capabilities of the storage mechanisms. The point is that tradeoffs must be applied to each situation to determine their relative merits, and the choice of the metric will directly impact the comparisons. The metrics may include the number of bits (or bytes) required to store a program segment, the time required to execute, the complexity of the algorithms required to implement the instructions. or any of a number of other appropriate metrics.

The above example **demonstrates** that the use of registers greatly reduces the time requirements for instructions. As mentioned above, the main reasons for this are the reduced time requirements for interacting with the operands and reduced memory requirements for storing the instruction itself. The reduced time requirements for operand access result from the fact that register access is faster than main store access. The reduced memory requirements are a function of operand identification, since identification of an appropriate register requires a **few** bits, while identification of a main store address requires a great many more bits. We have used the example of the IAS, which used 12 bits to identify a location in memory; more recent systems. such as the 68030 microprocessor, require as many as 32 bits to specify a location in memory.

A number of existing machines utilize multiple address formats, and we can benefit from an examination of the instruction set architecture of those systems. However, before we consider those machines, we will need to examine a "fcature" that we have ignored to this point. The very mechanism that saves time by reducing the memory requirements also reduces to a very small number the allowable locations for operands to reside. However, in general. we would like to be able to access any operand, and operands should be able to reside anywhere in main store. Thus, some mechanisms must exist that will allow operand access to arbitrary locations. Let us examine some of the mechanisms used for operand access.

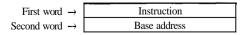

#### 4.4. Operand Addressing Mechanisms

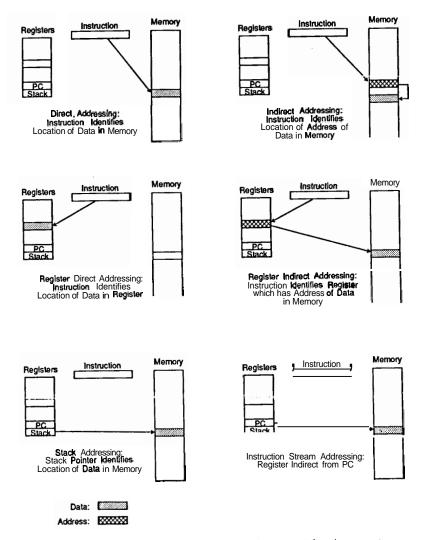

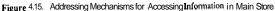

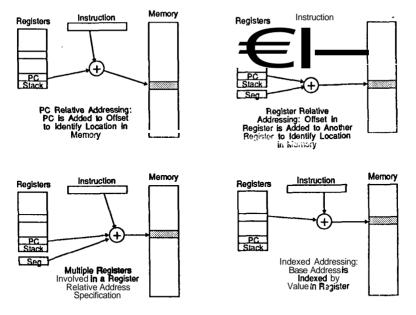

When an instruction requires an operand for execution, the location of the operand can be assumed. as in the CLA (clear accumulator) instruction, or the operand location can be identified in the instruction itself. In this section we will examine different mechanisms for the specification of the location of the operand. First we will look at direct and indirect addressing, and some variations of indirection that have proved useful in different machines. Then we will look at some of the indexed and register relative modes. Combinations of these mechanisms will provide the versatility needed to identify locations in main store for all types of machine instructions. A visual representation of the addressing mechanisms is included in Figure 4.15 (page 154), and it may be useful to refer to that figure throughout the section.

In our discussion of addressing modes, we are concerned with the manner of specification of the effective address of the operand. That is, how is the location of the operand identified. Thus, we are concerned with the generation mechanism or formula for the effective address (EA).

The term "direct addressing" refers to the situation where the effective address of the operand is supplied directly by the instruction. Thus, for direct addressing

#### EA = A

That is, for the ADD2 X, Y instruction. with direct addressing,

#### $EA_{OPERAND |} = X$

### $EA_{OPERAND 2} = Y$

The actual address is contained within the instruction. This is the situation that was **assumed** for the instructions considered in Example 4.3. As we have

mentioned, various costs associated with this method diminish its effectiveness, so other approachs to operand identification are used. One useful mechanism is to use the information contained in an instruction to identify not the operand, but rather the address of the operand.

The **term** indirect addressing is applied when the instruction identifies not the operand, but rather the location of the operand. That is, for an ADD2  $\mathbf{x}, \mathbf{y}$  instruction with indirect addressing,

## $EA_{OPERAND |} = M[X]$

# $EA_{OPERAND 2} = M[Y]$

The information in the instruction tells the machine where to find the address of the appropriate operand. Different manufacturers have different mechanisms for specifying that a value identified by the instruction is not an operand, **but** rather the address of an operand. **The** mechanism we will use is to include an asterisk (\*) before the operand specifier. Thus,

#### ADD2 X, Y

specifies an instruction that adds a value stored at location X to a value stored at location **Y**. However,

## ADD2 \*X. \*Y

specifies an instruction that adds two values: the address of the first value is found at location X, and the address of the second value (as well as the result) is found at location Y. These mechanisms can be combined in instructions, so that

# ADD2 \*X.Y

adds the value found in main store at the address found in location X to the value at location Y, and the result is placed in location Y.

The usefulness of indirect addressing is best demonstrated by example. Then a variety of uses becomes apparent, such as accessing arrays in a regular fashion or accessing information in a data dependent fashion.

*Example 4.4: Indirect addressing:* Using indirect addressing and two address instructions, demonstrate a method for adding the elements of three single dimensional arrays together. These arrays are located in main store. and their starting locations are also found in main store at the locations named ARRAY, ARRAY<sub>2</sub>, and ARRAY, The result is to be placed in an array in main store, the starting location of which is in a location named ARRAY<sub>4</sub>.

We have not yet considered the branching instructions needed for this problem, so those functions will be identified but not specified. Also, we will make the assumption that the information is stored one value per location (instead of double precision or other considerations), so that **increment**ing an address by one automatically points to the next value. This addition could be performed in a number of ways, but one way is demonstrated by the following instructions. Set up problem first, then enter this loop:

| over: | MOVE *ARRAY <sub>1</sub> , <i>TEMP</i><br>ADD2 *ARRAY <sub>2</sub> , <i>TEMP</i><br>ADD2 *ARRAY <sub>3</sub> , <i>TEMP</i><br>MOVE <i>TEMP</i> , 'ARRAY, | Get value from first array.<br>And add value from second array.<br>And third array.<br>Now move answer to right spot.<br>With the arithmetic over, adjust<br>the addresses appropriately. |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | INC ARRAY                                                                                                                                                | These increment instructions                                                                                                                                                              |

|       | INC ARRAY <sub>2</sub>                                                                                                                                   | bump each address to point                                                                                                                                                                |

|       | INC ARRAY,                                                                                                                                               | to the next value.                                                                                                                                                                        |

|       | INC ARRAY <sub>4</sub>                                                                                                                                   |                                                                                                                                                                                           |

|       | if nor done. go to over                                                                                                                                  | End of loop.                                                                                                                                                                              |

Note that the **MOVE** and ADD2 instructions access the information in the arrays indirectly. Thus, the location identified in the instruction is not the location of the operand, but rather the location where the address of the operand is found. Then the increment instructions, which access their appropriate locations directly, cause the addresses to point to the next elements of the appropriate array. The way in which the above section of code was written modifies the locations ARRAY<sub>1.4</sub>, which is in general not a good idea. A better solution would have been to place these addresses in temporary locations and operate on them in those locations. Another comment that **can be** made concerns the use of the temporary location. The location would not be needed if the MOVE instruction placed the value in the location identified by ARRAY, and the subsequent ADD2 instructions used that location to sum the value. Thus, the number of memory locations needed for the execution of the program would be reduced. However, indirect references require one more memory reference than direct references, so the required time to complete the code would be increased. Thus, the "best" solution will be determined by which metric is the critical one for the application.

Including both direct and indirect addressing mechanisms in an instruction set allows a **wide** variety of operand access capabilities. **These** concepts are directly applicable to systems with register sets, where the identification bits in the address refer to a specific register. Direct addressing in this fashion is sometimes referred to as register direct addressing. An indirect reference occurs when the value contained in the register is an address identifying the location in main **store** of an operand. This would then be register indirect addressing, and operates in the same fashion as the indirect addressing mentioned above. The benefits af this mechanism have already been identified: the number of bits required to specify the address are reduced, and the time required for register access is much less than that required for main store access.

*Example 4.5: Cost of direct and indirect addressing:* Determine the times for the ADD2 instruction using direct and indirect addressing. Compare the system of Figure 4.7, which doesn't have a register set, with the system of Figure 4.10, which includes a general register set.

The times required for these instructions can be obtained only if we know the set of register transfers required to accomplish the work of the additions. So, the first step is to obtain the RTL of instruction implementation. First we will look at the system without registers, then observe the

effect when a register set is available. The direct addressing implementation of the ADD2 instruction is shown in Figure 4.11. The transfers required to perform the work consume a total of 2.5 psec. Of that time, 0.450 psec is required for fetching the instruction, the other 2.05 psec is used in execution. Another view of the time requirements comes from examining the time used by the memory interaction. There are six memory transfers, one for the instruction and five for addresses and operands; these total 1.8 psec. We would expect the indirect addressing example to take even more time, and this is confirmed by examining the RTL of the indirect addressing version contained in Figure 4.12. The indirect addressing system is longer, but only by 0.7 psec. The instruction fetch again took 0.45 µsec, while the eight memory transfers consumed 2.4 psec, or 75% of the total instruction time. This gives an indication of one of the reasons that computer architects have attempted to reduce the memory interaction as much as possible. The times involved in the register implementations of the ADD2 instruction indicate how well that can be accomplished.

The work required for register-oriented **ADD2** instructions, both for direct and indirect addressing, is demonstrated by the RTL implementations in Figure 4.13.

An examination of the implementations of Figure 4.13 indicates that indeed time is saved when the operands (and/or addresses) are contained in the registers. When the operands are located directly in the registers, then the ADD2 instruction requires only 0.7 psec, 28% of the time required for the memory implementation. The principal contributor is the fact that this implementation requires only one memory transfer, compared to six transfers for the ADD2 X, Y instruction.

| fetch:    |               |        |        |                                       |

|-----------|---------------|--------|--------|---------------------------------------|

| PC        | $\rightarrow$ | MAR    | (50)   | First, address of instruction to MAR. |

| PC + Ilen | ->            | PC     | (50)   | Now bump PC.                          |

| M[MAR]    | $\rightarrow$ | MBR    | (300)  | Retrieve instruction.                 |

| MBR       | $\rightarrow$ | IR     | (50)   | And move to IR.                       |

| decode    |               |        |        |                                       |

| execute:  |               |        |        |                                       |

| PC        | →             | MAR    | (50)   | This to get address of X.             |

| PC + Alen | $\rightarrow$ | PC     | (50)   | Bump PC by length of address.         |

| M[MAR]    | $\rightarrow$ | MBR    | (300)  | MBR now contains address of X         |

| MBR       | ->            | MAR    | (50)   | So put in MAR.                        |

| M[MAR]    | $\rightarrow$ | MBR    | (300)  | And retrieve X.                       |

| MBR       | $\rightarrow$ | TI     | (50)   | Move operand to T1.                   |

| PC        | $\rightarrow$ | MAR    | (50)   | Do same thing for Y.                  |

| PC + Alen | $\rightarrow$ | PC     | (50)   |                                       |

| M[MAR]    | $\rightarrow$ | MBR    | (300)  |                                       |

| MBR       | $\rightarrow$ | MAR    | (50)   |                                       |

| M[MAR]    | $\rightarrow$ | MBR    | (300)  |                                       |

| MBR       | $\rightarrow$ | T2     | (50)   | Move Y to T2.                         |

| T1 + T2   | $\rightarrow$ | MBR    | (150)  | Do the ADD.                           |

| MBR       | $\rightarrow$ | M[MAR] | (300)  | And store back where Y was.           |

|           |               |        | (2500) |                                       |

ADD2 X. Y (Direct Addressing)

Figure 4.11. RTL Implementation of a Two Address ADD Instruction with Direct Addressing.

|           |               |        |                 | 8,                                        |

|-----------|---------------|--------|-----------------|-------------------------------------------|

| fetch:    |               |        |                 |                                           |

| PC        | $\rightarrow$ | MAR    | (50)            | As before, address of instruction to MAR. |

| PC + Ilen | $\rightarrow$ | PC     | (50)            | Bump PC.                                  |

| M[MAR]    | $\rightarrow$ | MBR    | (300)           | Retrieve instruction.                     |

| MBR       | $\rightarrow$ | IR     | (50)            | And move to IR.                           |

| decode    |               |        |                 |                                           |

| execute:  |               |        |                 |                                           |

| PC        | $\rightarrow$ | MAR    | (50)            | This to get address of address X.         |

| PC + Alen | $\rightarrow$ | PC     | (50)            | Bump PC by length of address.             |

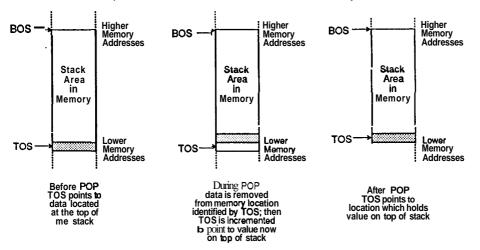

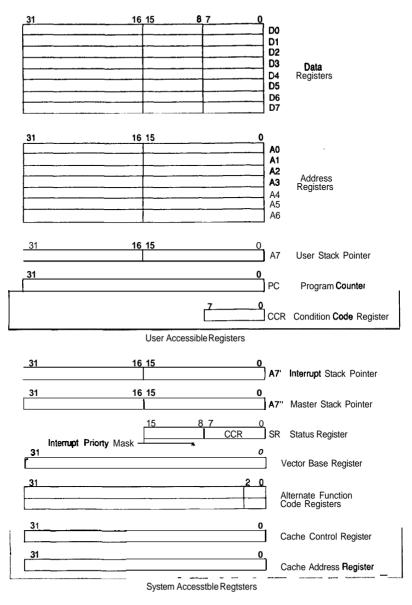

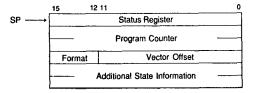

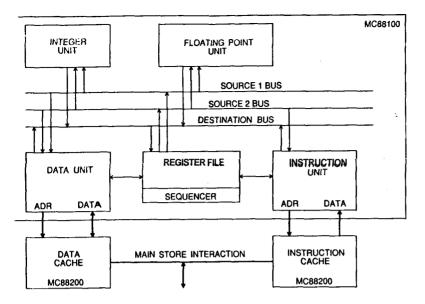

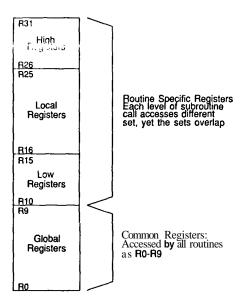

| M[MAR]    | $\rightarrow$ | MBR    | (300)           | MBR now contains address of address X.    |