# Control System Design

The design of a computer system, like that of all digital systems, requires both data manipulation capabilities (logical units, adders, multipliers, etc.) and control capabilities. The data manipulation elements form the data path of the machine, while controlling the flow-of data on that data path is the responsibility of the control section. The design of the data path elements and the instructions that identify the work to be done on the data paths have been the subjects of the preceding chapters. In this chapter we will deal with methods used to control the flow of information within a computer. Our intention is not to provide an indepth discussion of sequential design techniques; a number of excellent texts provide that material [Mano79, Flet80, McCl86, Bree89]. Our intention is to provide some insights into different ways in which those methods can be applied in the design of a control section of a computer.

The control system of a computer is basically a sequential system that implements the fetch-decode-execute function of instruction execution. Since it is a sequential system, it can be designed using the same techniques used to design counters, controllers, or any of a wide variety of digital systems. In this chapter, we examine different techniques for implementing sequential systems, and apply those techniques to the control of computational elements. Thus, our first task is to review some of the concepts used in sequential design.

The application of sequential design techniques will result in a control system that activates the appropriate clock lines, enables, and interface signals to accomplish the work of the computer system. However, before the control system can be specified and implemented, it is necessary to identify the appropriate clocks, enables, and other signals used in the system. Therefore, the first requirement of a computer system design is to develop a detailed data path **block** diagram. This diagram must identify the control lines that can be used to manipulate data in the system. And with this diagram and the definition of the instructions to perform. RTL descriptions of the data transfers needed can be developed. Thus. we will look again at the problem of data path definition and RTL specifications, and see how they are used in the process of control system design.

The designer of a control system must know what signals are available for the control and manipulation of the data in the system; these control lines are identified by the detailed block diagram. In addition, the order of operations must be specified, and this information comes from the RIL descriptions of the work to be done. With this global view of the system, a designer can select the most appropriate sequential design technique and create a system that will assert the control lines to do the work. We will look at different methods for implementing the control systems, providing examples of each.

### 5.1. Elements of Sequential Design: A Review

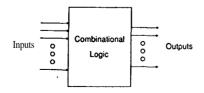

The circuits of the preceding chapters are all classified as combinational circuits: the outputs are functions only of the inputs. These can be modeled as shown in Figure 5.1; the outputs will change whenever the inputs change. This model applies to a variety of devices and circuits: random logic, ALUS ('181, '381), multiplexers ('151, '157), decoders ('138, '154), memories, PLAs, and the like. Nor-raally we like to think that these circuits are perfect, that the outputs will change instantaneously to their new value whenever the inputs change. However, associated with real devices are real delays, and the outputs will follow the inputs after some finite time delay. Some outputs may change during the finite time delay. and resume their former values after the delay period has passed. This results in glitches from occurring or to ascertain that, if glitches do occur, they will not cause problems. Thus, a designer must be aware of the timing restrictions in the process of creating the data path and the transfers represented by the RTL statements.

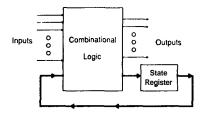

If a system is to have outputs that reflect not only the current set of inputs, but the history of the system as well, then a different model is necessary. An addition to the model of Figure 5.1 is shown in the model of Figure 5.2. Here the outputs are not only a function of the current inputs, but also the past history of the system as well. This history is reflected in the "state" of the machine, which is the value stored in the collection of memory elements within the system. If there are N memory elements, then there are  $2^N$  possible states that the system can assume. Hence, systems with more than a few flip-flops are intractable; a system with 20 bits of memory arranged in registers or other flip-flops would have more than a million possible states.

Figure 5.1. Block Diagram of Simple combinational Circuit.

Figure 5.2. Simple Block Diagram of Sequential Circuit.

Figure 5.3. Sequential Circuit: A Moore Machine.

The system depicted in Figure 5.2, where the outputs are functions of both the current state and the inputs, is called a Mealy machine. This kind of machine is useful in certain circumstances, but can cause problems because of the lack of synchronization between inputs and states. That is, the outputs may be of varying lengths, since the inputs change asynchronously with respect to the states of the machine. A different, slightly more restricted, model for a sequential system is shown in Figure 5.3. This type of system is called a Moore machine. Here the outputs are functions of the present state only. Inputs then influence the outputs only in that they can affect the next state of the sequential machine, but the outputs are not directly functions of the inputs. This model, and variations of it, represent the controllers that we will consider for the control sections of computers and other digital systems. The outputs of the sequential machine will be the control signals needed to manipulate data and move it within the system. The inputs required to specify the desired sequence of steps consist of synchronization flags, status bits, test conditions, and other information that influences the behavior of the system. The designer's challenge, then, is to design a sequential system that will assert the outputs in an appropriate manner to accomplish the work of the system. However, before the control system can be defined and the sequence of outputs specified, the data path must be specified and the control signals on the data path identified.

# 5.2. Data Path Formulation

The formulation of the data path for a **computer** or other digital system is a complex task that is influenced by many factors. The foremost requirement is that the system be able to perform the action required by the underlying task. Just how that task is accomplished is a designer's choice; the decisions made by the designer reflect his understanding of the task and the requirements imposed by system constraints. Consider, for example, the IBM System **360/370** family of computer systems. This was one of the first families of computers in which the different models were identified in the beginning, rather than having different models announced as permitted by customer demand and marketing strategy. The 360 family was set up to cover a variety of performance capabilities and economic ranges. Nevertheless, a program executed on different members of this family should **arrive** at the same answer on each machine. The instruction set architecture of the system appears the same to a programmer regardless of the model on which the program runs. However, the techniques used to implement the operations vary from model to model. The number of data paths, the arithmetic units, the memory interactions, and the control system for each model are configured to match different sets of economic and performance constraints. The same idea will **be** true for all digital systems: the parts used, the data paths provided, and the interfacing methods will be dictated by the intended use of the system. Some of the constraints and their implications are listed below:

- Economic: How expensive are the components used to build the system? This includes not only the integrated circuits, but other components as well, such as sockets, connectors, display elements, wire, printed circuit boards, and **so** on, as well as manufacturing costs.

- Interface requirements: Many devices are specifically designed to interface to TTL components. However, other technologies can require a different set of voltages and currents for information exchange. This also applies to the protocols required for the exchange.

- **Speed**; A variety of questions must be addressed. One of the first is to choose the technology in which the system will be implemented. Lower speed requirements can utilize some **MOS** technologies that conserve energy and do not have fast cycle times. Higher speed technologies, such as ECL and **GaAs**, require careful adherence to design constraints. However, another speed issue is the extent of the use of concurrency within the system, from pipeline techniques to multiple data paths. Each of these options carries with it a set of constraints that identify its range of usefulness.

- Power: The amount of power that a system utilizes may be a factor in the system. If the unit is to operate on battery power for extended periods of time, or be limited in the amount of available power, then the designer must select components and techniques accordingly.

- *Dynamic* range: Arithmetic requirements are often mandated by the intended applications of the system and the allowable signal to noise ratio. A system may be able to satisfy the data representation requirements with integer or fixed point arithmetic of a certain number of bits; or the required dynamic range may indicate that floating point operations are necessary. The data paths and arithmetic capabilities must match system needs.

- *Flexibility:* Many digital systems are created not to solve a single problem, but to provide a device that can be used in a variety of applications to achieve a reasonable solution. Therefore, the system must be flexible enough to be used easily in any of a number of target areas.

- Maintainability: Building a computer system. or other digital device, to satisfy

a particular need is only part of the overall problem. Because of device

failures, power surges, or other problems the system will at some time cease to

function properly. One of the desirable characteristics for digital systems is

that they be maintainable. That is, the design and the implementation be done in such a way that devices and subsystems that are not functioning properly can be identified and easily replaced.

• Environment: This nebulous heading is used here to include a variety of other types of restrictions. If the system is satellite-based, it must not only conserve power used, but it also may have a radiation hardening requirement. If the unit is to operate in an airplane, it may have vibration tolerance requirements, extended temperature requirements, or other restrictions.

Acceptable limits for these and other requirements are identified by the specifications for the system to be designed. The designer must utilize the ingenuity that he has to propose a design that will meet the specifications of the system. There are many different approaches to solving a given problem; indeed, vastly different data path solutions may be proposed which satisfy the requirements of the system. These approaches may use single bus implementations, multiple bus implementations, point to point techniques, or any of a variety of approaches. In any case, the system must satisfy the requirements placed upon it by its application area and intended use.

The designer must select the data path components from the pool of available parts in the target technology, arrange the components and the **interconnec**tions so as to meet the system requirements, and identify the basic transfers and manipulations required to perform the necessary work. We wish to make two points. First, the design of the data path is basically independent of the control design. There may be factors in the intended control design that influence the data path formation, and there may be elements of the data path that bear on the control design, but basically they **are** two different problems. Second, having identified the elements in the data path, a designer must then identify the signals that will control the flow of information within the data path. It is the responsibility of the control section to **assert** the signals in such a way that the appropriate work is accomplished, and, once the signals are identified, the design of the control section can proceed to achieve that objective.

To reiterate the points made above, the designer must:

- First select an appropriate technology and a set of components in that technology to provide for the needs of the system.

- Interconnect the components in such a way that the work of the system can be accomplished.

- Then, using a register transfer language or other means of specifying the action to take place, identify the data transfers and arithmetic required by the system.

- Identify the control signals required to accomplish the work of the system.

When the data path has been defined to this level, the design of the control portion of the circuitry can **proceed**.

This process is best illustrated by an example. The example chosen here, and the other examples in this chapter, are contrived to illustrate specific points, and do not necessarily reflect the "trickiest" way to accomplish some work. But once the principles have been identified, the designer can then proceed to apply them to other designs. The following example, like the other examples in this chapter, is more extensive than those in earlier chapters; for instance, Section 5.7 consists entirely of two different implementation techniques applied to the same

machine. Therefore, the examples here are interwoven with the text, not separated as a short example to illustrate a single point.

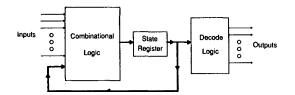

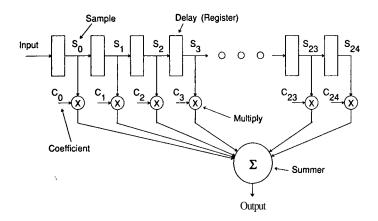

Our first example of a digital system is the calculation of an inner dot product. This is used repeatedly in mathematics for doing matrix manipulations; it is also used in digital signal processing for transversal filters. The example is to design a finite impulse response (First digital filter with 25 coefficients. The equation for this calculation is:

output =

$$\sum_{i=0}^{24}$$

S, **x C**,

where S, represents samples of an input stream and  $C_i$  represents constant coefficients. We will assume that the system is to stand alone; that is, that the system will contain an A/D converter to provide samples and a D/A converter to accept outputs. We will also assume that the coefficients are known and constant. The data manipulations involved in the FIR process are shown in Figure 5.4. The input is sent to a delay network, which saves 25 values of the data stream. Each of the delayed values forms one of the  $S_i$  of the above equation. Each sample is multiplied by its corresponding coefficient (C,), and all of the resulting values are summed to form the final result. The system **architect/designer** has the task of implementing the data manipulations represented by the **FIR** equation in real hardware.

The network shown in Figure **5.4** could be implemented directly in hardware. However, that would require **25** separate multipliers and some mechanism for summing **25** results in parallel. A more conservative solution is to build a system around a **multiply/accumulator** (MAC), a device that will perform a multiply and an add in each clock cycle. These modules have been available for several years and are applicable to a variety of different calculations; the FIR example is an ideal use for this module, since the chip performs all of the arithmetic needed to obtain the result. To present the appropriate values to the MAC, we will utilize memories to store the data and the coefficients. Thus, our problem will be to design a system that will accept a sample, store it in a memory, and then perform the calculations identified by the above equation using the current sample and the previous **24** samples.

Figure 5.4. Data Manipulations Involved in Inner Dot Product.

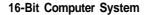

A simple block diagram of a piece of hardware to do this is shown in Figure 5.5. The MAC can be connected to the other elements of the system in a variety of ways to satisfy different system requirements. The solution shown is capable of a fairly high computation rate, and yet is simple in its implementation. The elements of the system, their names and their responsibilities are as follows:

- Coefficient memory: (C\_MEM[k]) This memory contains the constants (C<sub>i</sub>) needed by the algorithm. The memory chosen here is a small PROM (programmable read only memory).

- Coefficientmemory address register: (C\_ADR) This is a counter used to identify the current coefficient. It must start at zero for each iteration and increment through the coefficient numbers, which are used directly as coefficient addresses.

- Sample memory: (S\_MEM[k]) The sample memory is used to store the current sample and the previous 24; actually the memory is made of a number of RAMs, so 32 values are stored, but only 25 used for any single calculation.

- Sample memory address register: (S\_ADR) This counter is initialized to the address of the current sample; it is then incremented to point at the preceding samples in order.

- *Initial sample address register:* (I\_ADR) This register identifies the starting point of the algorithm for each pass. The correct starting point for the current iteration is one less than the starting point for the previous iteration. Thus, this counter will decrement once each pass.

- AD converter: (ADIN) This module provides the new data for each iteration. We assume that the time at which conversion begins is controlled by an

Figure 5.5. Simple Data Path Block Diagram for Finite Impulse Response System.

external source. When new data is available, a ready Rag will be asserted. Thus, testing this ready Rag will identify when the algorithm should be performed.

- **DIA converter:** (DAOUT) This module accepts the output of each interaction and converts it to an appropriate analog value.

- **Output register:** (OUT) This is a register that isolates the **D/A** converter from the values on the output of the MAC during the calculation process.

- *Multiplier/accumulator module:* This module has the responsibility for doing the arithmetic needed by the algorithm. It will do each multiply, then add the value to a running sum. There are three registers internal to the system, two input registers (X, Y) and an output register (P).

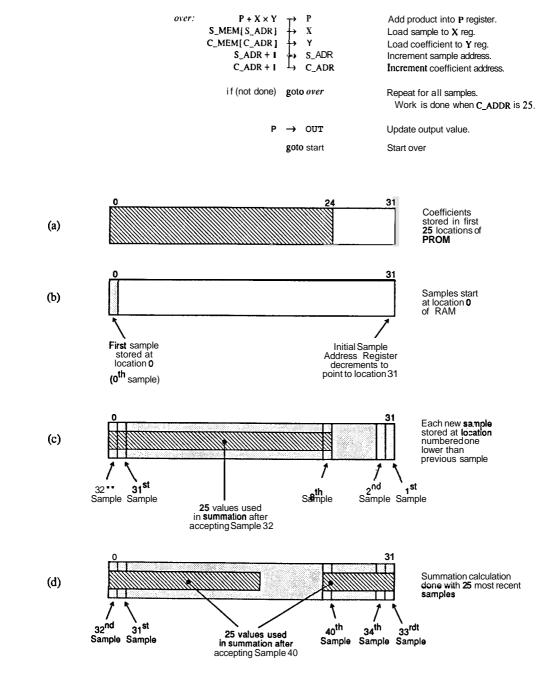

When the designer has arrived at a data path representation such as that shown in Figure 5.5, the next step is to identify the work to take place. As identified in the formula defining the calculation. 25 coefficients will be multiplied by 25 data values, and the results of the multiplies summed to the result. Assuming that the RAM and PROM (for the data and coefficient storage) both contain 32 locations, these memories can be visualized as shown in Figure 5.6. Part a shows the coefficient storage. These values are always used in order, from location **0** to location 24. Thus, at the beginning of each iteration the address register for the coefficients will be set to zero. Figure 5.6(b) indicates that the first value received will be placed in location **0** of the RAM, and then the initial sample address register will be decremented. Thus, the next location to be filled by a sample value will be location 31. Figure 5.6(c) shows the contents of the RAM after 33 samples have been received. The 33<sup>rd</sup> sample (Sample 32) overwrites the first sample (Sample 0). The output of the FIR calculation uses the 25 most recent samples, also identified in part c. The 25 most recent samples utilize a different portion of the RAM for each iteration. The samples used for the 41<sup>st</sup> iteration (Sample 40 through Sample 16) are identified in of Figure 5.6(d). Once the basic algorithm is understood, we can specify the work to be done with RTL statements:

start: if (ADIN not ready) goto start Check input data.  $\begin{array}{c} 0 \\ I_ADR \end{array} \begin{array}{c} C-ADR \\ S_ADR \end{array}$ Clear coefficient address. Load sample address.  $\overset{\text{ADIN}}{\text{I}_{ADR}} \overset{\text{S}_{MEM}[S_{ADR}]}{\downarrow} \overset{\text{ADIN}}{\text{I}_{ADR}}$ Data to sample memory. Decrement initial address. S\_MEM[S-ADR ] → Load sample to X reg. Х C\_MEM[C-ADR] Y Load coefficient to Y reg. Increment sample address. S-ADR + I S\_ADR Increment coefficient address. C ADR + I C ADR ' X × Y Load product register. S MEM[S\_ADR] Load sample to X reg. х C\_MEM[C-ADR] Y Load coefficient to Y reg. S-ADR + I Increment sample address. S-ADR Increment coefficient address. C-ADR + I C-ADR

Chap. 5: Control System Design

201

This identifies the work needed to perform the appropriate calculations, as well as the possible parallelism of simultaneous events. The system waits for new data to become available (ADIN ready), at which point the data processing begins. The first step is to clear the coefficient address and load the sample address register from the initial sample address register. These two events can happen simultaneously. Then, the input value is loaded into the sample memory (at the address just loaded into C ADDR from I ADDR), and the initial sample address is decremented. Again, these two events can occur at the same time. The next step is to load the first sample and the first coefficient into the X and Y registers of the MAC, as well as increment the sample address register and the coefficient address register. The next group of transfers specify loading a product into P, a new sample into X, a new coefficient into Y, and incrementing the address registers. At this point a loop is entered, which adds the new product to the running sum, loads a new sample and a new coefficient, and increments the address registers. This continues until the process is done, which will occur when the final samplecoefficient product has been added to the running sum and is available at the inputs of the output register. This condition is checked simply by counting the number of operations, and when the result is ready moving on to the next transaction. The final transfer moves the newly calculated value to the output register (OUT), at which point control returns to the beginning to start over again.

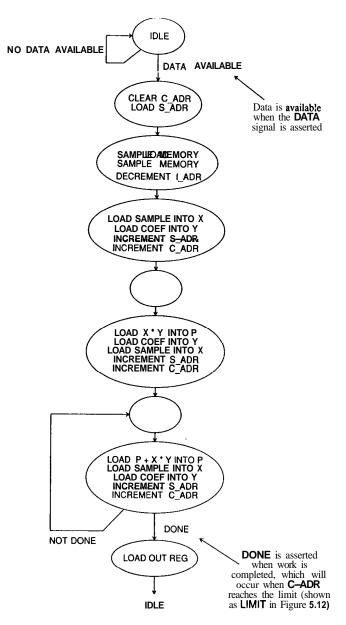

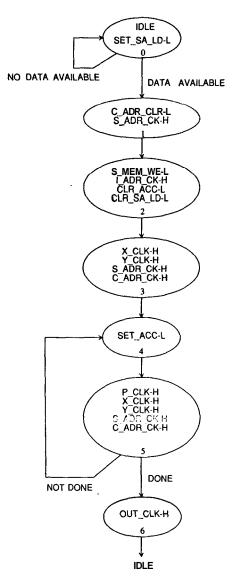

If all of the transfers in the **RTL** occur instantaneously, then there is no problem with the system. However, in real systems each of the actions identified in the **RTL** takes a nonzero amount of time to accomplish. One of the challenges of the designer is to create a control section that will manipulate the signals in such a way that the transfers maintain the appearance of the simultaneity specified in the **RTL**. To prepare to design such a control section, we will create a state diagram that identifies the action of the **RTL**. We will see that this state diagram can be used to directly implement an appropriate control section. This state diagram is shown in Figure **5.7**. It is called a preliminary state diagram, because it will be modified slightly before the actual implementation of the control section. The states that do not specify any work are added for timing purposes, and we will discuss them in connection with the actual implementation.

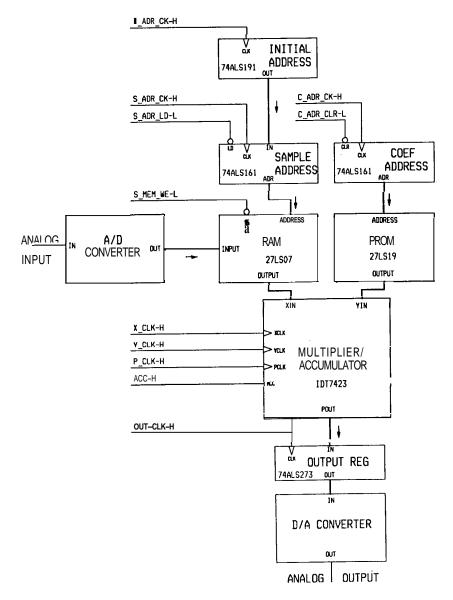

When the **RTL** description of operations and the state diagram are ready, the designer must complete the details of the data path block diagram by choosing the exact parts to be used in the system and identifying the control signals required on those parts to perform the work. Figure **5.8** shows the system of Figure **5.5** with the parts specified and the control signals identified. Note that, although the same parts are used both for the coefficient memory address register and the sample memory address register, the control lines needed are not the same. Both address registers need clocks, so that signal is shown for both blocks. However, the coefficient **MAR** needs to be cleared but not loaded, and the sample **MAR** needs to be loaded but not cleared. These differences are evident in the control signals included in Figure **5.8**. Note also that control lines of the components that do not need to be manipulated during the computation are not identified in the diagram. It is assumed that the designer has studied the specifications of the components and made provisions for the other signals. Some of these will be grounded, others tied to a high level, and so on.

To summarize, the creation of the data path can be done in a manner that is relatively independent from the choice of a control mechanism for a digital system. The designer must first become familiar with the work required of the system. This includes the operations needed, the limitations of the data representation and manipulation methods, the order of events, and other considerations.

Figure 5.7. Preliminary State Diagram for Finite Impulse Response System.

With the system and device specifications in mind, the designer then organizes appropriate devices in such a way that the necessary data manipulations can be performed and the system constraints can be satisfied. The flow of information

Figure 5.8. Detailed Data Path Block Diagram for Finite Impulse Response System.

within the system is then identified with register transfer specifications, state diagrams, and any other design aid that can provide insight into the operation of the system. Finally, the components are identified and the control lines of those components identified so that the detailed design of the control section can be performed.

#### 5.3. A Simple State Machine Controller

Once the problem is understood to the point that a detailed data path block diagram and a preliminary state diagram are available, then the design of the control section can proceed. The classical approach would begin by creating a detailed state **diagram**, then a detailed enumeration of all possible state and input combinations. This would be translated into flip-flop excitation tables, state tables, next state and output truth tables, and logical equations for the appropriate signals. These would then be implemented with random logic, and, if all of the steps were correctly followed, the circuit should do the necessary control work. We present here a method that follows the same basic steps as the classical approach, but that is relatively simple to understand and implement. First, the state diagram is expanded as **necessary** to include the appropriate assertion levels for the control lines of the detailed data path block diagram. Then the system is mapped directly onto the Moore model of Figure **5.3**. The simplicity of the implementation has some advantages and disadvantages, as we shall see.

A state diagram as shown in Figure **5.7** indicates the order in which events should occur to produce the desired results, but the details necessary for the control signals are missing. The designer must be sufficiently familiar with the parts being used so that the assertion of the control lines will be handled correctly. We now examine the primitive state diagram and the detailed data path block diagram in order to derive a correct and complete state diagram.

One observation concerning the state diagram of Figure **5.7** is that there are nine states in it, and to represent all of the states would require 4 bits of state information. One of the first steps of a design procedure is to attempt to reduce the number of states, if feasible, so that the number of bits required to represent the state is at a minimum. Two states in the state diagram appear to be unused, since no work is called out in these states. These states are useful, however, since they play a part in forming the control signals. Asserting signals in some states and not in others results in levels and edges that do the actual work of the system. **A** designer must visualize the desired behavior of the signals and create state sequences to produce that behavior.

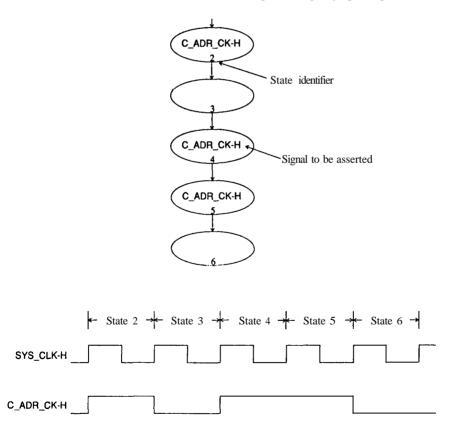

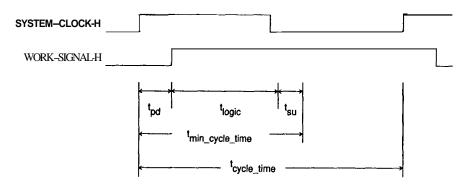

In state diagrams we will identify signals to be asserted by naming them in the states in which they are active. The asserted level of the signal is identified by the use of polarized mnemonics included with the signal name. This is demonstrated by the segment of a state diagram shown in Figure 5.9. Five different states are indicated in the figure, and the system moves from state to state without any branching. Each state time corresponds to a single cycle of the system clock (SYS\_CLK-H). In this fragment of a state diagram a single signal is called for in three different states (C\_ADR\_CK I:), and in each of those states it will be asserted, as shown by the waveform included in the figure. This signal is included on the detailed block diagram of the **FIR** filter implementatio for clock. ing (incrementing) the coefficient address register. However, even though this signal is asserted in three different states in Figure 5.9, the register would only be incremented by two. The implementation calls for a counter that is activated by a rising edge on the clock line, and as seen by the waveform of the figure, there are only two rising edges on C\_ADR\_CK-H. Thus, a designer must be aware of the shape of signal waveforms which will result from specifying assertion of the signals in a state diagram. A signal can be asserted for a single state time (C\_ADR\_CK-H in State 2), or a signal can last for many clock cycles (C\_ADR\_CK-H in States 4 and 5). We will later examine additional methods for creating control signals with state machines.

As shown by the signal waveform of Figure 5.9, removing the "empty" states in the preliminary state diagram would result in an incorrect function for the system. The states cause the signals that control the clocking of the address registers and the loading of the registers of the DAC to become unasserted, so that the proper edges are created when the signals are asserted in the following states. Thus, these states are needed, and another method must be used to try to reduce the total number of states in the state diagram.

The observation we now make is that there is some redundancy in the state diagram: if there is a method of accomplishing "LOAD PRODUCT INTO Z" and "ADD PRODUCT INTO Z" with the same signal, then two of the states can be combined. A careful examination of the specifications for the multiplied accumulator indicates that the function of the PCLK pin is determined by the level of the ACC line at the time that the X and Y registers are loaded. Thus, the desired behavior of the circuit will be obtained if the ACC line is low for the loading of the first values into X and Y, and high thereafter. This will allow combining of the appropriate states from the initial state diagram.

A detailed state diagram can now be created by identifying the desired behavior from the initial state diagram and specifying the signal assertions which

Figure 5.9. State Diagram Segment with Signal Assertion.

will cause that behavior. The new state diagram is given in Figure 5.10, and we will now explain in detail the signal assertions identified there. Two signals identified in Figure 5.10 are controlled by **SET-RESET** flip-flops to allow one behavior in one portion of the state diagram and another in a different portion of the state diagram. These signals are the **S\_ADR\_LD-L** line and the **ACC-H** line. The **S\_ADR\_LD-L** line is asserted by a signal in State **0 (SET-SA-LD-L)** to allow

Figure 5.10. Detailed State Diagram for FIR Filter.

loading of the sample address register when its clock line is asserted in State 1. It is reset in State 2 (by CLR\_SA\_LD-L) to allow the address to increment when the clock line is asserted later. The ACC-H line is cleared in State 2 (by CLR\_ACC-L) to set up the load of the product register. It is set in State 4 (by SET-ACC-L) to allow accumulation of results after the initial product load. We now consider each of the states, and the signal assertions needed for the process:

- *State 0* is the idle state; the **SET\_SA\_LD-L** signal is asserted to set up conditions for loading the sample address register, which will be accomplished in State 1.

- State 1 should clear the coefficient address register and load the sample address register from the initial address register. The clear of the coefficient address register is accomplished by asserting C\_ADR\_CLR-L. The loading of the sample address register requires that the sample address load line be asserted, and then the clock line is asserted. The load was asserted in State 0; the clock is asserted in this state.

- *State 2* causes three things to happen. The **S\_MEM\_WE-L** line is asserted to write the sample into the sample memory (the appropriate address was loaded in State 1). The initial address register is decremented by asserting **I\_ADR\_CK-H.** And the product load condition is set up by asserting **CLR\_ACC-L.**

- *State 3* causes load of the sample (X\_CLK-H) and the coefficient (Y\_CLK-H) into the MAC, then increments the two addresses (S\_ADR\_CK-H, C\_ADR\_CK-H).

- *State 4* sets up the accumulate condition for the product register in the multiplier/accumulator chip by asserting SET-ACC-L.

- State 5 is where all of the work is done in steady state. The first time the state is entered, the assertion of P\_CLK-H causes the product register to be loaded with X × Y. Subsequent assertions of P\_CLK-H load the product register with X × Y + P. Samples and coefficients are loaded by asserting X\_CLK-H and Y\_CLK-H. The addresses are incremented by asserting S\_ADR\_CK-H and C\_ADR\_CK-H. The net result is that values are loaded and addresses incremented to look at the next values. The use of positive edge triggered devices assures that the current values are loaded before they change; the change will occur some time later because of propagation delays in the address registers and the memories themselves.

- State 6 causes the output register to be filled by asserting OUT\_CLK-H.

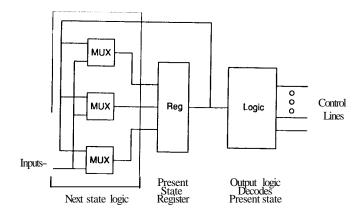

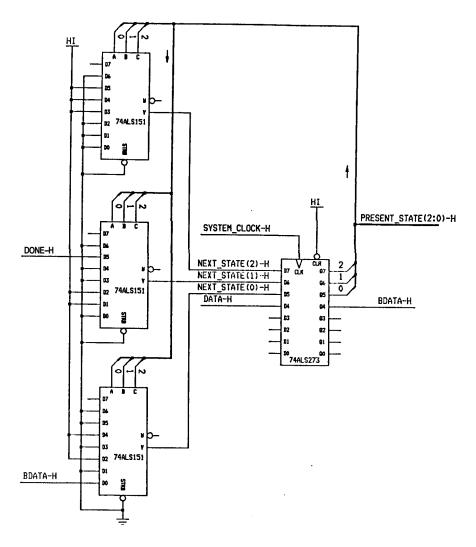

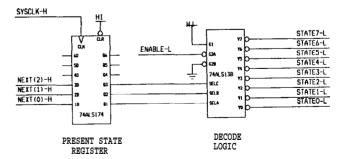

When the state numbers have been assigned to the state diagram, we are ready to map the controller onto the Moore machine. We will do this as shown in Figure 5.11. The present state register holds the current state of the system. The next state logic looks at the present state and the inputs and selects the next state. **As** shown in the figure, the logic blocks in the next state logic are multiplexers; the inputs to the multiplexers are chosen to select the correct next state from the current state. So the outputs of the multiplexers can be specified as shown in Table 5.1. The two signals included in the table have not yet been identified. The first is **DATA-H**, which is a flag from the **A/D** converter identifying that we have new data to process. **A** possible **arrangement** for this flag is shown in Figure **5.12(a)**. Here the end of conversion signal from the A/D converter causes a flip-flop to be set; the flip-flop is cleared by the same signal that clears the coefficient address. The second signal is **DONE-H**, which is asserted when the required number of iterations have been completed. We could create a new counter for

Figure 5.11. Implementation of Control System for FIR Filter.

| Table 5.1. | Next State Multiplexer Specifications. |        |        |

|------------|----------------------------------------|--------|--------|

|            | MUX 2                                  | MUX I  | MUX O  |

| State 0    | 0                                      | 0      | DATA-H |

| State 1    | 0                                      | 1      | 0      |

| State 2    | 0                                      | 1      | 1      |

| State 3    | Ι                                      | 0      | 0      |

| State 4    | 1                                      | 0      | 1      |

| State 5    | 1                                      | DONE-H | . 0    |

| State 6    | 0                                      | 0      | 0      |

this, but that counter would duplicate the numbers used as the coefficient addresses. Therefore, Figure **5.12(b)** shows a comparator connected to generate a **DONE-H** signal using the numbers available from the coefficient address.

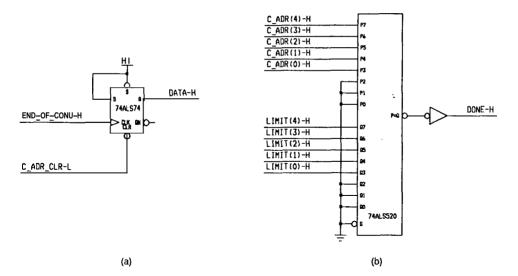

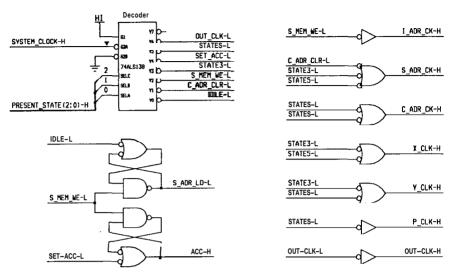

The entries in Table 5.1 specify the inputs needed for the multiplexers for the state machine. The resulting circuit is shown in Figure 5.13. Figure 5.13(a) shows the present state register and the next state circuitry; Figure 5.13(b) shows the decode of the present state register to generate the necessary control signals.

Several observations should be made at this point. The first is that the method described above is simple and direct, and easily applicable to state machines with up to **32-states**. Larger state machines have been constructed using this method, but the number of parts involved becomes unwieldy. The simplicity of the technique allows ideas to be tested quickly; changes are easily made by moving a few wires on the inputs of the multiplexers. The basic feedback mechanism need not be disturbed. This ease of modification allows the circuit to be quickly changed to conform to the needs of the system. This basic system allows different design ideas to be implemented and and tried with a minimal investment of time and **effort**.

One of the tasks required when the implementation has been completed is to check out the system to verify that the unit functions correctly and that the signals are controlled in an appropriate manner. The checkout process must identify and

Figure 5.12. Control Signals for the State Machine.

remedy any errors which cause improper assertion sequences for the control signals. Generally errors will fall into one of two categories: either the system has wiring errors and the behavior does not follow the state diagram, or the implementation is correct but the state diagram is flawed because the designer did not thoroughly understand the system requirements. In either of these cases, modifications to a system designed in the method described above can be made easily, and the system can then be completed.

A second observation concerns the synchronization of input signals with the state machine. Figure **5.13(a)** shows that the **DATA-H** signal is not directly fed into the multiplexers, but that it is first synchronized with the system by sending it through a buffer register that is clocked with the system clock. In the example, the buffer register is the same device used as the present state register, since the device is not entirely utilized. But what is required is keeping the input synchronous with the system clock. If this provision is not made, then the inputs may change in a manner such that, when the system clock does occur, that the next state is changing and the result is an illegal state transition. If the inputs are not synchronized, the system will fail when changes on the input lines occur at the same time that the present state register is being clocked. Note also that the **DONE-H signal** is not buffered by a register. The reason for this is that the **DONE** signal changes synchronously with the system clock, and hence does not need the effect of the register.

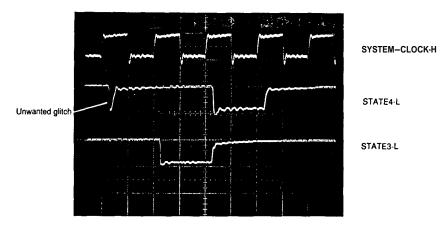

Another observation deals with the generation of the output signals. As shown in Figure **5.13(b)**, the present state is decoded to generate the appropriate signals for the system. Generally our concept is that as the system proceeds through the states identified by the state diagram, the lines of the decoder will become asserted at precisely the right time. However, since real devices contain real delays, and the delays can cause glitches, provisions must be made for the correct **operation** of the system. If the signals being activated are level sensitive,

Figure 5.13(a). Present and Next State Logic for Control System.

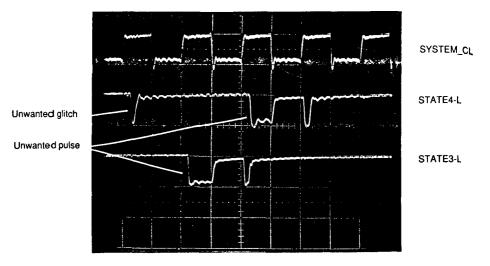

then a glitch will not cause problems. However, if **the** signals are edge sensitive, as all of the clocks in our example are, then glitches on the control lines can cause problems. Figure **5.14(a)** shows a decoder set up to **demonstrate** a number of possible combinations.

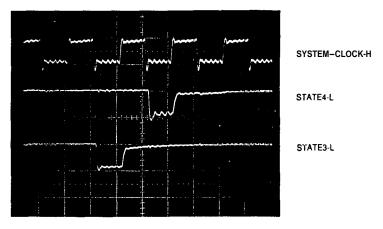

The problem of glitches on output lines is illustrated in Figure 5.14. The control line which is used in different ways in the example is the enable line of the decoder. If the decoder behaves as a perfect decoder, and no glitches occur on the output lines, then behavior similar to the waveform of Figure 5.7 can be obtained by always enabling the decoder. Figure 5.14(b) shows the results when

Figure 5.13(b). Generation of Control Signals from Present State.

the enable line is always asserted: glitches occur on the output lines of the decoders. In Figure 5.14(c) the enable has been tied to SYSTEM-CLOCK-H. The result is that the appropriate decoder output will be asserted only during the time that the system clock is low, which is the last half of the cycle. As can be seen from the figure, the assertion occurs half way through the cycle. This is the method utilized in the finite impulse response filter example. This is the reason that the ACC-H and **S\_ADR\_LD-L** lines are driven from flip-flops, since the decoder outputs are only asserted for half of the cycle.

The success of obtaining the last half of the cycle may prompt one to attempt to obtain the first half of the cycle by using the other phase of the clock.

Figure **5.14(a).** Test Setup for Using State Decoder.

Figure 5.14(b). Waveform for Decoder with Enable Always Asserted.

Figure 5.14(c). Waveform for Decoder with Enable Tied to SYSTEM\_CLOCK-H.

The result is shown in Figure **5.14(d)**, which indicates that unwanted pulses occur; this is a result of the propagation delay from clock assertion to change of decoder output. As can be seen from the **waveforms** of Figure 5.14, a number of options **are** available to a designer, and the merits of each option must be considered before selecting a design method.

The FIR filter example demonstrates some of the basic principles of **con**holler design. It is imperative that the designer first understand the system specifications; this includes aspects often neglected, such as the implications of

Figure **5.14(d).** Waveform for Decoder with Enable Tied to **SYSTEM-CLOCK-L.**

the arithmetic methods, number of bits on the data path, and interaction protocols. The designer then generates a data path block diagram, an RIL description of the desired system behavior, and a preliminary state diagram. These tools assure the designer that the system specifications will be satisfied, and that the necessary data transfers can be made. When the block diagram is defined, the control signals of the components of the system are identified and labeled with appropriate polarized mnemonics. The state diagram can now be refined to specify the assertion of the control signals that will cause the desired work to be accomplished. The state diagram can then be mapped onto the Moore model to provide a working control system. The result is a system that will activate the control signals in the proper sequence to achieve the necessary results.

The state diagram approach is easy to understand, and it is also fairly easy to implement for small systems. We have shown the next state decode logic to be multiplexers; classical methods dictate the use of random logic. Manufacturers now provide registered **PLAs** (programmable logic arrays) that allow the designer to put both the present state register and the next state logic inside a single chip, which is then programmed to follow some specified state diagram. Outputs are handled in much the same way. One use of these controllers will be used in Section 5.6. However, historically other methods have been applied to the control systems of computers. We now **look** at some of these methods.

## 5.4. Sequential Systems with Individual Delays

As we have seen, the first step in any control design is to derive a block diagram that meets the system specifications, and then to identify on that block diagram the control lines needed. In this section we will look at an extremely simple computer, and use that machine to exemplify the delay method of sequential control systems. The principles here are similar to those used in the state machine control of the previous section, but the application methods are slightly different. Rather than have the state of a system stored in a single register, and the state changes reflected by changes in the state number, the action of the delay type system is governed by a control pulse that traverses the elements of the control system.

The technique of individual delays described here has been used in the past for a number of computer systems, but is not widely used in new systems. However, in some systems constructed entirely within an integrated circuit **chip**, delay lines play a prominent part in generating control signals.

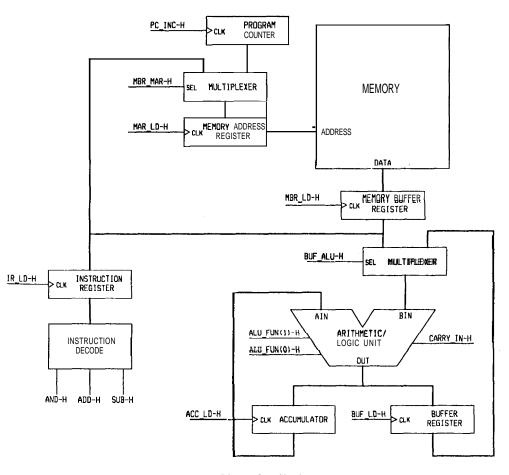

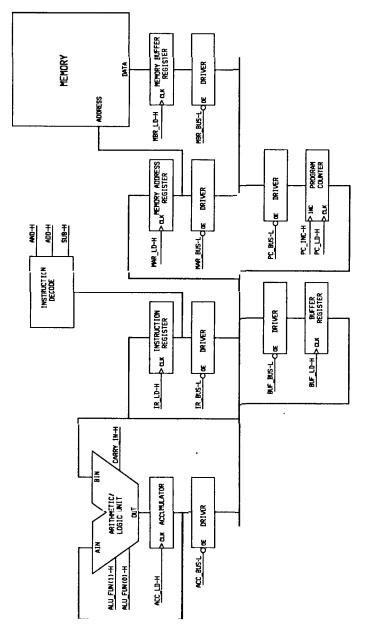

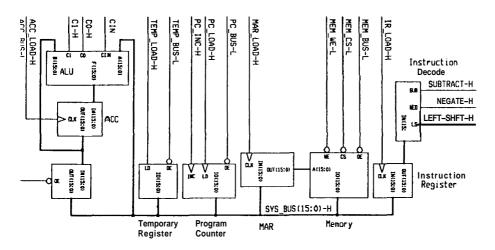

The block diagram for our example is given in Figure 5.15. The diagram shows a simple single address machine, with enough detail represented to illustrate the principles of this section. The diagram does not by any means represent a complete system, since a diagram of that complexity would be overwhelming. The data paths are patterned after some of the first computers: the connections arc

Figure 5.15. Block Diagram for a Simple Computer

basically point to point rather than bused. Note that the data paths are not complete, as exemplified by the fact that there is no path to the program counter.

The desired behavior for this example is to implement three simple instructions: ADD, SUBTRACT, and AND. All three of these instructions require two operands. Since this is a single address machine, one operand is found in the accumulator, and the other is found in memory at a location specified by the instruction. The task required of the control section is to cause the requested action on the data and leave the result in the accumulator.

As in the previous example, the first task is to create a suitable data path block diagram, which was given as part of the definition of the example. The designer then must arrange for the required action, utilizing the capabilities of the data path hardware. The hardware capabilities of this example include:

- Program counter: The content of this register identifies a location in memory where the instruction to be executed can be found. The process of instruction execution should increment this register to point at the next instruction. This can be accomplished by asserting PC\_INC-H.

- *Memory address register:* This register holds an address to identify a location in the memory.

- MAR multiplexer: The multiplexer selects the source of information for the MAR. Normal operation is for the PC to be output to the MAR. However, when MBR\_MAR-H is asserted, the address is obtained from the memory buffer register.

- *Memory:* The memory will provide to the memory buffer register the contents of the address specified by the memory address register within some specified delay. For this example we will assume that the delay is 200 nsec.

- *Memory buffer register:* For destructive readout memory technologies this register remembers the data just read so that it can be restored to the memory. In general, modem semiconductor memories do not need this capability.

- ALU multiplexer: This device selects the BIN operand of the arithmetic/logic unit. Normal operation selects the contents of the memory buffer register; when BUF\_ALU-H is asserted, the ALU receives the contents of the buffer register.

- *Buffer register:* This register is used for internal operations that need a temporary storage location. It is not visible to assembly level programmers.

- Accumulator: This is the known register of the machine. All instructions that manipulate data will find information in this register, and instructions that produce data results will leave their information in this register.

- Arithmetic/logic unit: This functional unit is capable of some rudimentary actions, as specified by the following table:

| ALU_FUN |   | OUT Function            |  |

|---------|---|-------------------------|--|

| 0       | 0 | Bitwise AND of AIN, BIN |  |

| 0       | 1 | Bitwise OR of AIN, BIN  |  |

| 1       | 0 | Inverse of BIN          |  |

| Ι       | 1 | Binary ADD of AIN. BIN  |  |

This ALU has the characteristic that logical operations (AND, OR, INVERT) take 40 nsec to complete; the arithmetic operation (ADD) takes 80 nsec to complete.

- *Instruction register:* This register is used to hold the instruction during its execution.

- *Instruction decode:* The decode circuitry identifies the type of instruction to be **performed.** In this example there are only three, but generally there will be many instructions. The appropriate output line will be asserted to identify which of the instructions has been decoded.

In addition to the times specified for the **ALU** and memory functions, we will assume that register to register transfers require 40 nsec.

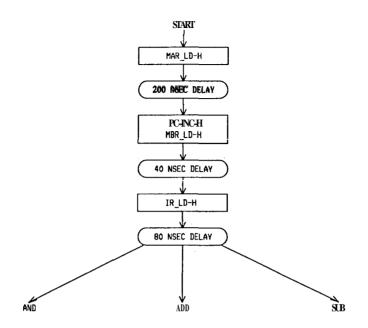

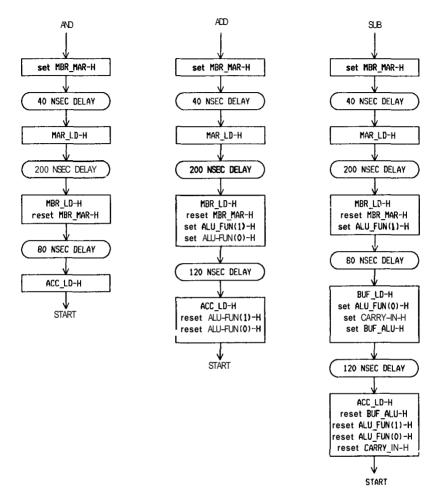

The designer utilizes knowledge of the data path connections and the capabilities of the components used on the data path to specify the required action of the control system. The first step is to identify the required register transfers, and for this example these transfers are given in **RTL form** in Table **5.2**. The table specifies the order in which the transfers are to be accomplished. Our task is now to take these transfers and implement them in hardware. The first step in this process is to generate a flow chart that identifies the required steps. The flow chart for these three instructions is given in Figure 5.16. Note that the flow chart identifies the signal assertions required to accomplish the transfers specified by Table **5.2**, as well as the delays necessary between the **assertion** of **those** signals. Also note that there is a one to one correspondence between the operations identified in Table **5.2** and the operations caused by the signal assertions identified in the flow chart.

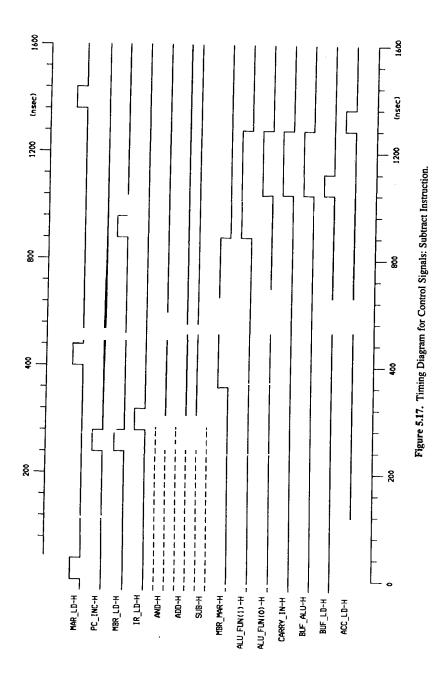

To illustrate the process of instruction execution, we will examine the subtract instruction. A timing diagram showing the control lines involved in this instruction is shown in Figure 5.17. The process begins by transferring the address of the instruction from the program counter into the memory address register with MAR-LD-H. Note that the multiplexer normally supplies this information to the MAR, so no action is required on the control lines of the multiplexer. The memory has a 200 nsec delay, so the MBR\_LD-H signal is delayed by that amount after loading the MAR. The program counter is also incremented at the same time. The instruction register is loaded from the MBR 40 nsec later, since 40 nsec is required for register transfers; after a period of time for instruction decode, the MBR\_MAR line is asserted so that the MAR receives its information from the MBR. A delay time later the MAR-LD-H line is asserted again, loading the address of the operand required for the operation. After the memory

| Register Transfers for Example                    |                                                   |                                          |  |  |  |

|---------------------------------------------------|---------------------------------------------------|------------------------------------------|--|--|--|

| AND Instruction                                   | ADD Instruction                                   | SUBTRACT Instruction                     |  |  |  |

| $PC \rightarrow MAR$                              | $PC \rightarrow MAR$                              | $PC \rightarrow MAR$                     |  |  |  |

| $M[MAR] \rightarrow MBR$                          | $M[MAR] \rightarrow MBR$                          | $M[MAR] \rightarrow MBR$                 |  |  |  |

| $\frac{PC+1}{MBR} \stackrel{PC}{\downarrow}_{IR}$ | $\frac{PC+1}{MBR} \stackrel{PC}{\downarrow}_{IR}$ | $\frac{PC+1}{MBR} \xrightarrow{PC}_{IR}$ |  |  |  |

| MBR L, IR                                         |                                                   | $_{\rm MBR} \downarrow_{\rm IR}$         |  |  |  |

| MBR → MAR                                         | $MBR \rightarrow MAR$                             | MBR → MAR                                |  |  |  |

| $M[MAR] \rightarrow MBR$                          | $M[MAR] \rightarrow MBR$                          | $M[MAR] \rightarrow MBR$                 |  |  |  |

| $MBR \bullet ACC \rightarrow ACC$                 | $MBR + ACC \rightarrow ACC$                       | $\neg$ MBR $\rightarrow$ BUF             |  |  |  |

|                                                   |                                                   | BUF + ACC + I $\rightarrow$ ACC          |  |  |  |

Table 5.2. Register Transfers for Three Instructions.

Figure 5.16(a). Row Chart for Delay Implementation of Three Instructions.

delay the MBR is loaded and the MBR\_MAR-H line reset. Since the subtraction method specified calls for inversion of the MBR, the ALU\_FUN(1)-H line is set high to present to the input of the buffer register the inverse of the MBR. This information is then loaded into the buffer register, and the ALU prepared for an addition operation. By also forcing the **Carry** input to be a "I," the final operation is the desired subtraction, and after the required delay the ACC\_LD-H line is asserted to load the information into the accumulator. The *fetch-execute* cycle then repeats itself, beginning with the assertion of the MARLD-H signal.

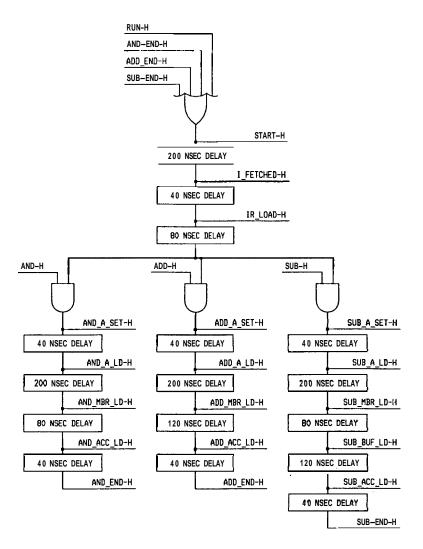

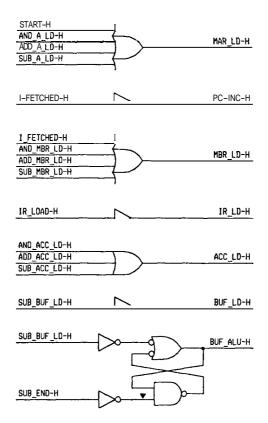

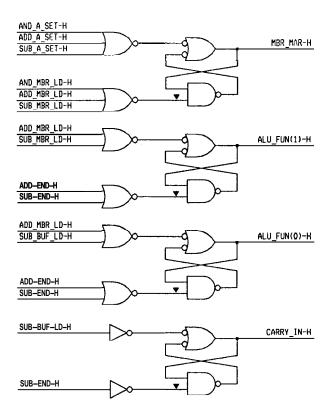

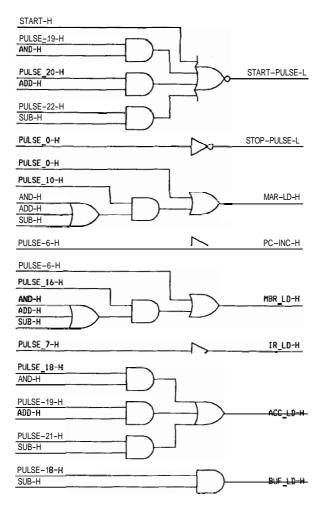

The flow diagram and timing diagram together specify the action to occur and the timing relationship between control signals. The individual delay method of sequencer design consists of directly implementing the flow diagram with delay elements. A delay element consists of either a semiconductor device or an analog equivalent that will accept a signal, usually a pulse, and delay the signal by a preset amount. In this example we need delays of 40 nsec for the register accesses — 80 nsec. 120 nsec. and 200 nsec. With these available. a designer matches the flow diagram with timing elements, and then uses logic gates and flip-flops to create the appropriate control signals. The delay elements for this example are shown in Figure 5.18(a), and the additional logic required is shown in Figure 5.18(b) and Figure 5.18(c).

The system would begin action by injecting into the delay network a single pulse at RUN-H. This would assert START-H, which in turn asserts MAR-LD-H. After a delay of 200 nsec, I\_FETCHED-H is asserted. This causes the assertion of both PC-INC-H and MBR\_LD-H. Another delay element is used to place the required time between the load of the MBR and the assertion of IR\_LOAD-H. The AND gates then direct the pulse down the appropriate set of delays, depending on the instruction decoded. And so the process continues, with the pulse traversing

Figure 5.16(b). (con!) Flow Chart for Delay Implementation of Three Instructions.

the delay network and doing work as required. The control signals are created by tapping the appropriate spots in the delay network, as specified by the flow diagram. For example, ACC\_LD-H is created by ORing the signals from the AND. ADD, or SUB delay sections together. For signals that need to remain set for lengths of time, the flip-flop arrangement shown for MAR\_MBR-H can be used. The signal is set when it is first needed, and then reset when it is no longer needed. This allows both pulses and levels to be used in the system.

The preceding example has shown that systems can be designed in a straightforward manner using delay elements and gates to cause the appropriate action. The data path block diagram identifies the control points that need to be activated, and the flow diagram and timing diagram specify the actions and delays to take place to accomplish the appropriate tasks. This example can easily be extrapolated to include other instructions: the flow diagram will require additional

Figure 5.18(a). Delay Elements Needed for Simple Machine.

branches in the decode section, and additional register transfer level specifications will identify the work required for arithmetic or procedural instructions. For example, not all instructions will require action from the ALU, and other data paths will be required for jumps and other activity.

This method of design has an advantage in that the control can be tuned to provide the fastest action possible. That is, if it is known that the ALU will do an AND action in 38 nsec, then the 38 nsec delay can be placed in the appropriate spot in the system, and the AND instruction will take 2 nsec less than an OR instruction. But offsetting the speed advantages **are** some of the practical problems. The fidelity of the pulse as it travels through the system must be carefully

Figure **5.18(b).** Creation of Control Signals for Delay Method.

maintained, and this can cause additional problems. The system must be carefully designed to prevent spurious pulses from entering the network; an interesting error mode is when two pulses are traversing the system simultaneously.

This method allows a straightforward combination of data path block diagram, flow diagram, and timing information to result in a tunable, high performance control system. The control system provides both pulse and level capabilities, and can be easily modified either by changing the delays or by including other points in the delay network in the creation of control signals. Many of these characteristics are also evident in the shift register method of control design.

#### 5.5. Sequential Systems Using Shift Register Timing

The concepts of the shift register timing method for control design follow closely those of the individual delay method. The data path block diagram is used to identify the control signals, the flow diagram identifies the register transfers and other work that need to **be** done, and the timing diagram specifies the interaction of the control signals required to accomplish the work. However, the timing

Figure 5.18(c). (cont) Creation of Control Signals for Delay Method.

diagram must now represent events that occur at multiples of the system clock. That is, the delays of a flow chart such as Figure 5.16 must all be multiples of the system clock. The preceding example was chosen so that all of the delays were multiples of 40 nsec — so that will be the assumed system clock rate for this section. The concept for the shift register method is to identify the work to be done, and then to create the proper waveforms by using gates to harness a pulse proceeding down a shift register.

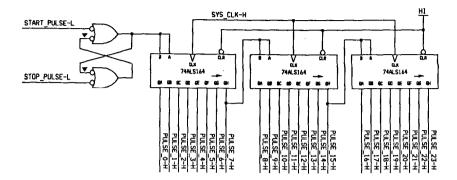

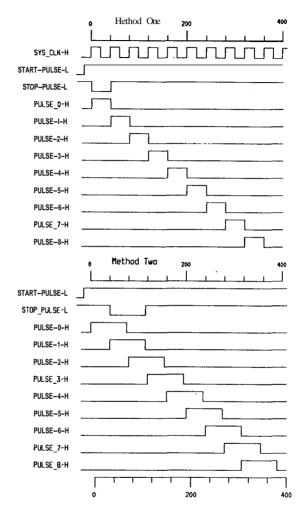

The creation of the timing action is accomplished by the action of a shift register. One such arrangement is shown in Figure 5.19. The desired pulse action is initiated by asserting START-PULSE-L. On the next clock pulse the signal **PULSE\_0-H** will be asserted. If a pulse duration of one cycle is desired, the STOP-PULSE-L control line can be created by inverting **PULSE\_0-H**. Thereafter, on each leading edge of the system clock the pulse "moves" down the shift register. The resulting pattern is shown in Figure 5.20, called Method One. The pulses depicted for Method One form a precise timing capability for the system. If an event is to occur 80 nsec after initiation of the instruction, then **PULSE\_2-H** can be used to cause the event. However, if a control line needs to be asserted for more than one clock period, then more than one time period is needed. That is, if a signal is to be asserted from 80 to **160** nsec after initiation of the instruction,

Figure 5.19. Pulse Creation with Shift Registers.

then the signal can be created by **ORing** PULSE-2-H and PULSE-3-H. This will indeed result in a signal of duration 80 **nsec**; however, there may be a glitch in the signal caused by the timing difference of **deasserting** PULSE-2-H and asserting PULSE-3-H.

One way to get around the problem of glitches on the control lines is to use set-reset **flip-flops** as we did with the delay line method. Another solution to the **problem** is to use overlapping pulses, as shown in Method Two of Figure 5.20. Pulses with a length of two system clock periods can easily be created by using the inverse of PULSE-I-H to be STOP-PULSE-L. When these signals **are ORed** together, the resulting signal is free of glitches caused by the hazards associated with pulse assertion.

The similarities between this method and the individual delay method are apparent from the approaches both take in implementing the control signals. The principal difference is that one method uses individual delays and a pulse that traverses a control network to accomplish work, while the other method achieves the correct timing relationships by the use of measured delays in a shift register. Both methods create the control signals by gating appropriate delayed values with the necessary enable conditions. The result is a system that **asserts** the control signals needed to accomplish the necessary work.

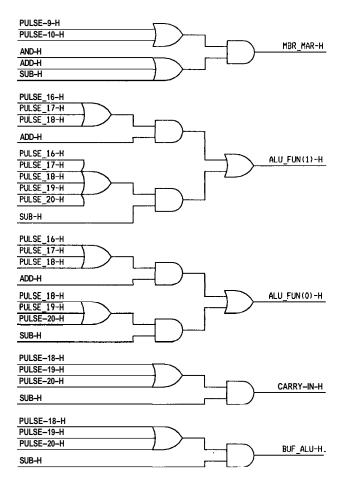

An example of gating for the shift register method for the system of the previous section is given in Figure 5.21. The gates shown are derived directly from the timing and flow diagrams. The MAR-LDH signal is always asserted at PULSE-0 time, or **it** is asserted at PULSE-10 if the instruction is an AND ADD, or **SUBtract** instruction. For this example, this is the entire collection of instructions so the AND and CR gates are superfluous. However, if a number of other instructions were included in the system, then the gates would be needed. The **PC\_INC**-H instruction always occurs at PULSE-6 time, so no additional gating is needed. The **ALU\_FUN(1)-H** signal is asserted during PULSE-16. PULSE-17. or PULSE-18. if the **instruction** is an ADD instruction, or during PULSE-17. PULSE-17, PULSE-IS, PULSE-19, or PULSE-20. if the instruction is a **SUBtract** instruction. It is not asserted during an AND instruction. The other control signals **are** created in a similar fashion. Note that the STOP-PULSE-L signal occurs at PULSE-1 time, resulting in overlapped pulse operation. Also note that the START-PULSE-L

Figure 5.20. Timing Diagrams for the Shift Register Method.

signal occurs at different times for the different instructions, and that initialization comes from some external circuitry.

Both the delay method and the shift register method provide **straightforward** approaches of building control circuitry, mapping the information from the flow and timing diagrams directly into hardware. Both methods allow the designer flexibility to implement the necessary signals to match the constraints of

Figure **5.21**(a). Control Signal Generation with the Shift Register Method.

technology and application. And both methods have interesting error modes when more than one signal enters the delay **network/shift** register. Nonetheless, both of these methods have been utilized in the design of many types of digital equipment. However, perhaps the most extensively utilized control design method in recent years is microcode.

## 5.6. Microcode Controllers: A Regular Control Structure

In 1951 Wilkes presented a paper in which he suggested that the design of control systems was entirely too complicated. He went on to suggest that the process  $c \in \mathbb{N}$  by  $c \in \mathbb{N}$  simplified by the use of a regular method for making decisions

Figure 5.21(b). (cont) Control Signal Generation with the Shift Register Method.

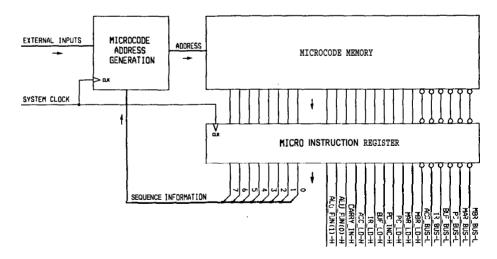

concerning the next thing to do and what control signals to assert. The heart of this method was a high speed memory element needed to remember the appropriate sequence of information. However, at that time the memory technology was not as fast as random logic, nor as readily available. Hence, for **many** years Wilkes' suggestions went unheeded. Instead, designers utilized classical techniques, as well as the delay line and shift register methods, to implement sequential controllers. However, in the mid-1960s memory technology advanced to the point that it was an attractive alternative to use high speed memory to govern the action of a control system. We will introduce the method by taking another look at state machine control, and transfer the state machine ideas to the use of micro-code.

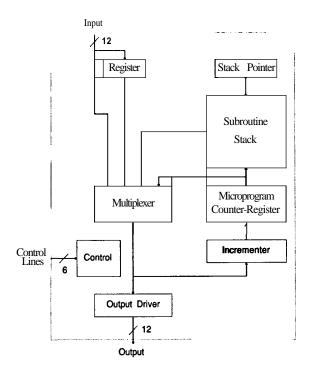

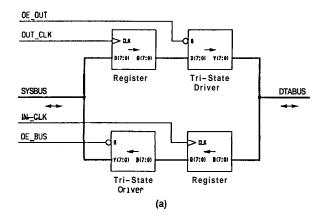

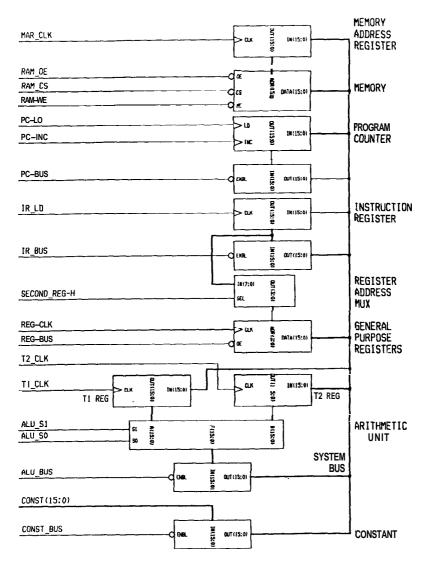

We begin our examination of memory-based control methods by reorganizing the **block** diagram of Figure 5.15. The same basic components are utilized, but the organization is changed. The reason for changing the block diagram will become apparent as we discuss the implementation methods of this section. The **main** organizational change is the inclusion of a single data path that is utilized by all of **the** components. This single bus organization is very useful in systems where universal communication is desirable. Each component can transfer information to any other **component**; however, only one value can be transferred in a clock period. The component required to accomplish this is a bus driver, which isolates the register outputs from the bus except when the information in that particular register is required. At that time, the bus driver is enabled and information from the register is **made** available to the other elements on the bus.

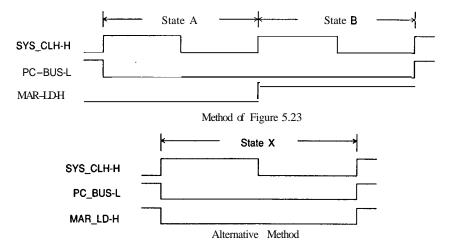

Transferring the contents of the program counter to the memory address register is achieved by asserting PC\_BUS-L to place the contents of the program counter on the bus, and then after a time required for propagation delay, settling time, and setup time, MAR\_LD-H is asserted to load the information into the MAR. One method of implementation is to make the various registers from simple register devices such as the '273, and the drivers from tri-state drivers, such as '244. For situations where the data is not necessary except to drive the bus, such as the buffer register, it is possible to obtain both register and driver in a single package, such as the '574. However, not all registers can take advantage of this capability, since the output of the accumulator is always needed at AIN of the ALU, and the value in the memory address register is required at the memory.

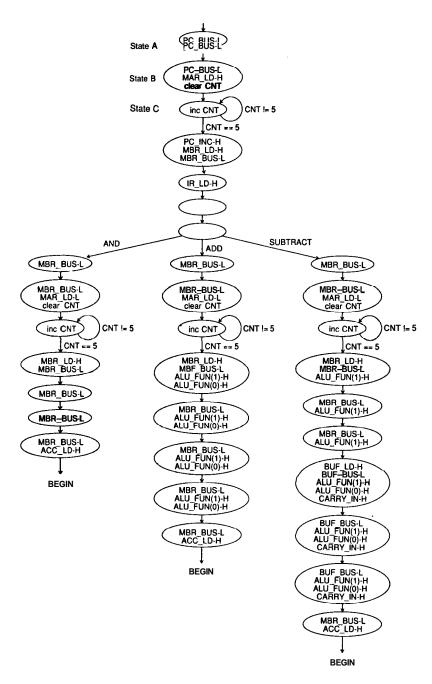

As with the other control implementations, our first requirement is a complete data path block diagram. with control points identified. This is given in Figure 5.22. We can now generate a state diagram that identifies the assertions required in order to accomplish the desired results. These results have already been identified by the flow chart given in Figure 5.16; we can **now generate** a state diagram to do the same work. One such state diagram is given in Figure 5.23. This state diagram illustrates some interesting points, and represents a fairly conservative approach to system design. Let us consider the methods illustrated by Figure 5.23, and then consider some alternatives.

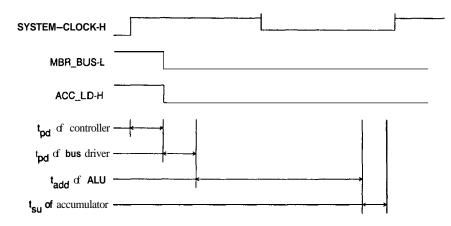

The method used for transferring information across the bus is illustrated in the first two states, which cause the MAR to be loaded with the contents of the PC. In State A the signal PC\_BUS-L is asserted, which causes the contents of the program counter to be placed on the bus. This same signal is asserted in State B, which guarantees that the value will be present during that state also. The loading of the MAR is caused by the assertion of MAR LD-H in State B; this signal causes the register to accept the information while the bus is held steady by the PC-BUS line. The relationship between these signals is shown in Figure 5.24. The method described in the state diagram, and shown pictorially in Figure 5.24, requires two states, and guarantees that the data is loaded into the MAR at the beginning of State **B**. The same work can be accomplished by generating both the **MAR** signal and the PC\_BUS signal simultaneously, as shown in the alternative method. The key to success of this method is that the register is loaded on the rising edge of the MAR-LD line. Thus, for the duration of State X the PC\_BUS signal is causing the data to be placed on the bus, and sufficient time is allotted for the delay in that process, as well as the setup time on the inputs to the MAR. Then when the lowto-high edge occurs on the MAR-LD line at the end of the state, the data available is loaded into the register. For most logic families (LS, ALS, AS, etc.), the delay in turning off the driver is sufficient to guarantee that the data is stable long enough to be correctly loaded into the MAR. This alternative method requires only one state to transfer the information, instead of the two states shown for

Figure 5.22. Block Diagram of Processor with Single Bus Organization.

Figure 5.23. State Diagram for Single Bus Processor.

Figure 5.24. Timing for Loading MAR from PC.

Figure 5.23. One caution with this method of information transfer is that the designer must ascertain that the data has been stable in the loaded register for a sufficiently long period to guarantee desired results for the next operatian. That is, the propagation delay, from clock assertion to data available, **must** be accounted for in any subsequent data manipulation.

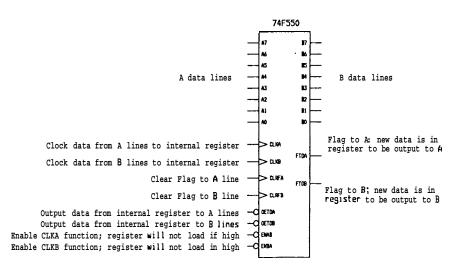

This method is applicable to registers and other edge-triggered devices whose clock lines are driven directly from signals generated by the state machine. Another method to achieve this result is to use devices with separate clock and enable lines. One such device is the 74F550, shown in Figure 5.25. This register

Figure 5.25. Register with Separate Clock and Enable Lines.

has a clock enable control line, which controls the effect of the clock. This allows the clock line to **be** connected directly to the system clock, and then the line that needs to be **asserted** by the control section is the enable line. This is particularly useful for systems in which all events are to happen at precisely the same time, and that time is defined by the rising edge of the system clock. A number of devices utilize this strategy for their operation, including registers (2950, 2952, '550, etc), arithmetic units (2903), and controllers.

Another example of the separate clock/enable function is demonstrated by the use of counters in this system. The 200 nsec delay required by the memory is obtained by waiting for five state times before proceeding. This wait time is governed by a counter similar to those used in the example of Section 5.2. The control design used in that section caused control signals (specifically, clock lines of counters) to be asserted when the action was needed. Another method to achieve the same result is to use counters which will increment only when enabled, even though a clock signal is present at the clock input. The counters will increment only when the enable line is asserted, and the enable line is controlled by the state machine. This is the method which is illustrated in State B and State C of Figure 5.23. The counter is cleared in State B, and then State C calls for incrementing the counter. This cannot be accomplished if the clock signal is fed **directly** from the decode of the state, since the state does not change. (As pointed out earlier, ANDing the clock signal with the system clock would result in a pulsating clock line.) However, if the State C signal is utilized to enable a counter, then the desired result is obtained. For the '161 of Section 5.2. the action can be obtained by using a signal generated in State C to assert the Enable P line of the counters.

Other delays are implemented by repeating the action of one state in another state. The **40**, **80** and **120** nsec delays can be obtained by using one, two, or three states. Thus, delays can either be obtained by staying in one state for a predetermined number of system clock times, or by using multiple states, assuring that the required signals are asserted within those states.

The state diagram of Figure **5.23** is specifically constructed to follow the flow diagram of Figure **5.16**. No attempt has been made to try to save on the number of states utilized. An examination of the state diagram reveals that there are some duplications, specifically in the area of obtaining the operand of the instruction. One method of reducing the number of states would be to delay decoding of the **instruction** until the operand has been obtained. This results in a system that partially decodes instructions at appropriate times to attempt to minimize the number of states. For example, the system under consideration always requires an operand for each instruction, but in a real system instructions such as "increment" or "clear" affect only the accumulator, and do not need to obtain another operand. Thus, the organization of the system all influence the designer in the creation of the state diagram that describes the control algorithms of the system.

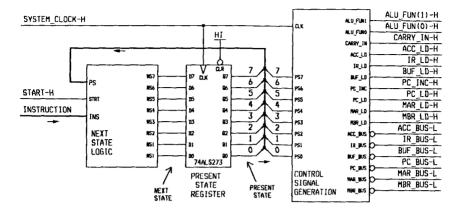

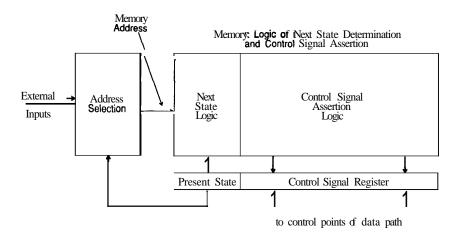

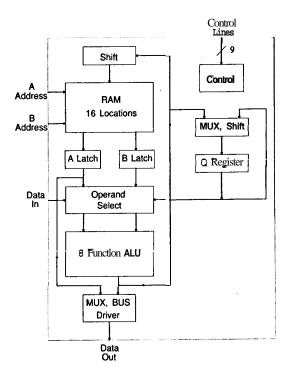

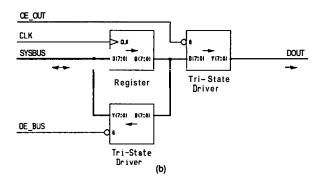

Using classical methods, or those described in Section **5.2**, we can implement a control section that operates as described by the state diagram of Figure **5.23**. A block diagram of such an implementation is shown in Figure **5.26**. The current state of the system is stored in a register labeled "Present State Register." The next state logic uses the current state, the instruction, and the start signal to select the appropriate next state. In the direct implementation method of Section **5.2**, this logic consists of multiplexers and perhaps some **minimal** logic. With classical methods, this would be some type of random logic implementation.

Figure 526. Block Diagram of State Machine Controller for Simple Computer.

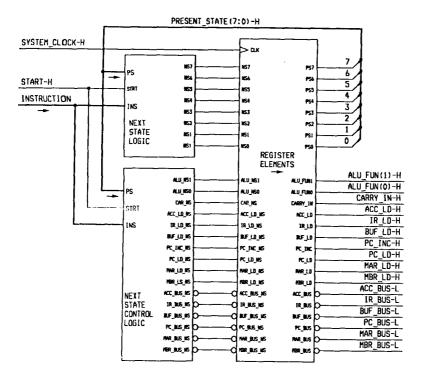

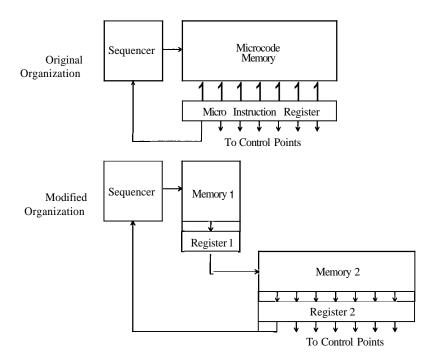

Regardless of the implementation method, every clock period a new determination is made as to the next state, and if the implementation is correct, the state diagram of Figure **5.23** will **be** followed. The control signals are generated by decoding the present state; these signals may or may not include the system clock in their implementation. The following observation can **be** made concerning the control signal generation: the signals asserted at any given time are functions only of the present state (and clock), and the signals to be asserted in any given state are determined during the design process. Since the signal assertions are set up at design time, the same information used to select the appropriate next state (present state and inputs) can also be used to determine the signals that will be asserted at that time. Therefore, during the same period that the next state is determined, the appropriate signal assertions for that state can also be determined. This leads to the implementation shown in Figure **5.27**.

The block diagram of a system controller as shown in Figure **5.27** is extremely simple. The next state logic determines the state to which the system will proceed from the present state, based on the present state and the external inputs. At the same time, this same information will be used by the next state control logic block to determine the control signals to be asserted in the next state. As stated earlier, this information is available at design time, and will not change during the useful life of the product. Both the state infonnation and the control lines will be held in registers, so that transitions on control signals will occur at the same time that the state changes. If it is deemed desirable to do so, some control signals can be conditioned with the clock to create appropriate timing pulses. This arrangement eliminates the use of a present state decoder for generation of control signals, since all of the signal generation is determined prior to the active edge of the clock.

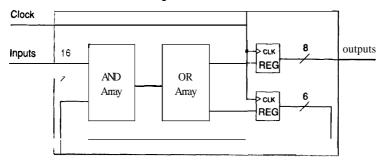

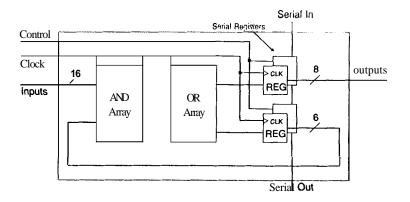

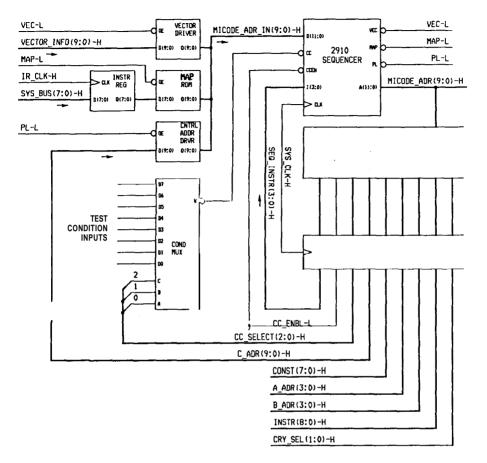

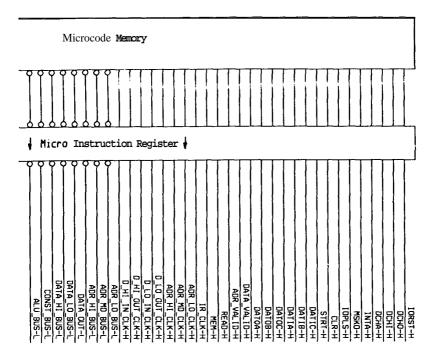

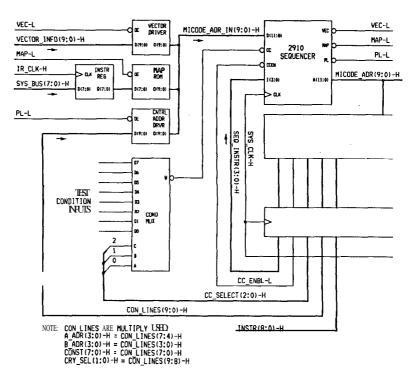

The logic utilized by a system for the **ncxt** state logic and next state control logic blocks can be created by any appropriate means open to a designer. But it is instructive to note that it need not be random logic nor the multiplexer arrangement presented earlier. Some manufacturers build devices specifically designed to do this function, and they provide means to create the appropriate logic, depending on the mechanism used for implementation of the device. Figure **5.28** shows a block diagram representation of the 82S105, which is called a "Field

Figure 5.27. Block Diagram of State Machine Controller Combining Generation of Next State and Control Signals.

Figure 5.28. Internal Makeup of a Field Programmable Logic Sequencer

Programmable Logic Sequencer." This device allows 16 external inputs; in addition there is a **reset/output** enable line (function is defined at time of programming). The device has eight outputs, all of which are registered so that the outputs will change only after a clock transition. Internal to the device are six feedback lines; this allows creation of a state machine with up to 64 states. The determination of **the** next state and the output levels is accomplished by a programmable AND/OR array; the limitation is that the device is capable of only 48 AND terms and 14 OR terms. This places some limits to the complexity of the state machines that can be implemented by the device, but a variety of very useful controllers is feasible. A large number of similar devices can be utilized to implement sequencers, such as registered PALs, state machine controllers, and registered PLAs.

One "feature" of this type of unit is **that** the feedback variables are internal to the device. This is a benefit in that the speed is not hampered by going off chip, which leads to a higher clock rate. Note that the inputs will need to be synchronized to the system in some way. The drawback to this feature is that the state variables are not available to the user to aid in the debug process. Thus, the only way to ascertain the state of the machine is to observe the output pins. The designer must be careful about his assumptions concerning the correctness of the machine during checkout. Nevertheless, programming aids. available from both manufacturers and third party vendors, greatly **enhance** the ability of the designer to create a correct system.