# Input and Output Operations

We have discussed several of the characteristics attributed to a machine. including the methods of information representation and the instruction set. We have also discused methods of designing the functional elements, such as the arithmetic unit or the control unit. But it is not sufficient to compute; the results of the computation must be made available to other systems. These systems may be other computers, computer peripherals. or similar devices. Eventually, the information may need to be **presented** in a form easily understood by humans; many interface systems **convert** information not only into readable text, but also graphic images. **synthesized** sound, or **some other** suitable **form.**

The term "input" is attached to the process of transferring information into the computer, and "output" to the transfer of information out of the machine. When both are possible, it is simply "LO." In this chapter we will discuss the methods used to perform these transfers, some of which we have already alluded to in the consideration of instruction sets. This will include mechanisms used for asynchronous and synchronous bus transfers, time multiplexing of information on buses, and so on. We will also consider arbitration techniques, which decide who is the "owner" of a bus when a transfer is made. And we will include both programmed control and direct memory transfers to move information. Included with the discussions are a number of examples that illustrate the concepts and techniques. Once the ideas are understood at both the conceptual and implementation level. I/O systems and interface modules can be more easily designed and understood.

The instruction set architecture of a machine will determine the apparent organization of the I/O system. That is, the mechanisms envisioned for system I/O will be one of the factors considered in the process of the creation of the instruction set of the system. In many respects, the computer system will be judged by its ability to coordinate information transfer in a reasonable fashion. A more comprehensive view of the total system impact is obtained by considering computer system performance from a systems aspect, taking into account the characteristics of the CPU, the peripheral devices, and the transfer mechanisms. (See, for example, [LaZa84].) Our intention is to understand the principles utilized in the transfer mechanisms.

# 6.1. Asynchronous Bus Transfers

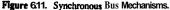

The block diagram of Figure 6.1 indicates that a number of functional units can exchange information over a common communication medium: the bus. The transfer of information will begin when one of the modules recognizes a need to communicate with another module. This need will result from any of a number of mechanisms, such as a processor module that must obtain the status of an interface module, or an I/O module that must transfer information into system memory. If a module has the ability to control the bus, we call it a "bus master." In general, there will be several bus masters in a bus-oriented system. When a master needs to transfer information, it will request ownership of the bus. The process of allocating control of the bus to a bus master is called arbitration, and we will discuss arbitration mechanisms in a later section. When a master has obtained **control** over the bus, it then initiates a bus transfer by activating the appropriate lines. The module activated by this transaction (the one that responds to the master) is called the "bus slave." The set of rules or algorithm utilized in this process is called the "bus communication protocol." This protocol will identify the sequence of events to occur in the process of transferring information, and specify the timing requirements of the transfer.

In this section we will discuss the exchange of information over the lines assuming an asynchronous protocol. That is, the modules of the bus system do not share a common clock, and the transfer **proceeds** in an asynchronous manner. In the communication process, the master and the slave assert signals on common communication lines in a predetermined manner so that the transfer can proceed. We will assume that the **arbitration** process has been completed and that the **mas**ter is in **control** of the bus. **The** master is now capable of initiating the transfer. and will do so by activating the appropriate bus lines according to the defined protocol. **The** bus lines (except power and ground, which **are** also distributed along the **bus**) belong to one of three groups: address, **data**, or control, as shown in **Figure** 6.2.

The address **lines are used** to identify the target of the transaction. That is, the **master** places an address onto **the** address lines that will uniquely identify the location to be used for the transfer. The number of address lines that can be used for this function **determine** the number of addressable locations, since N lines **are** capable of selecting one of  $2^N$  locations. This address is the only mechanism the master has to identify the target module. All of the modules that can respond to addresses to perform transfers **are connected** to the address bus, and they receive

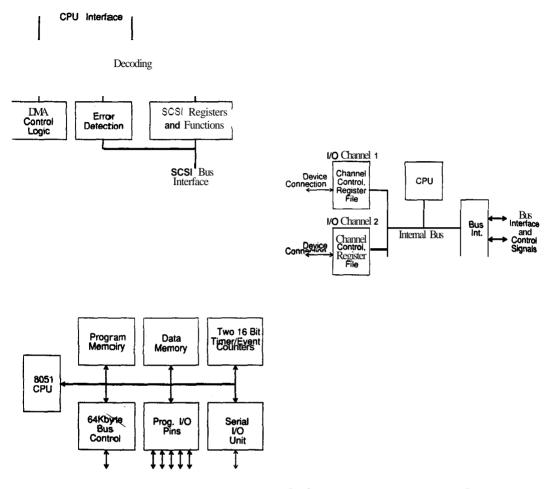

Figure 6.1. Module Organization for Bused Systems.

**Figure** 62. Bus Lines Connecting the Master and the Slave.

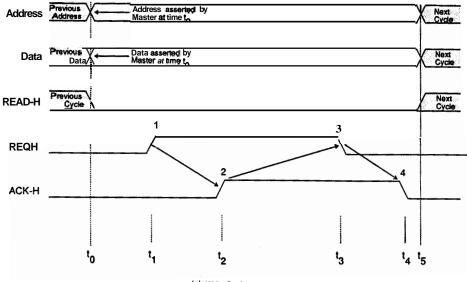

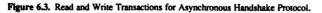

this address and compare it to their assigned address space. The address should identify only one module: if more than one module recognizes the address. the transaction will not function properly. (As usual, there are exceptions to this rule, which we will note later.) Once a master has initiated a transfer, it will allow a predetermined amount of time for the address comparisons, then proceed with the transaction. The slave module with an assigned address matching the target address will respond to the master, and the transaction will proceed governed by the assertion of the control lines. The control lines are used to synchronize the action between the master and the slave modules. The mechanism for this is shown in Figure 6.3. This figure shows the address lines as a group, the data lines as a group, and three of the control lines. A number of other control lines will he involved with the arbitration mechanism, but for this discussion we will limit ourselves to the three control lines identitied in the figure: READ-H. REO-H. and ACK-H. The READ-H line identifies a read transaction when it is asserted. That is. when it is high, the master module is reading a location fmm the slave module. When the READ-H line is not asserted (when it is low), the master module is writing to the slave module. The READ-H line has the same timing requirements as the address lines, which are explained in conjunction with the other control lines.

The two lines that control the timing and sequence of the events involved in the transaction are the request line (REQ-H) and the acknowledge line (ACK-H). The write cycle proceeds as shown in Figure 6.3(a). The master, which has already obtained control of the bus, asserts the address of the desired location. This time is identified as  $t_0$  in the figure. A finite time is required for this address to propagate to all of the slave modules and be decoded by them. so the master must wait for a specific period before asserting the request line. The amount of time required is a function of the technology in which the hardware is implemented, and the physical and electrical characteristics of the bus. When the required time period has passed, the master asserts the request line (time  $t_1$ ). This is then accepted by all of the slave modules, but only the module with the matching address will respond. When the slave has performed the requested action, which in this case is to accept the data on the data lines, the slave module asserts the acknowledge line (time t<sub>2</sub>). When the master detects the assertion of the acknowledge line. it recognizes that the **work** of the transaction has been completed. So it releases the request line (time t<sub>3</sub>), and when the slave detects the release of the request line, it releases the acknowledge line (time t<sub>4</sub>). The master must keep the address lines asserted after the release of the request line to prevent any spurious action that may occur if the address changes before the release of the request

(a) Write Cycle

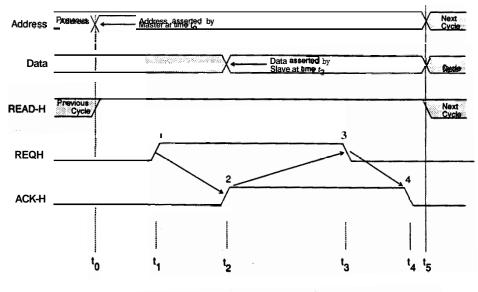

(b) Read Cycle

line has propagated through the decode logic of the slave modules. This may be accomplished by holding the address lines for a specific time after the release of the request signal, or until the master detects the release of the acknowledge by the slave module. This mechanism is sometimes called the four event **bus** transfer. since four events  $(1 \rightarrow 2 \rightarrow 3 \rightarrow 4$  in Figure 6.2) are involved in performing the transfer.

The read transaction is almost identical to the write, and the appropriate lines are shown in Figure 6.3(b). The major differences are that the read control line is asserted and that the data is now asserted by the slave module. The master begins the transaction as before, by asserting the address and waiting the necessary time for propagation delay and skew. Even though the master may assert all of the address lines simultaneously, they will not all arrive at the decoder of the slave modules simultaneously, since the electrical characteristics of the bus and the propagation delays of the address lines may be different from one another. The time difference from the arrival of the first signal to the arrival of the last signal is called the skew time, and the bus protocol must include a sufficient time delay to account for the maximum expected skew time of the bus. When the master has allowed time for propagation delay and skew, it then asserts the request line (time t<sub>1</sub>), asking the addressed slave to provide the information. The addressed slave module performs whatever action is required to obtain the data: if it is a memory device this will require a memory cycle, but if it is an interface module the information may be readily available. When the data has been obtained, the slave module asserts the data onto the data bus, as well as asserting the acknowledge line (time to). At this point the master must wait for a period of time to allow for skew, then it accepts the data and releases the request line (time (t<sub>a</sub>). When the slave detects the release of the request line, it releases the acknowledge line. Some time after the release of the request line, the master is free to release the address.

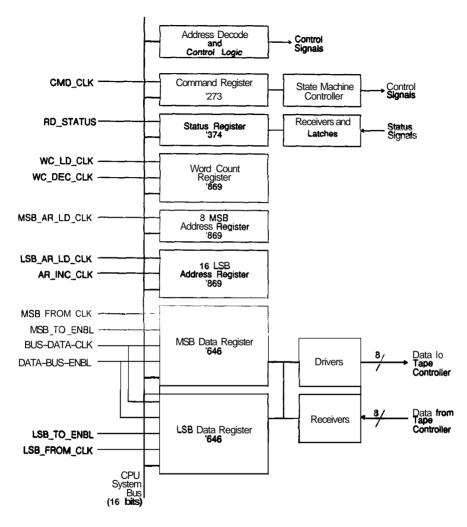

This basic asynchronous communication protocol is used by a number of different microprocessors and minicomputers. It has the advantage of not needing a specific clock, since the transaction proceeds according to the signals asserted by each module. Since the modules can proceed as fast as their functions allow, the transactions can **proceed** as fast as data is available. The **drawback** is that the built-in delays, needed to allow for signal skew and **propagation** delay, force a relatively long minimum cycle time. For the **UNTEUS**, which is the bus on which the Digital Equipment Corporation PDP11 series is based, a typical minimum cycle time is 400 ns. Nevertheless, because of its simplicity and **ease** of function, the asynchmous bus protocol is used extensively. One example is the Multibus, which originated with some products from Intel.

**Example 6.1:** Asynchronous protocol: The Multibus is an asynchronous protocol that fits the discussion above. What **are** the signal and control lines utilized by the Multibus, and the associated delays?

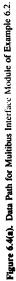

The asynchronous **protocol**, as described in the above paragraphs and in Figure 6.3, is **directly** applicable to the Multibus, with a few modifications in nomenclature. The signals on the Multibus **are** all asserted low, so **the** address, data. and control lines have a low voltage for a "1" and a high voltage for a "0." Then **are** 20 address lines and 16 data lines, which gives an **addressable** space of one megabyte. The address lines **are** used for both 1/O and memory addresses. After a master has asserted the address, it waits for 50 **nsec** before, asserting the request line; this is the time allowed for skew and delay. The appropriate request line is asserted low (as opposed to the high assertion shown in Figure 6.3). Instead of having a read line to identify the direction of the transfer, the Multibus has separate request lines for memory read (MRDC-L), memory write (MWTC-L), I/O read (IORC-L), and I/O write (IOWC-L). This allows the address lines to be used by memory and I/O devices, and the appropriate interface module will respond only when the necessary control line is asserted. When a slave module responds, regardless of the request line that activated the module, it will assert a transfer acknowledge signal (XACK-L), in the manner shown in Figure 6.3.

**Example 6.2: Interface to asynchronous system:** Assume that a floating point multiplier is to be interfaced to the Multibus in the I/O space. This multiplier requires two 32-bit words to be available, one in Register X and one in Register Y. Design an interface module for the Multibus that will read and write to Register X and Register Y, and also cause the multiply to occur when accessed. Assume that the multiply process will take a variable amount of time depending on the data. and that the multiplier will assert a DONE signal when the answer is available.

The Multibus protocol allows 16-bit bus masters to address 4.0% different I/O locations, so we will assume that the floating point multiplier in question is to occupy the following addresses:

| Address           | Request Line | Action                               |

|-------------------|--------------|--------------------------------------|

| DF0,              | IOWC-L       | Write to Register X (low 16 bits).   |

|                   | IORC-L       | Read from Register X (low 16 bits).  |

| DFI <sub>16</sub> | IOWC-L       | Write to Register X (high 16 bits).  |

| DF1 <sub>16</sub> | IORC-L       | Read from Register X (high 16 bits). |

| DF216             | <b>IOWCL</b> | Write to Register Y (low 16 bits).   |

| DF2 16            | IORC-L       | Read from Register Y (low 16 bits).  |

| DF316             | IOWC:L       | Write to Register Y (high 16 bits).  |

| DF316             | IORC-L       | Read from Register Y (high 16 bits). |

| DF416             | IORC-L       | Read from Result (low 16 bits).      |

| DF516             | IORC-L       | Read from Result (high 16 bits).     |

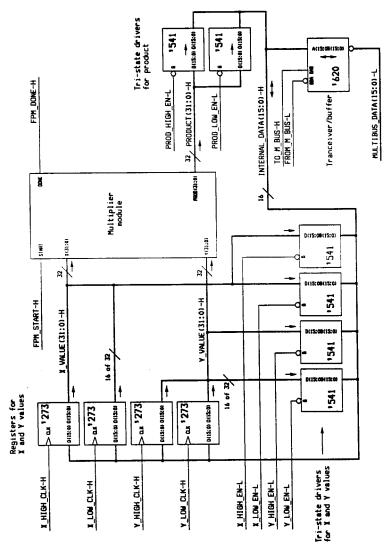

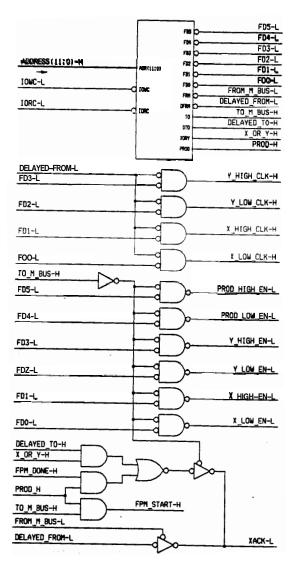

The design of this system is relatively straightforward, since the logic is basically combinational in nature. The only timing requirements are those imposed by the bus protocol, and the sequentiality of action defined by the protocol is also enforced by the master. The data path for this interface module is shown in Figure 6.4(a). The registers are made up of positive edge triggered devices ('273s), which hold the information for the floating point multiplier. Note that for this system an inverting bus transceiver has been inserted into the data path. This has the benefit of presenting only one electrical load to the data bus, but incurs the penalty of an additional delay, which needs to be included in the design process. Many multipliers have registers built in, so in one sense the external registers are redundant. However, the specification indicates that these values should also be made available to the bus upon request, so the registers are needed to provide that capability. Tri-state drivers ('541s) are used to send the information to the internal data bus, which is enabled onto the Multibus data lines by the tran**sceiver.** This path is also **used** by the product **from the** multiplier.

The control signals used for this system arc derived by the logic shown in Figure 6.4(b). The address lines arc checked for a proper address pattern. However, since the address pattern could be asserted for memory addresses as well as the I/O addresses needed for this system, no action is

Figure 6.4(b). Control Signals for Multibus Interface Module of Example 6.2.

taken until the I/O request lines are asserted. If the transaction is a write to the X or Y register, then the Multibus data lines are enabled onto the internal data bus (with FROM\_M\_BUS-L), and after a delay to allow the data to propagate to the registers, the appropriate clock line is asserted. Figure 6.4(b) does not indicate how this delay is obtained. but a number of different methods could be utilized, from a targed delay line to a synchronous method using the clock provided on the Multibus. The slave response to the I/O request lines is through the acknowledge (XACK-L), which is seized when the address is recognized, but not asserted until the transaction is complete. For filling the X and Y registers the acknowledge will be asserted when the delay has been completed. Similarly, reading the X or Y registers, or the lower bits of the product, involves a delay to allow the data to propagate onto the internal data bus and then to the Multibus data lines. When a propagation delay time has been accounted for. then the acknowledge can be asserted. Requesting the higher bits of the product causes a multiply to occur. so the acknowledge is asserted when the done signal is asserted by the multiplier. This necessitates that the most significant word of the product be requested first to achieve proper results.

The Multibus. and many other buses that use the asynchronous handshaking technique to transfer **information**, can be effectively utilized to pass data in a single bus environment. However, the lines required to perform this type of transfer are rather numerous. The Multibus utilizes 41 lines to perform these transfers, and the UNIBUS uses 38 lines. One of the ways to reduce the number of wires required is to time multiplex the address and data lines. That is, one set of lines contains the address for part of the time and data for another part; the information content of the lines is determined by the control signals. **Thus**, the total number of wires required to perform transfers is reduced. The **tradeoff** is between the number of wires on the bus (or pins on the integrated circuit, or on the edge of the board, or ...) and the **increased** time required to perform the runsfer. Since the lines will increase. Nevertheless, the total number of wires is decreased, and the speed of the bus is sufficient for many applications.

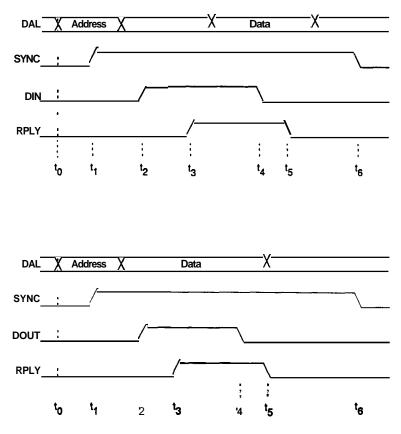

**Example 63:** Time multiplexed asynchronous protocol: Digital Equipment Corporation has built a number of devices based on a protocol and physical configuration called the Q-Bus. This is a time multiplexed data/address bus with an asynchronous protocol. What is the sequence of events involved in performing a read and a write with the Q-Bus?

The waveforms for the transfers of the Q-Bus are shown in Figure 6.5. This is an abbreviated version, since there are control lines to indicate when a transfer is in the 1/0 page, when it is a byte transfer, and so on. But the basic principles are demonstrated by the figure. The levels indicated in the figure are logical levels only, since the assertion level of the signals on the bus itself is negative, so that on the bus a "1" is indicated by a low voltage level. The read cycle [Figure 6.5(a)] begins with the master asserting the address on the time multiplexed data/address lines (DAL), then allowing a time for propagation delay and skew. The SYNC 1 i e is then asserted (time t<sub>1</sub>), which is used by slave devices to latch the address information as needed. The master releases the DAL lies, and at time t<sub>2</sub> asserts DIN, which indicates to the addressed slave that the transaction is a read. From this point the transaction follows the four event sequence, with DIN

Figure 6.5. Read and Virite Cycles on a Time Multiplexed Bus: (a) Read Cycle; (b) Virite Cycle.

representing the request line, t<sub>3</sub>), and then within 125 nsec asserts the data. The master responds by releasing DIN (time t<sub>4</sub>). When the slave detects **the** release of **DIN**, it releases RPLY (lime t<sub>5</sub>), and then releases the DAL lines. The last event in the cycle is the **release** of the SYNC signal by the master in preparation for the next cycle.

The write cycle shown in Figure 6.5(b) is very similar to the above sequence of events. The major difference is the assertion of the data on the DAL lines by the master after the address has been issued and synchronized by the SYNC signal. Once again, the four event cycle mechanism is used. The master identifies the cycle as a write cycle by asserting DOUT. The slave accepts the data and asserts RPLY. The master then releases DOUT. Which allows the slave to release RPLY. The bus protocol calls fat the master to hold the data on the DAL hes for at least 175 nsec after releasing DOUT. And as before, the termination of the cycle is indicated by releasing SYNC

The asynchronous method for information **transfer** can be very useful for exchanging data in time multiplexed systems and in systems with dedicated address and data lines. It is simple to comprehend, and interface modules between the bus and external devices can be designed and **constructed** in a relatively easy manner. The absence of a clock allows the transaction to proceed at the rate at which data (and address) information is available. Nevertheless, the data rates for this type of transfer **are** in general not as high as those for a synchronous protocol. Before we discuss the reasons for this, let's examine some of the arbitration mechanisms used to identify the module that will control the bus transaction.

# 6.2. Arbitration Mechanisms

In any system with multiple master modules, that is, modules that can assert the control lines on the bus, a mechanism must **be** provided for arbitration. Using some predefined priority algorithm, this mechanism must uniquely identify the module that will take charge of **the** bus for the next transfer. It is possible to have this decision follow each bus cycle, so that there is an arbitration between each bus transfer. But in general the arbitration process is performed in parallel with data transfers. So that during the current transfer arbitration is being performed for the next transfer. In this section we will consider arbitration mechanisms and how they can be utilized to assure that control is passed to the proper module.

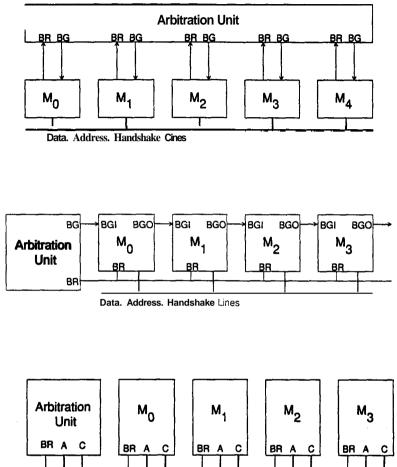

Three basic mechanisms can be utilized for making the decision as to the proper module to control the bus for the next cycle. These **are** shown in Figure 6.6. In each case, the masters  $(M_1, M_2, ...)$  request access to the **bus** by asserting a bus request (BR). When the arbitration mechanism is ready to select a new master module to control the bus, it will assert the bus grant signal (BG) associated with that module. The behavior of the devices receiving the bus grant depends on the **type** of arbitration mechanism involved, as we shall see. When a device needs access to the **bus** and it detects that the bus grant line has **been** asserted, then it will be the next to receive control of the bus. If more than **one** master requests ownership of the bus at the same time, then the arbitration process selects one. and the remaining modules must wait until a later time for their respective transfers.

The fastest arbitration mechanism is the parallel system. In this system each master module has a dedicated connection to the arbitration unit, and when a master module needs control of the bus it will assert its assigned bus request line. The arbitration unit then has the responsibility of dealing with the system in some predetermined fashion. That is, the algorithm utilized in the design of the arbitration unit is not limited by the interconnection system. The **arbitration** can be done **on** the basis of first-asserted/first-served, round robin, assigned priority levels, or whatever mechanism is determined in the design process. Thus, this mechanism allows a variety of possibilities, from extremely simple to extremely complex.

In the parallel scheme, when the arbitration unit has determined that a master module has priority and should have control of the bus, it asserts the bus grant line associated with that master module. This module can then **control** the transfers on the bus. The data, address, and handshake lines are controlled by the selected master, and when the master no longer requires access to the bus, it will release the bus request signal. The parallel arbitration system is then free to allow other master modules to gain access to the bus.

Data. Address. Handshake Lines

The details of the transfer mechanism will vary with each implementation. but the parallel mechanism provides the highest speed of arbitration. The cost for this speed is the additional lines required to allow each possible master direct access to the arbitration unit, and the hardware costs associated with whatever arbitration algorithm is implemented. The number of lines required could be extensive, needing two lines for each module as shown in the following example.

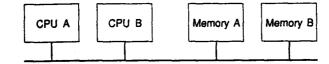

Figure 6.6. Bus Arbitration Mechanism.

Another mechanism would need only one line per module, as we will see later.

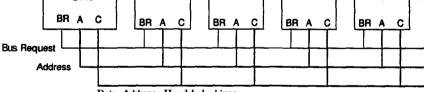

**Example 6.4:** Parallel arbitration system: Design a parallel arbitration system that will allow up to eight bus masters to access a common set of **control** lines. The assumed mechanism for master-slave data exchange is the four event handshake that has been discussed. If no bus master has control of the bus, then the requests are to be synchronized by an internal 10 MHz clock. If a master module has control of the common handshake lines, then the requests are synchronized on the trailing edge of REQ-H.

This type of a system can be easily constructed with a priority encoder and a decoder, such as shown in Figure 6.7. Notice that the assertion levels are low in this example. When no request is pending for the bus (no bus master requires use of the bus) the decoder is disabled, and no master has control. The requests for access are synchronized by a 10 MHz clock, and when one of the masters has made a request for the bus, the appropriate bus grant line will be asserted. If more than one module has requested the bus. then only the highest priority bus grant line will be asserted. Note that the nature of the '148 priority encoder, with its asserted low outputs, inverts the normal order on the decoder **outputs**.

The desired behavior, as defined above, is that the synchronization of requests take place on the trailing edge of REQ when the bus is being used by a bus master. The gates on the input of the clock of the synchronizing register multiplex between the 10 MHz clock and the bus request to allow this to happen. This simple mechanism is. In general not sufficient, since it does not preclude the possibility of glitches occurring on the clock line. (What additional gating is required to assure that no glitches occur?)

The example demonstrates the simplicity with which parallel systems can be **constructed**. However, more exotic priority algorithms. such as first-asserted first-serviced. will lead to more complex implementations. But because of **the speed** with which arbitration can proceed in this **case**. systems that need the performance will **provide** the lines necessary to **allow** parallel **arbitration**. Because of

Figure 67. Simple Parallel Arbitration System.

the need to have dedicated lines to the master modules for **parallel** arbitration, the number of allowable masters on any system is fixed at the time of implementation. This places a fixed limit on the number of allowable masters. and the system cannot be expanded beyond that limit in a parallel fashion. Expansion is **cne** of **the** benefits of the next type of system to be considered, the serial arbitration system.

Serial arbitration is a technique in which the bus grant lines of the bus masters are connected together in a serial fashion, as shown in Figure 6.6(b). There is a single bus quest line, which is connected to all bus masters. The arbitration unit is not aware of which bus master needs access to the bus, and so the arbitration mechanism is simplified to asserting the bus grant signal at the proper time in the bus cycle. The arbitration unit is then responsible for examining the lines controlling the transfers on the bus and deciding when control of the bus can be given to a new master module. When the bus can be controlled by a new module, the arbitration unit asserts a single bus grant line connected to the first module. Since this module is the first to receive the bus grant signal, it has the highest priority: a device can receive the bus grant signal only if the modules between it and the arbitration unit do not need the bus. Because of this connection method, where one module passes the signal on to another in a serial fashion, this is referred to a "daisy chain" mechanism. And because of its serial nature, there is no limit to the number of devices that can be connected in this manner. However, each additional device results in a longer maximum arbitration time.

The serial mechanism for bus arbitration needs at least three lines to function, although more can he used, as indicated by the example below. The three lines are hus request, bus grant in, and hus grant out. A master module indicates that it needs to access the bus by asserting a common request line, as shown in the **figure**. This line is implemented in open collector technology, or some other method that will allow multiple units to assert the signal simultaneously. The arbitration unit uses this signal to identify when a new bus master needs access to the bus, as described above. When the arbitration unit determines that a different module can control the bus, it asserts the bus grant line. Each master receives the grant signal on its bus grant in line, and if the module does not need to access the bus, it asserts the bus grant out line. In this way the assertion of the bus grant signal is passed from one module to another, until it arrives at a module which needs access to the bus. This module **does** not assert the bus grant out line, but rather assumes ownership of the bus and performs the needed transfer. A master module of lower priority that needs access to the bus will continue to assert the quest line, and at a later time a new bus grant signal will be asserted by the arbitration unit and passed to it.

The priority scheme of this system is strictly physical: devices of higher priority are physically (and hence electrically)closer to the **arbitration** unit. Devices of lower priority are farther away from the arbitration unit. The number of devices included has a **direct** effect on the speed of the function. Since each device must check the bus grant signal in a serial fashion, **the** total time for the arbitration function is proportional to the number of devices on the bus. Of course, the closer the device is to the arbitration unit (fewer modules in between), the faster the operation. But since each module requires time to complete **the** bus grant in to bus grant out sequence, there is a **practical** limit to the number of devices that can be utilized.

Because of the serial nature of the arbitration process, care must be taken to avoid the situation where two masters access the bus simultaneously. This

possibility will arise in systems in which the modules operate asynchronously with respect to each other and to the transactions taking place on the bus. In this **case**, a module could q u i r e access to the bus **directly** after the bus grant out signal had been asserted to inform the next module in the chain that it can access the **bus**. If the first module is allowed to immediately command the bus and release the bus grant out line, then both units could be in a situation where they **are**. **accessing** the bus. A practical solution to this **problem** is to design the units to be **edge** sensitive rather than level sensitive. That is, the master modules would be capable of taking ownership of the bus only when the bus grant signal is changed from its unasserted to its asserted level. Thereafter, the unit must wait until the next assertion of the signal, even though it is currently asserted. This mechanism will prevent more than one module from assuming control simultaneously.

**Example 65:** Serial arbitration system: The UNIBUS uses serial arbitration to identify bus master modules that need access to the bus. What **are** the lines involved in this arbitration process, and how does the protocol function? Also, what **circuitry** is need to connect to the arbitration lines to properly utilize the serial arbitration lines?

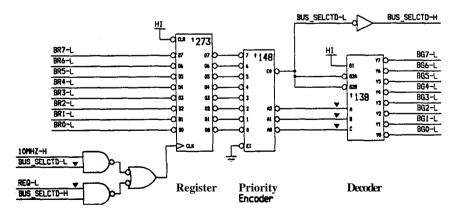

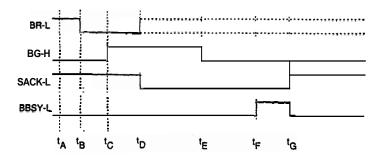

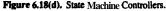

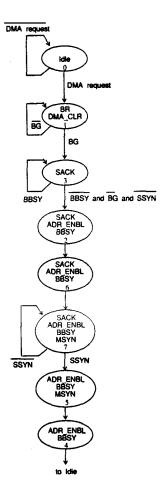

A number of lines in the UNIBUS are used by the master modules to control access to the bus. For the purposes of understanding the mechanism, we need consider only four signals: BR-L (bus request, asserted low), BG-H (bus grant, asserted high), SACK-L (selection acknowledge. asserted low), and BBSY-L (bus busy. asserted low). These lines and the relationship between them are shown in Figure 6.8. The sequence of events begins at t<sub>A</sub>, when the bus arbitration unit recognizes that a new arbitration cycle can begin. since SACK is nor asserted. When a master module needs to transfer information over the bus, it will signal the arbitration unit by asserting the **BR** line  $(t_{\mathbf{R}})$ . The arbitration unit will then respond by asserting BG  $(t_{\mathbf{C}})$ . Some time later (t<sub>n</sub>), the bus grant signal will be received at the master module; there may be other master modules through which this signal has passed to reach the module that requested the transaction. When the bus grant signal is received by the module needing the bus, it will not pass the signal **on**, and it **will assert SACK**. This signals the arbitration unit that the arbitration process was successful, and it can now release the bus grant signal. At the same time. BR will be released by the module, but this will not necessarily mean that the line will return to its unasserted level, since another master module may also be asserting the request line. When the arbitration unit receives the assertion of SACK, it releases BG (tr.). The actual arbitration process is now complete, but the bus is still being used by a different module. When the current bus master completes its cycle, it will release BBSY (tr), signaling the next bus master that it has completed its operation. The new bus master will wait for SSYN (not shown) to be released, indicating that the slave involved in the last transfer is idle, and BG to be released. At that time it will be able to **control** the transactions on the bus. The new bus master will then assert **BBSY** to signal the fact that it is controlling the bus, and relase SACK, to allow the arbitration process to select a new bus master.

A logic diagram of an system that does this is shown in Figure 69. The gates receiving bus signals (RCV) and drive bus lines (DRV) have special electrical characteristics that minimize the electrical loads placed on the bus. Otherwise, the gates have the normal NAND or NOR function shown by the shape of the gate.

Figure 68. UNIBUS Bus Arbitration Lines.

Figure 6.9. Logic for UNIBUS Bus Request-Bus Grant

The UNIBUS protocol was chosen for this example for three reasons. First a great number of devices have been built to interface with the UNIBUS, and so for sheer numbers this is a very prolific mechanism. Second, this example demonstrates that the arbitration process can proceed in parallel with the transfer currently in **progress**. Many asynchronous buses **require** that **the current** transaction terminate before arbitrating for ownership of the **bus**. And third, the mechanism described here is utilized in **one form or** another by almost all asynchronous bus arbitration systems.

The protocol **described** in Example 6.5 is similar to many schemes **that use** the daisy chain **method** of arbitration. **One** of the problems that **can** arise with this mechanism is **the** transfer of control from one master to another. Although the arbitration system **can** select a bus master to assume control of the **bus**, the actual transfer of control will not occur until the **current bus** master **releases the**

**BBSY** line. Therefore, a bus master may control the bus for an extended period of time, not allowing other modules access for transfers. In that sense, the **protocol** is not "fair," and may not be applicable in some circumstances. To prevent this type of device lockout, schemes can force the system to arbitrate for every transfer, **instead** of arbitrating for ownership. Or a a mechanism may be included that will force a module to relinquish ownership of the bus and allow the arbitration process to find a new bus master.

The use of one kind of bus arbitration does not exclude the use of another. The UNIBUS uses parallel arbitration in combination with serial arbitration, as does the VME bus. Parallel arbitration occurs in the UNIBUS because there are five sets of **BR-BG** lines, each of which has a different priority. The access to the bus between these five sets is done in a parallel fashion. Each of the five sets of **BR-BG** lines is a serial line, and operates as described in the example above.

The final bus arbitration technique we **are** going to mention is polling, which is shown in Figure 6.6(c). Here each master module has access to a common request line, which it will assert when it requires access to the common resources. The arbitration unit must then decide which of all of the possible modules made the request. It does this by placing the address of a master module on the address lines and querying each in turn, until it finds the highest priority module needing the bus. This method has the benefit that any priority scheme can be implemented — FIFO, round robin, and so on. But the cost of the mechanism is large in time requirements. For that reason it is almost never used for arbitration of bus lines, but it does find application in the arbitration of I/O requests. That is, a processor, under program control, will poll I/O devices to ascertain the module requesting an Interrupt.

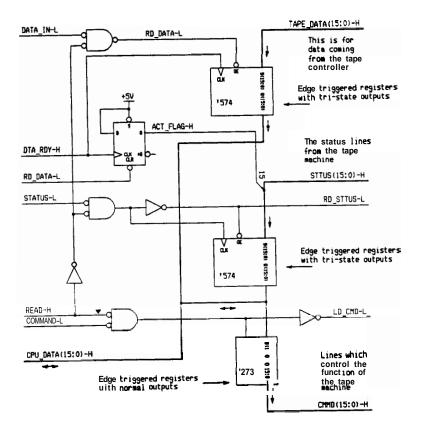

## 6.3. Synchronous Bus Protocols

The term "synchronous bus" can refer to a number of different techniques for **transferring** information between modules. The common characteristic of all of these mechanisms is that a clocking signal is used to synchronize all of **the** transfers. This **restricts** the length of the bus, since the signal must propagate to all bus masters and bus slaves, and be received with a reasonable degree of simultaneity at all locations. In this section we will consider **some** of **the** mechanisms that can be used for synchronous data transfers on bus systems.

One type of a synchronous bus is not a multiple master, general purpose bus. This is a bus bus system under the direct control of a central unit. This type of system fits into the model shown in Figure 6.1, but each of the units is directly connected to a master control unit. This central control unit then decides which module is to assert information onto the bus, and which element is to accept the information. That is, no general address is decoded by slave modules, but rather the central control unit selects both the source and the destination. The **microprogrammed** modules studied in Chapter 5 are included in this classification. since the contents of the bus **are** determined by **the** microcode word during each **micro** cycle.

Another bus protocol that is synchronous in some aspects is typified by the bus **connections of some high** performance **microprocessors. The M68020** has a protocol almost identical to that **described** above, except that the **mechan**isms allow for dynamic bus sizing and other flexibility. The mode of operation is **synchronous** with the system clock, giving the appearance of a synchronous mechanism. If the slave (memory, for example) is not able to respond to the processor fast enough to allow continuous operation, the processor automatically inserts idle bus periods, called "wait states," until the slave responds with the desired cata. Thus, the only difference in method is that the M68020 works in increments of the basic system clock, rather than using completely asynchronous signals.

Another bus protocol is used by a number of micmprocessors, and works in conjunction with the system clock. One of the problems that has become prevalent **as** integrated circuits have increased in complexity is providing enough pins to transfer the information into and out of a device. To minimize the total number of pins required for information transfer. some devices time multiplex the bus lines to allow one set of pins to present both address and **data** information. Thus, a processor with a 32-bit data path and a 32-bit address requirement can use one set of 32 pins, and synchronize all **requests** in such a way that all **bus** modules know when the address is available, and when the data is required.

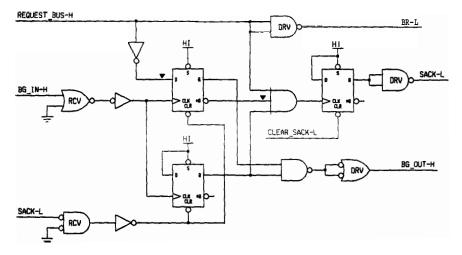

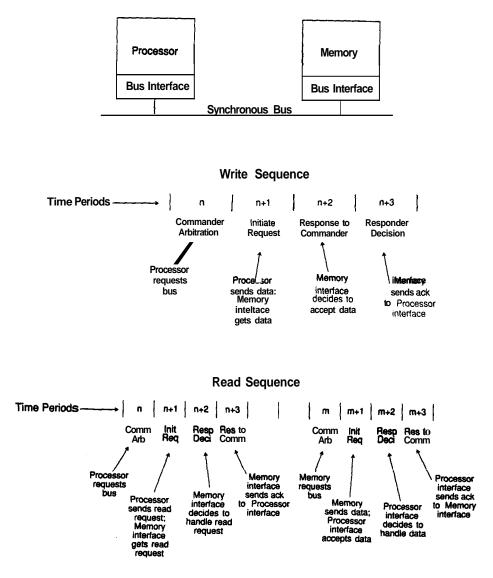

A sample of the NS32332 protocol is presented in Figure 6.10(a), which presents a write cycle. The 32 bits of address and data share the time multiplexed AD(31:0)-H lines: the presence of a valid address is identified by ADS-L, and the data is synchronized by WRTTE-L. The DDIN-L line identifies the direction of data transfer. The minimal transaction requires four cycles; the address is presented in the first cycle, and the data is available during later cycles. If the slave cannot respond within the required time, the master can wait until the transaction is able to proceed. This may occur. for example. if a dynamic memory is performing a refresh cycle when the processor requests a transaction. Most systems that use this technique will latch the address and create the appearance of separate address and data buses. A block diagram of one such arrangement is shown in Figure 6.10(b). To a slave device attached to the separate address and data lines, this communication mechanism appears the same as those previously described: the four event transaction proceeds in exactly the same way.

The time multiplexed **data/address** lines provides a mechanism to efficiently utilize one scarce system resource, the number of pins on **the** device. But another system resource that is not effectively utilized in the protocols described above is time. The master must **alert the** slave that some information is needed, and then wait for **the** slave to respond. A more time efficient mechanism would be to identify the basic components of a transfer and so design the protocol and **the bus** to allow these components to occur simultaneously. This requires a greater complexity on the part of both the master and slave modules, but it does **more** efficiently utilize the wires used to connect the modules together.

One of the beneficial features of asynchronous protocols identified in Section 6.1 is that the transaction proceeds as fast, or slow, as both sender and receiver agree that the information can be transferred. If some event requires more time, then the protocol essentially waits for the event to complete, and then **proceeds** with the transfer. This provides for increased flexibility, and it also provides for fairly simple interface modules. However, **the** overall **data** rates will be higher if more capability is **provided** in both the sender and receiver to minimize the amount of time that the bus lines are utilized to exchange **the** information. This is the basic premise of synchronous protocols, and the mechanism provides for time efficient use of the bus **lines**.

In the **protocol** described in Section 6.1. the bus master was responsible for **asserting the** address, and then allowing time for propagation delays and signal skew **before** asserting the request line to initiate action. One of the reasons that a

Figure 610. NS32332 Bus Transactions: (a) Timing Diagram for a Write Operation; (b) Block Diagram of Interface Logic.

synchronous protocol is more time efficient than the asynchronous protocol is that the action of all of **the** modules is coordinated by the presence of a common clock. This establishes an exact time when the information must be present on the bus, and when each module attached to the bus will know that information is available. This establishes bounds on the time required to transfer the information, and interface modules must all be designed to operate within those bounds. Thus, this mechanism calls for the interface modules to meet a time standard, rather than having the protocol adjust the time requirements to satisfy the needs of the various interface modules. The modules connecting to the bus must then be capable of transferring **information** at the rate determined by the bus protocol.

**The** mechanism of data exchange for synchronous protocols operates on a different set of principles than the asynchronous methods previously described, and this leads to a slightly different nomenclature when dealing with the units. We will call the module that initiates a transaction a commander, because it sends a command to another module. The command may or may not contain data, depending on the type of transfer. The module that fields the command we will call a responder. since it responds to the request in an appropriate manner. As with the asynchronous protocols. a number of different mechanisms will function properly. We will describe first a sample mechanism for write and read. and then examine a **specific** instantiation of a protocol.

There **are** four components of **the** transfer of information, and all four must be completed for a successful transfer. We discussed each of these functions in the process of describing the asynchronous protocols and **arbitration** mechanisms, but did not identify them as necessary constituent parts of the transfers. These components are:

- Obrain control of the bus. This is the responsibility of the commander and the arbitration network. When a module requires a transfer, it communicates that need to the bus interface module, which initiates a request for the bus. When the arbitration process allows the commander interface module access to the bus, the transfer can **proceed**.

- 2. Initiate transfer. If this is a write, this will include data. The commander places appropriate address (and data, if needed) and control information on the bus. The responder with that address will react by accepting the request This does not imply that the responder module will be able to handle the request, only that the request has been received.

- 3. Decide how to handle the request. This is the task of the responder bus interface module. This does not mean that the subsystem attached to the bus will necessarily accept (or provide) information immediately, but the bus interface module of the responder must be capable of deciding how to respond to the request. For example, if a memory is ready to accept information, it will be capable of accepting the information, and the bus interface module will decide that the information can be accepted. On the other hand, if a memory is busy with a previous request and unable to accept data, the bus interface module will decide to reject the request.

- 4. Inform commander of the decision of the responder. This is the feedback mechanism to allow the handshake to occur, and indicates to the commander that the request has been handled. If the request was a write, for example, the system attached to the commander bus interface module can proceed with its tasks. However, if the system attached to the responder interface module was

unable to accept the data. this decision is relayed to the commander, and the commander interface module can then initiate the request anew.

These four components are present in the asynchronous protocol, with its associated arbitration mechanism, but are not as evident as in synchronous protocols. The arbitration component can be handled in parallel, as in the UNIBUS protocol, or after a bus is available, as with most microprocessor bus systems, such as the NS32032 systems. Component 2, initiating the transfer, is handled by the bus master in an asynchronous protocol; the master module asserts the address, waits the prescribed time. and alerts the slave modules by asserting the request line. The third component, deciding how to handle the request, is an integral pan of the slave module mechanism, since all requests in an asynchronous protocol are handled immediately. If a memory read is required, then the protocol awaits the response from the memory before proceeding. Thus, it is difficult to separate the act of responding from the decision to respond. However, in a synchronous protocol, these two elements are distinct. and are handled in a different manner. The decision process is handled by the bus interface module. while the response to the request is handled by the appropriate subsystem, such as a memory. The forth component, the handshaking mechanism, is handled by the request and acknowledge lines of the system.

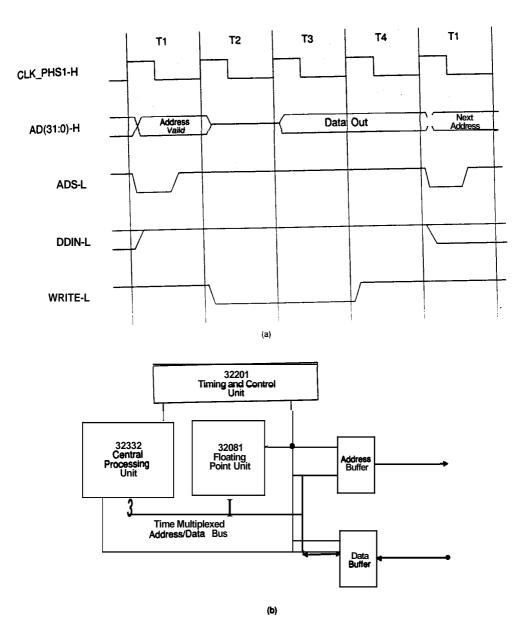

These four events are shown in write and read sequences in Figure 6.1 1. The write sequence begins (period **n**) by the processor interface module arbitrating for use of the bus lines. When the arbitration process is settled in favor of the processor, the sequence proceeds, and the processor interface module asserts the data and address intornation onto the bus lines (period n+1). When the clock occurs, the memory interface module accepts data and address, and determines that the request was intended for the memory subsystem. During the next period (n+2), the memory interface module ascertains the status of the memory and determines that the data can be accepted. And finally, during the acknowledge period (n+3), the memory interface module sends an acknowledgement to the processor interface module to indicate that the transaction was successfully completed. Since the commander of the processor bus interface module started the series of events in period n+3, so it will listen to the lines at the time to find out if the write action was successful.

The read sequence is also shown in Figure 6.11. The transaction is initiated by the arbitration of the processor for the bus (period n). When the processor interface module has obtained control of the bus lines, it will then assert the address and request information on the bus (period **n+1**). Synchronous with the clock, the memory interface module accepts the request, and in the following period (n+2) ascertains the status of the memory and decides to accept the request. This decision is communicated to the processor interface module in the last period of this sequence (n+3). The memory subsystem is then activated in order to supply the required information. The time from period n to period m reflects the response time of the memory. When the memory provides the information, the memory interface module initiates a bus transaction, first by arbitrating for the bus (period m), and then by asserting the data onto the bus (period m+1). The processor interface module accepts the data synchronous with the clock, ascertains in the next period (m+2) that the data is in response to an earlier request, and in the last period (m+3) sends an acknowledgement to the memory interface module.

As indicated in Figure 6.11, each of the four components of the exchange happens in separate cycles of the common clock, and can be pipelined. We will discuss pipelining in more detail in Chapter 8, but the basic idea is that independent events can occur in different pieces of hardware in the same period. With

multiple events occurring simultaneously. a speed advantage is obtained over the same events occurring serially. With a synchronous bus protocol, the interface devices can be designed in such a manner that each of the four functions involves a different set of hardware and a different set of bus lines, so that up to four separate transactions can be in different stages of execution at any one time. Thus, the speed advantage of synchronous bus transactions stems not only from the specific windows in which information must be valid, but from the pipelining and overlapping of transactions. Note that, if not enough transactions are available to keep the different portions of the bus busy during the various clock cycles. then the speed advantage of the pipelining is lost.

**Example 6.6:** Synchronous bus protocol: The synchronous backplane interconnect (SBI), which is the communication mechanism for the VAX 11/780 computer, is a synchronous bus protocol. What **are** the methods used by the protocol. and how fast can information be transferred on the bus?

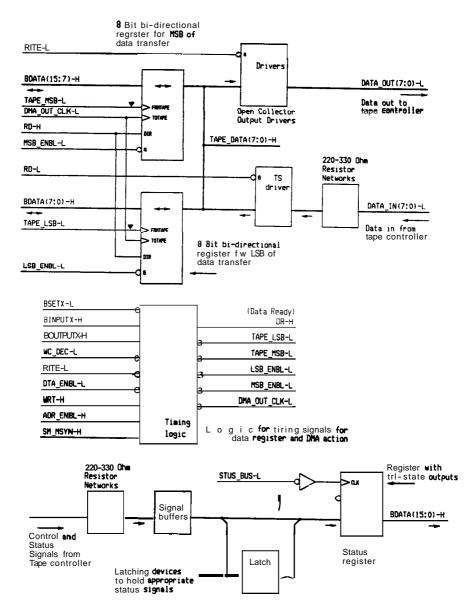

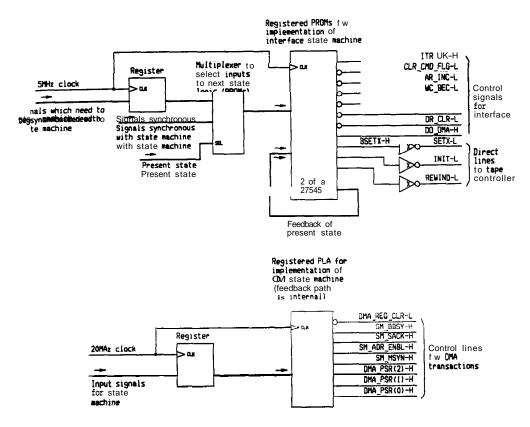

The principle lines (but not all) involved in information transfer on the SBI are shown in Figure 6.12(a). The sixteen arbitration lines [TR(15:0)] allow parallel arbitration of up to 16 different modules during a clock period. The information transfer lines include the 32 data/address lines [B(31:0)] and lines for identifying the type of transaction that is occurring. The response lines [CNF(1:0)] provide a data path for confirmation of previous transactions. The principle difference between the SBI and the protocol discussed above is that the SBI time multiplexes the data/address lines so that a write will require more than one cycle. The SBI mechanism allows for one or two words of data in a write transfer, so that up to X hytes of information can be written. Such a write cycle is shown in Figure 6.12(b). To demonstrate the pipelined nature of the action, the transfer is shown in a space-time manner. The lines involved in the transfers are divided into three groups: arbitration lines, information lines, and acknowledge lines. And the action of these three sets is described for each of the cycles. The DEC name for the commander and responder interface modules is the NEXUS. The first period (n) is used by the arbitation lines for the NEXUS associated with the processor to acquire control of the bus. Once this has occurred, the transfer can continue. The arbitration unit has the capability of locking out other requests for the two additional cycles needed to complete the transfer. The assertion of address and write identification information occurs in the second cycle (n+1). This information includes not only the target address of the write, but also an identifying field to specify the source of the information. The reason for this will become apparent with the read transaction. At the end of this period the NEXUS associated with the memory will receive the address and the identification information. The data/address lines are used in the next period (n+2) to send the first 4 bytes of data; at this same time, the memory NEXUS is deciding how to handle the request. At the end of the period, the acknowledgement decision has been reached, and the first bytes of data are accepted into the NEXUS. Then, during the final data cycle (**n+3**), the acknowledgment is returned to the originating NEXUS for the address and write identification information. In the next two cycles additional acknowledgement information is returned for the data cycles of the transfer.

The pipelined nature of possible transactions is indicated to in **Figure 6.12(b)** by the shaded area that indicates a possible second write cycle to be

| NEXUS<br>for<br>Transm<br>and<br>Receive | it                                 |                                  | Infor<br>TAG(2:0                  | Arbitration<br>TR(15<br>mation Tra<br>)), ID(4:0),<br><u>Response</u><br>CNF(1<br><u>Control</u><br><u>Interrupt</u><br>REQ(7 | :0)<br>msfer L<br>M(3:0),<br><u>e Lines</u><br>:0)<br>tines<br>Lines | _ines<br>B(31               |                 |                                 | f<br>Trar<br>a                  | KUS<br>or<br>ismit<br>nd<br>aiva |

|------------------------------------------|------------------------------------|----------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------|-----------------|---------------------------------|---------------------------------|----------------------------------|

| Time Period —                            | - !                                | n                                | n+1                               | n+2                                                                                                                           | n+3                                                                  | 8                           | n+4             | n+5                             | ; }                             |                                  |

| Arbitration<br>Action                    | 0                                  | cquire<br>ontrol<br>of bus       | Hokd<br>bus                       | Hold<br>bus                                                                                                                   | Acqui<br>contri<br>of bu                                             | ol<br>JS                    | (Write c        | ycle 2)                         |                                 |                                  |

| Information<br>Transfer                  |                                    |                                  | Send<br>Command<br>and<br>Address | Send<br>four bytes<br>data                                                                                                    | Senc<br>lour by<br>data                                              | rtes                        |                 |                                 |                                 |                                  |

| Confirmation                             |                                    |                                  |                                   |                                                                                                                               | Confin<br>Addres<br>Comma                                            | SS,                         | Confirm<br>data | Confir<br>data                  |                                 |                                  |

| Time Period>                             | ] n                                | n+1                              | n+2   n-                          | 13                                                                                                                            | m                                                                    | m+                          | 1   m+2         | m+3                             | m+4                             |                                  |

| Arbitration<br>Action                    | CPU<br>NEXUS<br>acquire<br>control | Reed<br>Cycle<br>2               | Write                             |                                                                                                                               | MEM<br>NEXUS<br>acquire<br>control                                   | MEN<br>NEXI<br>hold         | JS              |                                 |                                 |                                  |

| Information<br>Transfer                  |                                    | CPU<br>NEXUS<br>sends<br>request |                                   |                                                                                                                               |                                                                      | MEN<br>NEXI<br>senc<br>data | JS NEXUS        |                                 |                                 |                                  |

| Confirmation                             |                                    |                                  | ME<br>NEX<br>cont<br>requ         | (US<br>firm                                                                                                                   |                                                                      |                             |                 | CPU<br>NEXUS<br>confirm<br>data | CPU<br>NEXUS<br>confirm<br>data | 1                                |

Figure 6.12. Synchronous Backplane Interconnect Protocol: (a) Control Lines Involved in SBI Information Transfer: (b) Write Transaction. 8 Bytes: (c) Read Transaction, 8 Bytes.

initiated by a second NEXUS. Note that the second cycle begins before the first cycle ends. This protocol allows meaningful data or address information to be placed on the data bus during each cycle.

The read transfer operates with a similar mechanism, except that the request and the response are separated by the response time of the memory.

This is shown in Figure **6.12(c)**. Here the **NEXUS** associated with the processor acquires control of the bus (period **n**), sends out a read **request** consisting of an address, a logical identifier, **and** a transfer type identification that informs the memory to supply 8 bytes. The processor **receives** the acknowledgement of the request in period **n+3**. Some time later, when the memory has the information for the processor, the **NEXUS** associated with the memory gains control of **the** bus (period **m**), and sends **the** data in two 4-byte transfers (period **m+1, m+2**). The destination of this information is carried by the identification lines, which will have the same logical identifier that was passed with the request. The **NEXUS** associated with the processor sends its acknowledgement to the memory in periods m+3 and **m+4**.

Additional read and write transactions are shown in the shaded areas of Figure **6.12(c)** to demonstrate the pipelining and parallel events possible with the protocol.

The clock cycle time for the SBI is 200 nsec. Thus, with the above protocol it is possible to send 8 bytes every 600 nsec. This gives an effective data rate of 13.3 **MBytes/sec**.

In this section we have considered some of the principles involved in **transferring** information with synchronous bus communication protocols. These mechanisms will, in general, lead to a higher data rate than their asynchronous counterparts for two basic reasons. First, the presence of a common clock limits the physical size of the system and synchronizes ail requests for action. This synchronization establishes a time at which all action must take place. Second. the separation of the components into independent pieces of hardware. and into independent bus lines, permits pipelining of the various functions. This allows concurrent use of the available resources. The net result is that data can be **transferred** at higher rates than achievable with other methods.

## 6A. Data Movement: Programmed I/O and Direct Memory Access

We have discussed some of the basic mechanisms involved in doing transfers of data over bus systems. Regardless of the exact protocol used, an arbitration mechanism is utilized to identify the module which controls the bus. This module then initiates a transfer, and the data is moved from one module to another. This mechanism is most often utilized to exchange information between a memory and a processor module. However, the same mechanism is used to transfer information and commands to and from I/O devices. In this section we want to explore some of the methods that can be used to control I/O devices and to transfer information to and from a computer system. For computer systems that include separate I/O instructions, generally an I/O bus is used for the communication. In some systems with I/O instructions, the system bus is used for memory and I/O transfers, but I/O transactions use a slightly different set of control lines to perform the transfers. However, one prevalent practice is to use the same address space for both memory and I/O devices. This method calls for the I/O devices to be assigned locations in the memory space, and then, when the device is to be activated and controlled, the processor does so by writing and reading the appropriate locations. This is called "memory mapped I/O," and is used extensively in minicomputer and micmprocessor systems. In fact. the inclusion of I/O instructions in the processor instruction set does not preclude the use of memory

mapped I/O, and the manner used for connecting I/O devices is left up to the **system** designer.

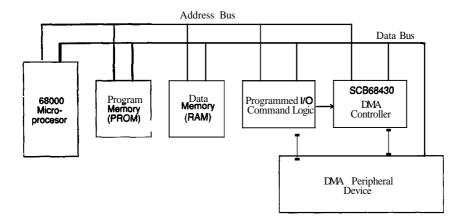

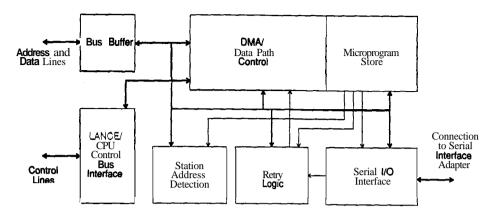

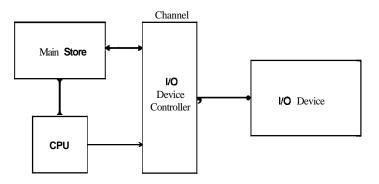

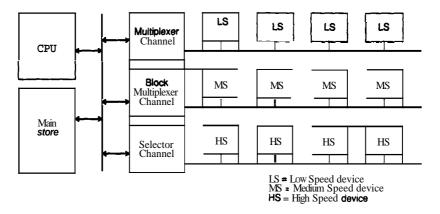

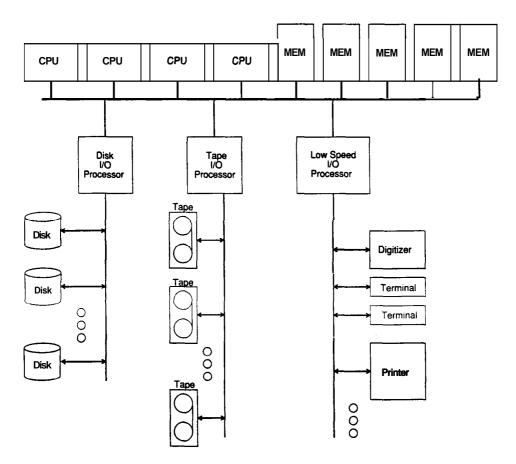

There are three basic mechanisms for the interaction between the processor and the I/O device. The processor **responsibilities** of each mechanism, the system **resources required**, and the complexity of the I/O interface module **required by** each method **are** all different. A **Mock** diagram showing the **relationship** between the processor and the I/O device is shown in Figure 6.13. The I/O interface module interacts with the system **bus** to **provide both** control signals and **data** to an I/O device controller. Most I/O device controllers **are** designed in such a way that they will control a single type of device, such as a disk or tape unit. However, the devices can be controlled by a single I/O device controller. If another type of I/O device is to be included in the system, then a different I/O device controller is needed, with its associated I/O interface module.

Regardless of transfer mechanism utilized, the **processor** must have the ability to direct action in the I/O device with instructions; this mechanism we will refer to as "programmed UO." It is possible to **control** both the action and the data movement of a device with programmed UO, as we will see in an example. It is also possible to initiate the action with programmed I/O, and then allow the interface module to **interrupt** the processor when data is available. This **interrupt** capability allows **the** processor to **proceed** with other work while the **data** is being obtained, and then to interact with the I/O device only when data is available. Finally, the highest **speed is** obtained when the interface module has the capability of exchanging data directly with the memory. This is referred to as direct memory access (DMA), **and** is limited in speed by the transfer rate of the bus. For

Figure 613. Interface System Block Diagram.

DMA transactions, programmed I/O instructions **are** used to set up a **starting** address in the system memory and the length of the transfer; and then another programmed I/O instruction initiates the action. The system is then free. to perform other **tasks**, and the DMA interface module interacts **directly** with system memory to perform the transfer.

An I/O device is controlled by writing (and reading) information to (and from) specific locations. This method is independent of the type of bus protocol used. but the examples in this chapter will all be done with **the** asynchronous pro**tocol**, as that is the most widely used mechanism at this time. Interface module and I/O devices can be controlled by assigning a specific action to each **of** the addresses used by an I/O device, or by assigning an action to specific bits or bit **patterns** at a single address. **In** either case. the processor sends the command to the interface module by writing to the proper address with the necessary bit pattern. When the interface module receives a write request, it supplies the appropriate **information** to the bus. **In** this fashion. information can be moved to and from the I/O device.

One of the most frequent inquiries made by a processor **concerns** the status of the interface module and UO device, whether it is busy or not, and whether it has data available. Thus, reading a status register in the interface module must be done quickly and easily. The status register usually contains information about the device it is controlling. For example, a tape recorder interface module might have bits in its status word that indicate if the device is on line. if it is busy, if the interrupt 1 enabled, and so on. The processor 1s then capable of determining the status of the device by reading the status register.

The simplest interface mechanism results by allowing the processor to control all aspects of the transfer. This method consumes all of the time of the processor, but can be used if the need arises. Since the machine is entirely utilized with the I/O transfer, it is not capable of being used for other tasks during this time, and this is generally not an acceptable cost. Nevertheless, the interface module between the computer system and the UO controller can be very simple. as shown by the following example.

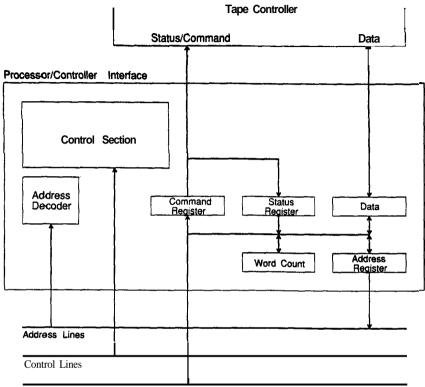

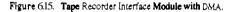

**Example 6.7: Interface module design:** Design an interface module that will connect a tape recorder to a **16-bit** asynchronous bus for a read only operation using memory mapped I/O techniques. This mechanism is to be controlled by writing command patterns to address **FFFD80<sub>16</sub>**, reading status at address **FFFD82<sub>16</sub>**, and by reading the data at address **FFFD84<sub>16</sub>**. **Wrat** is the maximum data rate achievable by this mechanism?

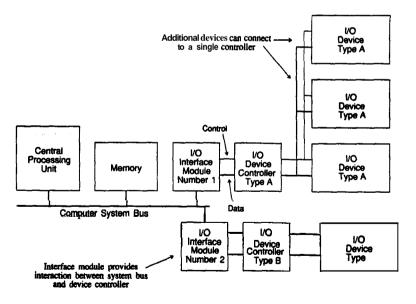

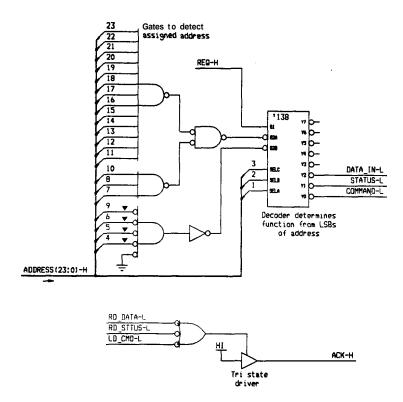

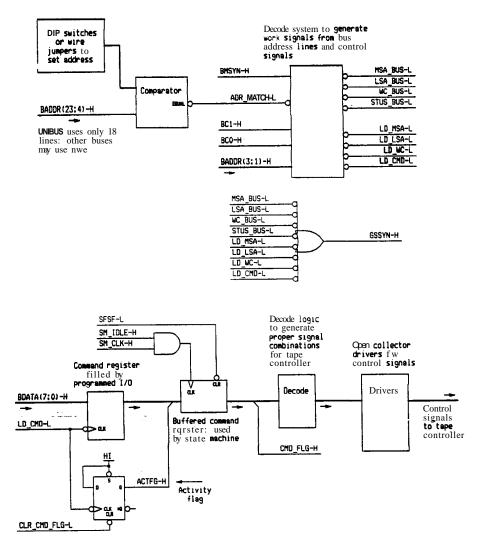

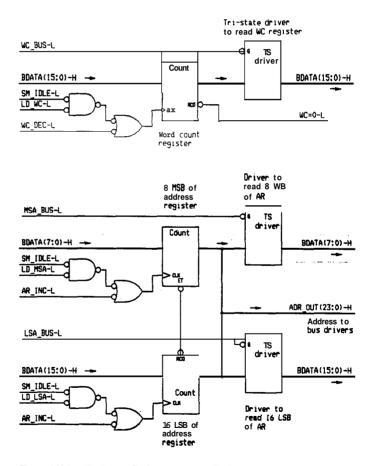

We will delay several of the details of the tape **recorder** side of **the** interface module, and concentrate on the interaction with the bus. Assuming that the interface method to be used is the four event protocol described in Section 6.1, the lines of interest are the **address** and data lines, a read line. a request **line**, and an acknowledge **line**. One design for this interface module is shown in Figure 6.14, which we will examine by function.

The first function is the address decode and command **line** interface. The most significant lines of the address **are tested** with a **gating** network to look for the proper address (FFFD80<sub>16</sub> - FFFD84<sub>16</sub>). This **same** function can **also** be accomplished by using an address decoder chip. such as the 74677. which looks for a specified bit pattern. However, if the address of the device is not known **at** & sign time, then one mechanism is **to** use comparators

Figure 6.14(a). Tage Recorder Interface Module (Control).

configured with address specifying **switches**. The least significant lines are directed to a 3-line-to-8-line. decodet, which asserts a line for each of the appropriate addresses. Note that the least significant line (ADDR(0)-H) is not used; we **assume** that the system is always going to access this information in 16-bit words, properly aligned.

If the address matches, then when the quest line is **asserted** (REQ-H), the required action is immediately **performed**, and the acknowledge line asserted (ACK-H). No delay other **than the** gate delays of the circuitry is inserted into the system since the timing does not require it: information from the master is accepted with edge triggered devices, and the **reaction** time of the master will account for any hold time **needed**. Also, information sent to the master is **asserted** at the **same** time **as the** acknowledge line, and 'the master is responsible f a any delays necessary to account for skew on the data lines. **Thus**, command information (and **data**. if it is **required** by the **specified** interaction) is **accepted** without delay. Likewise, **as scon as a read** command is received, the **requested** information is provided. **This** register interaction will result in a faster **read/write** than normal **memory**, **although** it is in the **same** address space.

Figure 6.14(b). Tape Recorder Interface Module (Data Path).

To demonstrate the programmed I/O mechanism, consider the transactions required to cause the recorder to space forward a block, then read the, next block of 512 words. Assuming that there is a simple assembly language to work with, the following code section will perform the desired work:

| 1  |      | MOV # <fsf>, @FFFD80</fsf>           | FSF is file space forward pattern.            |

|----|------|--------------------------------------|-----------------------------------------------|

| 2  | one: | TESTI # <busy>, @FFFD82</busy>       | BUSY is pattern to test busy condition        |

| 3  |      | JNZ one                              | of interface module. Loop to "cne" till done. |

| 4  |      | MOV #<512>, R1                       | Set up the count.                             |

| 5  |      | MOV # <start addr="">, R2</start>    | Set up the address.                           |

| 6  |      | MOV # <dav>, R3</dav>                | Set up test pattern for dam available.        |

| 7  |      | MOV # <fffd82>, R4</fffd82>          | Set up address of status register.            |

| 8  |      | MOV # <fffd84>, R5</fffd84>          | Set up address of data register.              |

| 9  |      | MOV # <read cmnd="">, @FFFD80</read> | Start read action.                            |

| 10 | two: | TEST R3, *R4                         | (800) Is there data?.                         |

| 11 | JZ two       | (450) If not, go back to "two."     |

|----|--------------|-------------------------------------|

| 12 | MOV *R5,*R2+ | (1150) If so. move where R2 points. |

| 13 | DEC RI       | (550) and bump R2; done 512 words?  |

| 14 | JNZ two      | (600) If not. go back to "two."     |

|    |              | (3550)                              |

The first instruction writes out the pattern to indicate to the interface module that the tape recorder should move forward to the next file mark. The next two instructions merely wait until that is accomplished. Instructions 4 through 8 set up the general purpose registers to allow faster processing in the transfer section. Instruction number 9 actually starts the read action of the recorder. Instruction 10 checks to see if the **data** is available. It is similar in function to instruction 2, which checks to see if the recorder is busy. However, by using values in registers, rather than values in the instruction stream, the time required for the instruction is greatly reduced. In Chapter 4 we identified different instruction times for instruction types, based on the amount of work required by the instruction. Using the times identified there. instruction two requires 1,750 nsec for completion, while instruction 10 can be done in 800 nsec. Instruction II is to loop until data is available, when the action moves to instruction 12, which moves the data from the interface module to the designated spot in memory. And with the autoincrement feature of the destination address, the system is ready for the next iteration. Instruction 13 decrements the counter. and instruction 14 loops if the count has not reached zero. The highest data rate will occur when the instructions [() and [] are executed hut once each iteration. When this occurs. The loop takes 3,550 nsec. Two bytes each 3,550 nsec results in a data rate of 563 Kbyteslsec. This rate cannot be sustained over time. since it does not take into account the time required to set up the transaction.

The above example indicates what can be accomplished by a machine dedicated to performing a single transfer. However, if the device being **controlled** is a modem or line printer, then the **data rate** is much lower than that attainable by programmed I/O. Most of the time the machine would be executing the wait **loop**, waiting for the **data** movement to occur. Therefore, system designers have often designed the machines in such a way that the interface module can **interrupt** the action of the computer when **data** movement is necessary. The positive effect of this is that the machine time that would be used by looping can be effectively utilized **for** other functions. The negative effect of this mechanism is that the **transfer** rate will be lower, since more work is needed for each transfer.

**Example 6.8:** Interface design with interrupt: Consider the system of Example 6.7, but assume that the interface module is also capable of issuing an interrupt when data is available. What is the maximum data rate for the system?

We will make the assumption that an interrupt action causes the current PC and status register to be pushed onto the system stack, and **also** causes the **interrupt** service routine to be entered with the vector mechanism discussed in Chapter 4. This mechanism will require about 1.100 nsec in our machine. We include here two sections of code. one of which is used to set up the action, and one of which is actually executed once for each word of data transferred.

| 1<br>2<br><b>3</b>   | setup:          | MOV # <start addr="">, @ADDR<br/>MOV #&lt;512&gt;, @COUNT<br/>MOV #<read cmnd="">, @FFFD80<br/></read></start> | Set up the initial address.<br>Set up the count value.<br>Start the read action.                                                                                 |

|----------------------|-----------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10<br>11<br>12<br>13 | srvce:          | MOV @FFFD84, *@ADDR+<br>DEC @COUNT<br>JZ more<br>RTI                                                           | <ul> <li>(3650) Move the data</li> <li>(1800) Check the count.</li> <li>(450) If done, do other action.</li> <li>(850) If not, return from interrupt.</li> </ul> |

| 14                   | mom:            |                                                                                                                | •                                                                                                                                                                |

| <b>20</b><br>21      | ADDR:<br>COUNT: | DATA 0<br>DATA 0                                                                                               |                                                                                                                                                                  |