# Memory Systems

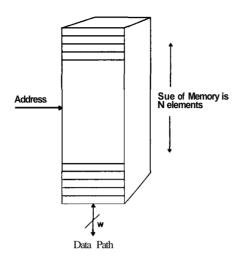

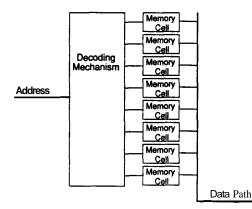

One of the most basic functions of a computer is the retrieval of information stored in a memory element. This action is needed to obtain the instruction to perform; it is also needed to obtain the data on which the instruction operates. One widely used model of memory is shown in Figure 7.1. In this model the memory consists of N consecutive storage locations. The size of a location is dependent on the system architecture, and the width of the data path (w) is a function of the implementation mechanisms. But the model remains the same: the address supplies the desired location, and the data is transferred to/from the memory. The number of bits needed in the **address** is  $\log_2 N$ , We will use this model to represent a memory system, and recognize that for special systems appropriate changes must be made. In many systems, the size of the memory is given in bytes, although **that** is not the normal width of data transfers. One reason for this is that the systems are byte-addressable, and although the width of the transfer path may not be a single byte wide, the information is obtained by giving the address of the specific byte desired. Then, if more bytes are required, they are obtained as needed by the processing unit.

The design of the memory unit is a series of **tradeoffs**, since a number of different factors must be considered. These include the size of the memory (N elements), the width of the data path (w), the organization method, and the speed of access. The speed of the memory depends on many factors, including technology of implementation and organizational method. Regardless of the mechanisms involved and the memory technology used, there will be a minimum time to access information, which we will call  $\tau_A$ . This represents the shortest time required to retrieve the information, and includes not only the access time of the memory device, but also any delay caused by additional gates needed to provide sufficient drive capability for the address or the **data**. Another very important time is the minimum time between accesses. or the **memory** cycle time, which we will call  $\tau_{a}$ . For "normal" memory interaction, where information is retrieved

Figure 7.1. Memory Model: Linear Array of Locations.

from memory, then work is done on it, and then memory is accessed again,  $T_{i,j}$  is not 3 limiting factor, since the action of the system will not result in memory accesses which occur faster than  $T_{cyt}$ . However, for burst mode access, where several consecutive memory elements are read or written,  $T_{cy}$  is a factor that limits the rate of transfer. One simplifying assumption we will make is that the memory times are the **same** for the read and write cycles, which is not always **true**.

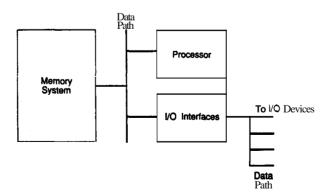

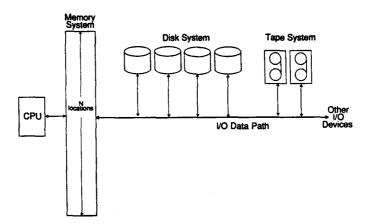

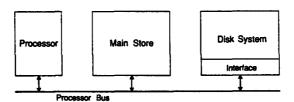

The memory itself is configured in such a way that all of the necessary accesses **can** be made to it. That is, using one or more of the communication protocols described in Chapter 6, the memory is **connected to** elements that need the capability of **data** transfer with the memory. The simple representation of Figure 7.2 shows a memory that **can** be accessed by a **processor** and **I/O** devices. The

Figure 72 Memory System and Connections to Processor and I/O Interfaces.

data path (bus system) is also used to allow the processor to control the action of the t/O interfaces. The configuration shown in Figure 7.2 is a very simplistic representation, and the actual connections to the memory can be as simple or complex **as the** application requires. In general, however, we would like to create a memory with **as** large a size (N) as reasonable within the design constraints, with an access time  $(T_{A})$  and a cycle time  $(T_{CT})$  as short as possible. Let us **look** at the memory hierarchy mechanisms used to try to accomplish this, then examine details of the memory systems involved.

#### 7.1. Memory Hierarchy: Tradeoffs in Size and Function

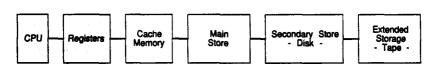

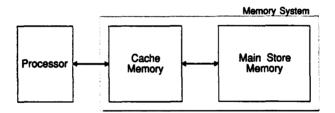

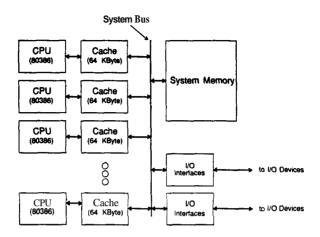

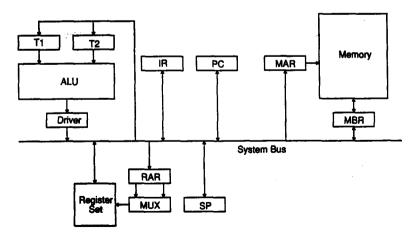

In the description of their 1946 IAS machine Burks, Goldstine. and von Neumann recognized that "ideally one would desire an indefinitely large memory capacity such that [infonnation] would be immediately available ..."[BuGo46]. But the realities of the economics and the technology are such that compromises must be made. The **IAS** machine contained **4.096** words of 40 bits each for the main store, which "exceeds the capacities required for most problems that one deals with at present by a factor of about 10." However, they recognized that the time would come when this would not be sufficient storage for the problems to be solved in the future. and therefore looked forward to the "constructing of a hierarchy of memories. each of which has greater capacity than the preceding, but which is less quickly accessible." The machines of today indeed match this concept. and can be represented by the block diagram shown in Figure 7.3. The fastest memory elements are those closest to the processor: most systems have a small number of very high speed locations, which we call a register bank. The  $T_{4}$  for the registers is minimal. and in general the infonnation stored in registers is available in the same cycle as it is needed. However, the cost of this type of storage is very high, whether the cost is measured in dollars, silicon real estate, or power dissipation. For this reason, the amount of register storage available in a system is relatively small, from eight to sixteen registers in most general purpose systems, to over a hundred in some special purpose and RISC systems.

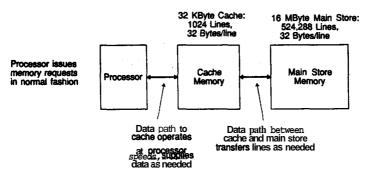

The next element in the memory hierarchy is often a cache memory. The **purpose** of a cache is to enhance the operating speed of the processor by making available the most **recently** used information by keeping it in a high **speed** temporary storage. The  $T_A$  of a cache is on the order of two CPU cycle times, and we will discuss methods of approaching cache designs in Section 7.4. The amount of

Increasing speed; increasing cost

Figure 7.3. Block Diagram of Hierarchical Memory System,

memory available here is generally small in comparison to the other elements of the system. For example, **the** VAX 11/780 has a 2-Kbyte cache, and some other **processors** have even smaller caches. However, as the cost of memory decreases with respect to overall system costs, larger caches **are** much more common. Many newer systems have caches that contain 16 Kbytes to 64 Kbytes or more incorporated with the processing unit.

The purpose of the cache is to maintain current information for rapid retrieval. This is done in a manner that is transparent to the user. The programmer does not know of the existence of the cache, except that the speed of the system is enhanced over a system with no cache memory. Thus management of the data is done in a fashion determined at design time. in contrast to the virtual memory systems discussed below.

The information in a cache memory is a high speed copy of what is in main store, which is the "standard" memory of the computer. The amount of storage in a main store is system dependent, but it has increased with each passing year. In contrast to the 4.096 locations of the (AS system, many systems require a minimum of 8 Mbytes or more. The technology is now such that it is possible to get 8 Mbytes in eight packages, which is one of the reasons for the increased size of main store. The  $\tau_A$  of main store is about an order of magnitude greater than the  $T_A$  for cache. Thus, when a request is made for information, and it is determined not to be in the cache. then the system pauses until the information is retrieved from main store. At that time the processing can continue. Some of the issues involved in the design of the main store are discussed in Section 7.2.

The information resident in main store for a "standard" computer system is a sufficient amount of the operating system to maintain a continuity of action. That is, a portion of the operating system. I/O storage areas, and other basic routines are maintained in the memory of the machine. In addition, the active portions of user programs and data sets **are** available as well. The portions of the operating system and user programs and data that **are** not active **are** kept on the next level of **the** hierarchy, the secondary store.

The purpose of the secondary store of this hierarchy is to maintain copies of all of the programs and data needed by the computer. Generally this will be a **disk**, although it could **be** any block-oriented storage **device** with a large capacity. Such devices have **been** built with charge **coupled** devices, bubble memories, and large **RAMs.** This device is generally organized into files, and maintaining the files is one of the responsibilities of the operating system. In addition to the files, there is an area which is used to maintain the current copies of user program space; this area is often called "swap space." The swap space is also under the control of the operating system. The procedures and mechanisms established within the computer system to manage the use of the memory system are done so to effectively utilize the available system resources. With a combination of software/system policies and the appropriate hardware, only copies of currently active information need reside within the main store of the machine at any given time. Still, the apparent effect is that **user** programs execute in "virtual space," which frees up the user from being aware of the exact physical configuration of the system and the orientation of his program.

**The**  $T_A$  of **information** on the disk is much longer than the  $T_A$  for main store. Note that **the cache** is created from a (relatively) small amount of high speed **RAM**; and main store is also **electrically and** randomly accessible, but with lower **cost**, slower devices than the cache. Secondary store, on the other hand, involves electromechanical devices, and therefore requires relatively long times to find the physical location of the information and effect the **transfer**. The ratio for  $T_{A_{\text{SECONDARY}}}$  is on the order of 10, but the ratio for  $T_{A_{\text{SECONDARY}}}$   $\longrightarrow$  /  $T_{A_{\text{SECONDARY}}}$  is on the order of 100,000. For this reason, when information is needed by the processor. and it is not in main store, the operating system will request the **needed** information, place the current task on a queue, and get a new task to execute while waiting for the information to be retrieved from the disk. This action of "context switching" allows the processor to be **shared** effectively between multiple programs; such systems **are** often called multipmgrammed or time-shared systems. To be effective, the secondary storage system must be sufficiently large to handle the swapping functions and the necessary file system operations.

The last member of the hierarchy shown in Figure 7.3 is the extended storage. This consists of information stored on magnetic tape, which is slow in comparison to the disk storage. This storage is generally used for permanent storage of programs and data, as well as transfer of information from one computer to another. Some systems have automated tape storage capabilities. so that parts of the extended storage can be considered a random access system with capabilities similar to the disk systems. albeit much slower.

The intended operation of the memory hierarchy is to provide a very large memory capability, with the response time of a cache system and the storage capability of a disk or tape system. The mechanisms used to perform these **tasks** is the subject of the following sections.

## 7.2. "Standard" Memory Systems: Random Access Storage for Programs and Data

The storage of information in computer systems is accomplished by utilizing collections of individual storage elements, each of which is capable of maintaining a single bit. Thus, for a device to be useful as a memory element it must have two stable states, a reliable mechanism for setting the device to one state or the other, and a mechanism for interrogating the state. Memories have been built of a variety of devices that match this characteristic, including relays, individual vacuum tubes, storage tubes, and delay lines, which form a type of serial memory. In each **case**, information in the form of bits was entered into the **memory**, and then at some later time extracted for use by the system.

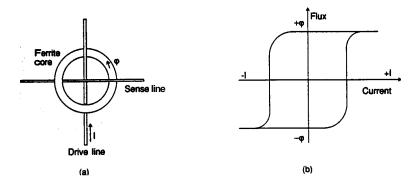

Storage tubes and delay lines allowed for information storage in some early machines, but the central memory technology next used by most computers utilized the magnetic properties of iron. The mechanism utilized by these memories is depicted in Figure 7.4. A ferrite material is fashioned into a circular, doughnut shape, as shown in Figure 7.4(a). The principle utilized by this **device** is the fact that the magnetic orientation of the fenite material will change to coincide with a forced magnetic field, if the field is strong enough. Due to the physical nature of the material, once the magnetic orientation has been established, it will remain in that orientation until a different magnetic field is created to change it. This is shown by the flux-versus-current diagram of Figure 7.4(b), which is known as a hysteresis loop. When the current returns to zero, the orientation of the flux remains in the diltion that it was established. It will remain in that orientation until a current is passed through the drive line in the opposite direction. The residual magnetic flux within the core is used to store a single bit. If the flux is aligned in one direction, the bit is a zero; alignment in the opposite direction represents a one. The use of the core for the storage of information requires at

Figure 74. Magnetic Memory Mechanisms (a) Magnetic Con for Single Bit. (b) Hysteresis Loop.

least two wires passing **through** the center of the core. One line is used to write information into the core:

- Forcing current in the drive line as shown in Figure 7.4(a) will create a flux, φ, as shown: let this orientation represent a one.

- Forcing current in the wire in the opposite direction from that shown in the tigure will reverse the orientation of  $\phi$ ; let this orientation represent a zero.

The other wire is used to sense the content of the core. Note that establishing the orientation of the magnetic **flux** can indeed **represent/binary** values; but we not only need to establish the value, we also need to **retrieve** the value stored in the **core.** The sense line **uses** the fact that a wire in a changing magnetic field will pick up a voltage: that voltage is **sensed** to identify the **content** of the **core.** The **process works** in the following manner:

- A negative current [opposite to the direction shown in Figure 7.4(a)] is established in the drive line; the net result is to leave the core in an orientation representing a zem.

- If the sense line detects a voltage, then the magnetic field is changing. and hence the bit represented was a "one" before the **process** started.

- If the sense line detects no voltage, then the magnetic field is not changing, and the bit **represented** by the con was a **"zero"** before the process started.

To produce **information** needed by a **processor**, these characteristics are **utilized by** core memories in the following fashion:

• Read: To read the value stored in a bit. a current is sent through the drive line of the core for that bit Assume that the current direction is that which establishes a "zero" in the core. If the new magnetic orientation agrees with the established orientation. no change is made and the sensed voltage is zero, which corresponds to a "zero" bit. If there is a change in the magnetic orientation, then a nonzero voltage is created on the sense line. which corresponds to a

"one" bit. In either case the bit representation of the magnetic flux at the end of the read is a "zero."

The overall effect is to **destroy** the data stored in the core, and so core memories are destructive readout devices. This is generally an unacceptable feature, so the value read out is stored in a register and immediately **returned** to the core. For this reason cores generally have  $T_{cr} = 2 \times T_A$  since the data must be restored to the accessed location.

• Write: The first step in the write sequence is to place known data in all of the cores that will be used for the write: this places a constant. known value in the core. The value could be either a "one" or a "zero," but we will assume that it is a zero. This is not absolutely necessary, but is usually combined with the electronics used for the read cycle: the first half of the read process above performs this function. Current is then directed to the drive lines on those bits which will have a "one" orientation. while current is inhibited from the cores for those bits that need to maintain a "zero" orientation. In this fashion, the correct orientation is established for the data to be written to the core.

This technology was used for many years to create the main memory for most computers. However, the cost and size of the memories, as well as their speed, became a disadvantage as semiconductor memories were developed. Each bit in the memory required a separate core, with at least two, but usually three, wires through it. The technique of storing information by the magnetic orientation of a ferrous material is now used more prevalently for other types of storage than for the central memory ot a computer. The magnetic orientation of a region of ferrous material on a surface is used to store a bit. and this surface is most often on a rotating magnetic disk, or on a magnetic tape. The reading of the information still requires a moving magnetic field, but in a disk or tape unit the movement of the field is caused by physical movement between the surface and a detecting element called a head. The head is also used to create the proper fields for writing the information to the magnetic surface. Disk units are utilized to store thousands of bytes, such as floppy disks on a personal computer, to billions of bytes on larger machines. Tapes have a similar range of storage abilities, and are used on computers of all sizes.

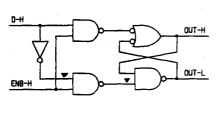

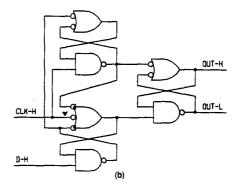

**Different** types of **electronic** technologies have been used to store information in computers, from tubes to semiconductors. At one level we can examine the storage mechanism by **looking** at the gate level; another level is **the** device level. Figure 7.5 shows two different gating implementations for storing a single bit These can be cascaded into several bits to store bytes or words. One method of maintaining a bit is to put it into a latch, as shown in Figure **7.5(a)**. The simplest gating arrangement to store a bit is cross coupled gates, and these are shown in the figure. The information placed in these gates is established by the input (D) when **the** enable line (ENB) is asserted. As long as **the** enable line is **asserted**, whatever information is on the data **line** will be passed to the storage element. When the enable line is **deasserted**, **the** last value for the data will be retained. This behavior is useful for many computer functions, and can be used to store **information** when needed.

**The** latch behavior is **not** the most prevalent mechanism used in storage elements in a processor. The gates shown in Figure 7.5(b) implement an **edgetriggered** function, **the** behavior generally associated with a register. The **mechan**ism shown in the figure is used to capture **the** value of **the** data (D) on **the** rising edge of **the** clock (**CLK**). Analysis of **the** gates implementing the latch is

Figure 75. Possible Arrangements of Gates for Storing a Single Bit. (a) Latch (Single Bit). (b) Edge-Triggered Flip-Flop.

relatively straightforward. but the register **function** is very involved. However, in both cases the data must **be** stable for some window of time around the active edge of the clock (or enable). If this condition is not true, the unit can enter a metastable condition that will cause problems in high speed systems.

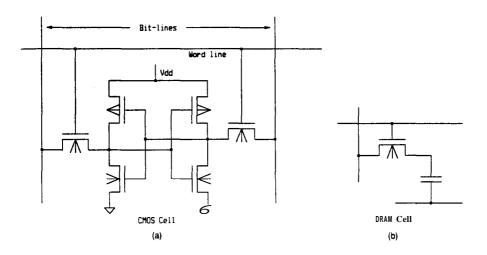

The circuitry shown in Figure 7.5 requires many individual transistors or other active devices to create. Therefore, they are used in small numbers in places where the storage requirements are not extensive. Creating enough register or latch type circuits in an integrated circuit ro store a lot of information would not be a good use of silicon real estate. Two types of mechanisms for storing information in semiconduction memories are shown in Figure 7.6. Figure 7.6(a) shows an arrangement of parts that implements a static memory cell. As in the **case** of the latch, there is cross coupling between the elements, and the device has two stable states. The active action of the system makes fure that the value of the **cell** remains as set until an external event causes a **chanse**. Thus, a value written to this cell will be maintained until the power is lost, or until the contents is changed by the write action. In this it **differs** from core memories, since it is not a **destructive** readout mechanism.

Static memories generally have a smaller number of bits per package, and a higher power consumption, than dynamic memories. The static mechanism of Figure 7.6(a) requires six transistors in every cell; other static memory configurations utilize fewer active elements. One of the tasks of memory designers is to reduce the number of components needed in an individual storage cell, since fewer elements means that each individual cell can be smaller and require less power, which in turn leads to larger memories. The memories with the largest capacities use not a static mechanism, but rather a dynamic mechanism, as shown in Figure 7.6(b). Here the value of the bit is not determined by the **current** flowing through one of two different paths, but rather the bit value is determined by the amount of charge stored on a capacitor. The capacitor is created with semiconductor technology, and is extremely small. The sensing of the charge is also very difficult, and handled by circuitry on the device itself. The information is placed on the capacitor by opening an electronic gate and establishing the proper charge level. Then, the gate is closed, and the charge maintained on the node by electronically isolating it from surrounding influences. However, the time which the charge can be reliably maintained in this manner is not long,

Figure 7.6. Bit Storage Elements for Semiconductor Memories. (a) Static Memory Cell. (b) Dynamic Memory Cell.

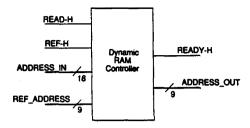

and so it must he re-established periodically. This is done by a "refresh cycle. which detects the appropriate bit values and refreshes the hits. The length of time between refresh cycles varies from memory to memory, but a common value is 8 msec: each row must **be** visited at least once every 8 msec. For this reason dynamic memory controllers **are** designed to periodically access rows to assure that the **data** is maintained in the memory cells.

The storage of the information in the cells is only a part of the memory problem. The bits stored must be organized in a reasonable fashion to access the information. The two most prevalent mechanisms **are** random **access** and serial access. As the name implies, random **access** memories **are** organized such **that the** information can be accessed in a random fashion. That is, each location has **the** same access penalty,  $T_A$ , and the order of access can be entirely random. The only requirement is a mechanism to decode an address of a specific location, and a **data** path such that any location accessed can provide **the** necessary information.

On the other hand, serial access mechanisms **are** organized such that the **data** is written and accessed in a serial fashion. Thus, the  $T_A$  varies depending on the location of the information in the memory, since the data must pass a mechanism for reading each bit. Examples of serial access devices include magnetic surface systems, such as tape and disk, and serial semiconductor systems, such as shift registers and charge coupled devices.

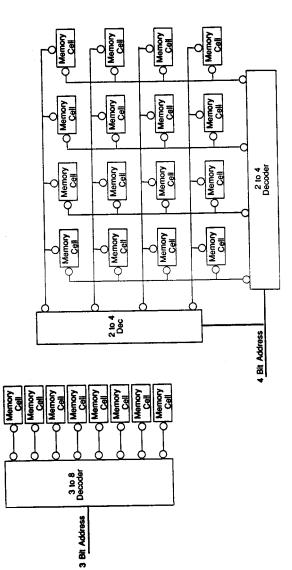

A simplified block diagram for the random access mechanism is shown in Figure 7.7. The size of the decoding mechanism is dependent upon the size of the array of memory elements; the number of bits in memories increases each year. The mechanism used to decode the address can be designed in a variety of ways. The two most basic mechanisms are the one dimensional (1-D) and two dimensional (2-D) decoding schemes. The I-D scheme accepts an N-bit address. and uses an N to  $2^{N}$  decoder to identify one of  $2^{N}$  individual elements. The location identified is then used in the read or write operation. The 2-D scheme accepts the

#### Chap. 7: Memory Systems

Figure 7.7. Random Access Memory Block Diagram.

N-bit address and divides it into two groups, which we will **call** X and Y. Thus, X + Y = N. These two groups of address lines control X to  $2^X$  and Y to  $2^Y$  decoders, which jointly specify a single element. Note that the memory cells used with the I-D arrangement need only have a single enable line, while the memory cells used with the 2-D arrangement need two enable lines. Thus, the I-D arrangement has a simple cell and a more complicated decoding scheme, while the 2-D arrangement has a slightly more complex cell, with less logic required in the decoding mechanism. These methods are depicted in Figure 7.8, which shows the addressing mechanism for an array of eight cells in a 1-D decoding **arrangement**. Mechanisms **USE** by manufacturers **internal** to memories include both the I-D and 2-D methods, as well **as** other variations of the **schemes**. Note that there is no reason to stop at two dimensions, and higher mechanisms could be useful in some systems.

The basic ideas of the preceding paragraphs apply not only to individual bits, but also to collections of bits. That is, many memories **are** not organized as 1-bit entities, but rather some multiple that makes logical **as** well **as** manufacturing **sense**. Memories containing Cbit words are very useful for storing BCD digits, and for **use** with 4-bit **microprocessor** systems. Memories organized 8 bits wide **are** useful for ASCII characters, 8-bit microprocessor systems, and **byte**-addressable memory systems. Combinations of **4-bit** and 8-bit systems can be used as **needed** to meet other system needs. In **dealing** with the memories or other storage elements, the principles used in identifying a bit in a memory array can be applied. That is, the individual components can be organized in a one dimensional fashion, a two dimensional fashion, or in some combination of the above schemes.

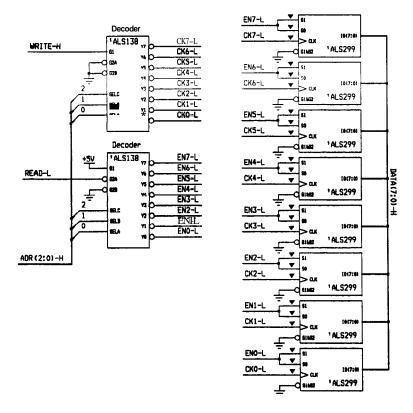

**Example 7.1:** I-D Design of a register set: Design a register array that contains eight registers, and that operates with an 8-bit bus. The array should have two control lines, a read line and a write line. Use individual registers in the ALS technology, and a one dimensional addressing scheme. How fast can information be made available on a read? What is the data requirement for a write?

Figure 7.8. Memory Cells Organized in 1-D and 2-D Memory Arrays.

One solution to this is shown in Figure 7.9. The register selected here is the 74ALS299, which has inputs and outputs on the same pin. The inputs not shown in the figure have been appmpriately disabled. With the enable lines (G1, G2) tied low, this device will output its information when the function select lines (S1, SO) are both low. When the function select lies are both high, the outputs are disabled, and a value can be accepted from the bus to the internal register. The address is decoded by two 74ALS138s. When the read line is activated, the function select lines of the appmpriate register are asserted. The delay from assertion of the read line to the output data stable is the sum of the enable-to-output-stabledelay of the **74ALS138** and the function-select-to-data-stabledelay of the 74ALS299. The sum of the maximum times is 39 nsec; typical times would be shorter. When the write line is asserted, the clock line of the **appropriate** register is activated. The loading of the register occurs on the low-to-high transition of the clock at the register, which corresponds to the high-to-low transition of the clock line in the figure, since there is a change of assertion level through the 74ALS138. The maximum delay through the 74ALS138 is 17 nsec. and the

Figure 79. Registers with One Dimensional Addressing.

data must be stable on the bus for 16 **nsec** prior to the rising edge of the clock (at the register).

The arrangement of the pans as shown in the figure gives a register **bank** with eight registers in ten **DIP** packages, and a power consumption of about 1.6 watts. This is not a very efficient use of the board space or system power, but the unit can meet some **requirements** for special systems.

The use of individual **registers** as shown in Example 7.1 can be used to meet some special requirements, but the normal manner of operation is to use memory elements that contain a larger storage capacity. Nevertheless, the same principles apply, and the memories can be organized in a one dimensional or two dimensional manner.

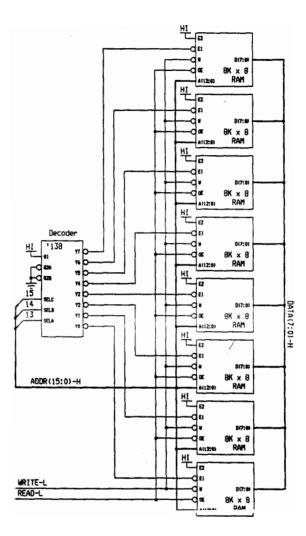

**Example 7.2:** 64-Kbyte static RAM system: Design a memory system for an 8-bit microprocessor system. The memory system is to contain 64 Kbytes of static RAM memory, using  $8K \times 8$  RAMs, such as the µPD4464 from NEC Electronics Inc. Do this design in two ways, first as a one dimensional scheme, then as a two dimensional scheme. Communication lines to the memory include the address and data buses, a write line and a read line. Write and read lines **are** asserted low.

The 4464 is an 8K **x** 8 RAM with thirteen address lines, two enable lines, an output enable, and a write line. One of the enable lines is asserted high, while the other is asserted low: the write line and the output enable are both asserted low. To attain the 64K space, eight separate memories are required. Figure 7.10 shows one of the possible I-D organizations that can be used. The lower address lines **are** shared by all memories; the current **requirements** of each input is only I  $\mu$ **a**, which does not cause loading problems. The upper **three** address lines **are** directed to a **3-to-8** decoder ('138), which enables only one of the memory chips. This allows sharing of all of the read and write lines, as only one **memory** element will be active at any one time. The **burden** is on the user of *the* system to be sure that the address lines do not change while the write line is **asserted**; such action will **cause the data** to be **corrupted** in **the** memory.

Note that this **arrangement** can be extended to include more memories by utilizing the unused enable lines of the 3-to-8 **decoder**. That is, additional decoders combined to make larger decoding systems (4-to-16; 5-to-32; etc.) can be used to make larger 1-D memory systems.

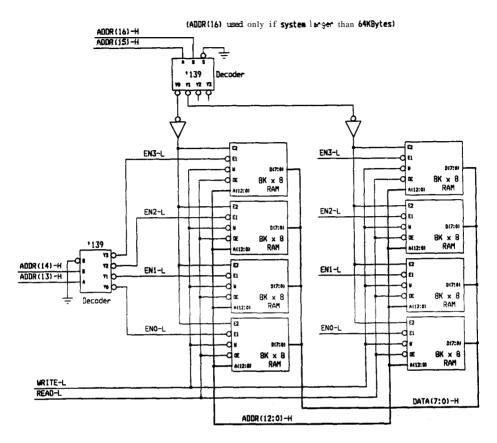

The two dimensional implementation is shown in Figure 7.11. Many of the characteristics **are** identical: the read and write lines are shared between all of the memories; the 13 least significant **address** lines **are** common to all memories, and the data bus is used by all chips. However, two **2-to-4** line decoders ('139s) are used to implement the decoding of the most significant address lines, instead of a single decoder. The use of the '139s allows for doubling the size of the memory (not shown) without the addition of **more** decoding **capability**. If the larger capability is not **needed**, then the function of the second '139 **can** be filled by an **inverter**.

The systems shown in Figures 7.10 and 7.11 demonstrate the use of decoders to make one and two dimensional systems. However, certain design criteria have not been considered in the discussion that must be taken into account in designing a specific system. For example, the time from chip enable to **output** valid for the uPD4464 is twice the time required for

Figure 7.10. 64-Kbyte Memory Array from 8K x 8 Memories; 1-D Organization.

output enable to output valid. If the speed of the system is critical, then a different **arrangement** may be **desired**, one in which the chips are **enabled** all the time, and the output enable lines and write lines activated as needed to perform **reads** and writes. This changes the configuration of the system, **since** the **read** and write lines can no longer be common to all *memory* chips, but the same basic concepts are still applicable to the memory.

Figure 7.11. 64-Kbyte Memory Array from SK x 8 Memories; 2-D Organization.

The concepts involved with the address mechanisms are not limited to the examples examined above. Consider the following example, in which dynamic memories are used to create a large random access memory. The addressing mechanism for identifying the appropriate memory module to activate is 1-D in nature, while the actual memories involved are selected in a 2-D fashion.

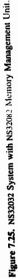

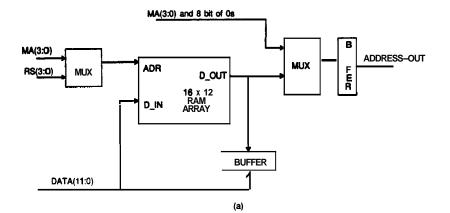

**Example 7.3:** Dynamic memory system: Design a memory to be used with the time multiplexed address/data bus of the NS32332 shown in Figure 6.10. The address will be supplied on the bus during **T1**, along with a data direction indication (DDIN). The memory should respond to the assertion of the address strobe(ADS-L) by initiating a memory request. If it is a mite, the data will become available during T3; if it is a read, the data should be s up plied as soon as possible, but no later than the beginning of T4. Use dynamic memories to provide as large a memory space as possible.

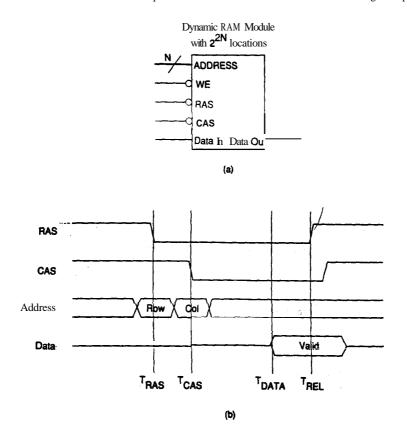

To discuss a system with dynamic memories, first let us examine **some** of the mechanisms of dealing with the memories. There are a number of device-specific characteristics, but the basic cycle for a **read** in a dynamic RAM is shown in Figure 7.12(b). Usually, large RAMs such as the dynamic RAMs shown here require so many **address** lines that the address divided into two parts and time multiplexed on a single set of address lines. These two parts of the address are called the "row address" and the "column address." After the mw address is presented on the address lines for a required period, the mw address strobe (RAS) is asserted. The address. After a required strome, the column address strobe is asserted (CAS), and the memory access begins. Some time later, which is the access time of the memory, the data becomes valid ( $T_{\text{DATA}}$ ). When the RAS is released ( $T_{\text{RED}}$ ), the output data will return to the tri-state condition. A write requires the same operation, but the write enable line is asserted during the operation.

Figure 7.12 Dynamic RAM. (a) Symbol. (b) Timing f a Read Cycle.

Chap. 7: Memory Systems

and the data is asserted on the data lines by the module requesting the write action. As long **as** the rows are accessed every  $T_{REFRESH}$  the information should be maintained. Thus, one of the design requirements is to access each row within the refresh time, which in many memories is 8 msec.

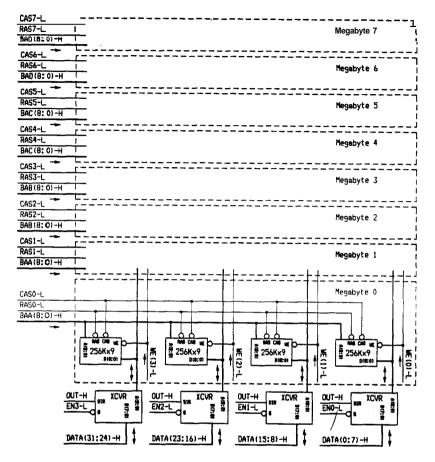

These individual packages can be combined in reasonable ways to be used in systems. For example, for bused systems the data in and data out pins can be tied together and connected to the system bus with transceivers. One commonly used configuration is to put nine individual memory modules on a single in line package (SIP), which is sufficient for a byte plus parity. This SIP module is used in this example; each SIP contains 256 Kbytes of **information**. SIP modules that contain 1 Mbyte and 4 Mbytes of **information are** also available.

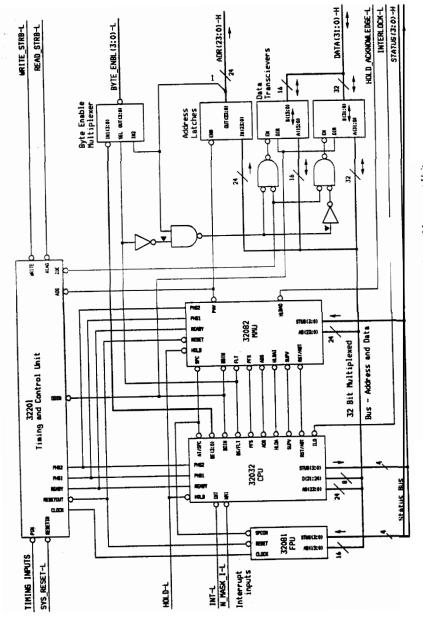

Using modules with 256 Kbytes, an 8-Mbyte memory can be constructed with just 32 modules. Drawings of the memory **are** contained in Figure 7.13(a)–(c). A more complete set of drawings are found in Appendix B. Figure 7.13(a) contains the memory elements themselves and the data buffering transceivers. Note that the data lines are buffered from the bus system with a transceiver. Although the data line of each memory module does not present a large load, there **are** enough individual memory modules in the system to provide a nontrivial load. The buffer (transceiver) **has** the effect of isolating the loads from the bus and minimizing the effect of the wires required to carry the signals. Also note that the organization is such that the 4 bytes required for a 32-bit word (assuming that the word is aligned correctly) are all accessed with the same RAS and CAS line. Accesses of information nor aligned on a word boundary must use the proper set of lines, and this is the responsibility of the initiator of the transaction.

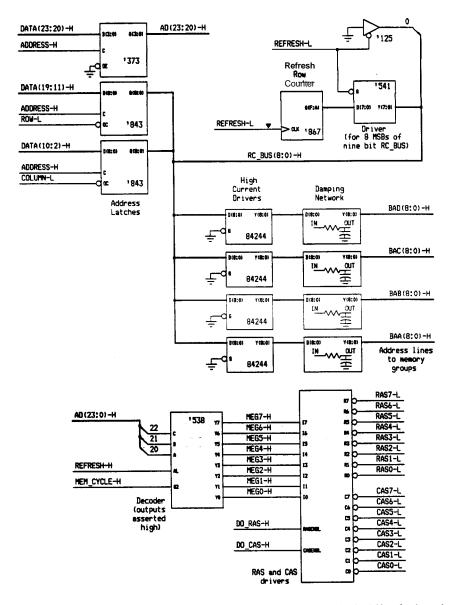

The generation of row and address strobes is done by drivers capable of supplying a sufficient amount of current, and these **are** represented in Figure **7.13(b)**. The selection of the appropriate megabyte is accomplished by a decoder, which is a **1-D** technique. The most significant address lines **are** used to identify the appropriate megabyte; expanding to a 16-Mbyte address space would require an additional decoder. The **decoding** is done by a '538, which is chosen for two reasons. The first is that the **assertion** level of the output is selectable, so that the assertion level is selected to match the gates **that** follow the decoder. In this case, the gates that follow are '**801s** which were selected for their drive capability: each RAS and CAS line has 36 individual memory modules attached to it (32 data, 4 parity). The second reason for the selection of the '538 is that, with the proper activation of the control signals. all of the outputs can be asserted simultaneously. This is very useful to allow all 8 Mbytes to perform a refresh cycle at the same time.

The address latches **are** also included in Figure **7.13(b)**. The latches **accept the** address during the first cycle of the transfer, and the address is then broken into **three** groups: nine bits for the row address, nine bits for the column address, and the most significant bits for identification of the active megabyte. The two **least** significant bits **are** not included, since the system is byte-addressable, and these bits merely identify the appropriate byte. Since all 4 bytes **are** accessed on every cycle, the least significant address **bis** (**RC\_BUS**) is then presented to four sets of high **current** drivers. which have the capability

Figure 7.13(a). 8-Mbyte Memory System: Memory Array and Data Buffering Transceivers.

of providing the current needed by the collection of memories. The outputs of the high **current** drivers are conditioned by damping networks to minimize the undershoot and overshoot, which will occur **when** switching the **lines between** high and low logic levels. The address **lines** of the individual memories are supplied from the damping networks by four separate sets of **lines** (BAA-BAD). This buffering is **required to** provide sufficient drive capability, since each address line (**BRA(0)-H**, for example) **supplies the address to** 72 **separate memory** modules. Also included is the mw counter **that** identifies **the appropriate** address for **refresh**. These **memories refresh** two mws simultaneously; so the **0 line** is not involved in the count.

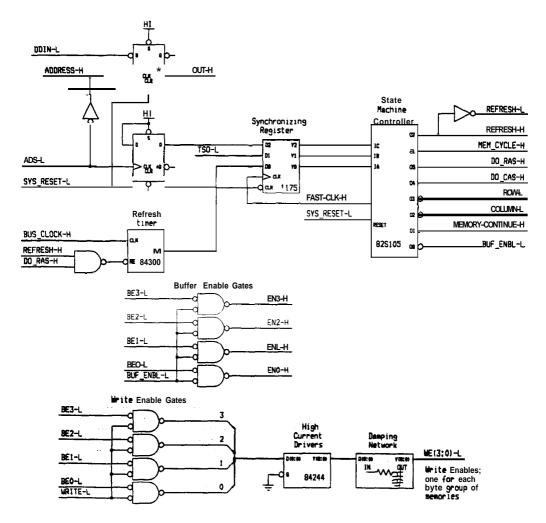

The **control** logic shown in Figure **7.13(c)** coordinates **the** assertion of all of the signal lines. The **coordinator** of all of **the** work is a state machine

Figure 7.13(b). 8-Mbyte Memory System: RAS and CAS Logic; Address Latches and Drivers.

Figure 7.13(c). 8-Mbyte Memory System: Control Logic.

controller (82S105), which has the responsibility of asserting the signals in the order explained above. It is driven by a clock (FAST\_CLK), which is four times faster than the bus clock(BUS-CLOCK) and synchronized with it. Thus, the bus clock and the fast clock are generated externally and supplied a the memory system. Using these two clocks in this manner allows the signals to be created in a timely fashion. The refresh counter is connected to the bus clock, which it courts down to identify the proper time to do a refresh. When the refresh is needed, it sets an internal flag that provides an input to the state machine; when the refresh is recognized the flag is reset. The other inputs to the state machine are a flag to identify the start of a memory cycle. and the signal TSO. which comes from the timing unit of the **microprocessor** to identify the end of a cycle. The outputs of the state machine are used to assert RAS. CAS. and the other signals associated with the dynamic RAM. The signal MEMORY-CONTINUE is used to inform the rest of the system that the memory information is ready. This is necessary since the RAM may be in the middle of a refresh cycle when the system makes a memory request.

The two sets of gates in Figure 7.13(c) are to assert the write enable lines and the data transceiver enable lines at the appropriate time. The time is identitied by the state machine controller, but the appropriate byte is identitied by the byte enable signals generated by the processor. This 7-D mechanism chooses the appropriate bytes. One dimension is provided by the address: the second dimension is supplied by the processor. Thus, the processor must assume the responsibility of reading and writing information that is not aligned exactly on a 32-bit boundary.

A photograph of such a system is shown in Figure 7.13(d). This astom contains 8 Mbytes of memory and a 32032 system.

The concepts discussed in this section are applicable to a wide range of memory organizations and considerations. For most processing done by general purpose computers, random access is required to the memory. This is true of core memories, semiconductor memories, and other technologies as well. Hence, the individual elements must be individually addressable and accessible through the

| المحمدات المراكل أتكأر محمد                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1111 | 1014     | 4111   | 1414  |      | ****     | 44.84 |      | 1114    | ۰ <u>۶</u> ۰ |         |   |      | af   | Ĉ.               |     | 1341  | 1110  | 1114 |       | `uii |      |        | 4446     |         |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|--------|-------|------|----------|-------|------|---------|--------------|---------|---|------|------|------------------|-----|-------|-------|------|-------|------|------|--------|----------|---------|-----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      | ****     |       | (1)+ | mi      | . °          |         |   |      |      | 21.00<br>(11.00) | ÷ . |       | - · · | **** | ****  |      | **1* | 1165   | 1116     |         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | `ii  | ****     | ,,,,,  | ,,,,, | 1100 | 1100     | 1111  |      | ****    | ۰.           | 12.722  |   |      |      |                  |     |       | 1144  |      |       |      |      |        | ****     |         | 2   |

| ¢                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100  | 1111     | 1044   |       | 4818 | 1000     |       | 1994 | 1416    | •            |         |   |      |      |                  |     |       |       |      | ****  |      |      |        |          |         | 2   |

| TCN 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |          |        |       |      | ****     | -     | 7444 |         |              |         |   |      |      |                  |     | 1464  | ****  |      |       |      |      |        | ****     |         | 2   |

| -10 N 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | **** |          | ****   |       | 1685 | 1010     |       | 1618 | ****    |              |         |   |      |      |                  |     | ****  |       |      |       |      |      |        |          |         | ÷.  |

| 6/25/87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | ****     | ``•••` | 1614  | **** | 10.05    |       |      |         |              |         |   |      |      |                  |     |       |       |      |       |      |      |        |          |         | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | in a | 1111     | ****   | ****  | **** | 1414     | `ma`  |      |         |              |         |   |      |      |                  |     |       |       |      |       |      |      |        | ****     |         | į.  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      | 1411     |       |      |         |              |         |   |      |      |                  |     | 1.00  |       |      | ****  |      |      |        | 1924     | ****    | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        | 1111  |      |          | 11.15 |      |         | •            |         |   |      | ٠.   |                  |     |       | ****  | 1611 | ****  |      |      | ****   |          | 1111    | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          | `,     |       |      | ****     |       | **** | ·       |              |         |   |      |      |                  |     |       |       |      |       |      | **** |        |          | ••••    |     |

| 3 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | ****     | ****   | 1494  |      |          | ****  |      |         | 18           |         |   |      |      |                  |     | ****  | ****  | im   | ****  | **** |      |        | (11)     | ****    | 3   |

| hehis non 12 hen 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | <b>.</b> | 1114   |       |      | <b>`</b> |       | 1161 | - ini - |              |         |   |      |      |                  |     |       | ****  | **** | 1414  | 1116 | **** | ****   | ****     | ****    |     |

| nch32 non32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |          | -      |       |      |          |       | 1100 | °       |              |         |   |      |      |                  |     |       |       | **** |       |      |      | ****   | 1110     | 1899    |     |

| 6/25/87 6135/67 6/25/67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |          | in.    |       |      |          | 1007  |      |         |              |         |   |      |      |                  |     | -iiii |       | 1111 | 100   | 1.00 | ` mi |        |          | 1010    |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      |          |       |      |         |              |         |   |      |      |                  |     |       |       |      |       |      |      |        |          |         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      |          |       |      |         |              |         |   |      |      |                  |     |       |       |      |       |      |      |        |          |         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      |          |       |      |         |              |         |   |      |      |                  | 11  |       |       |      |       |      | ÷.   | ÷È.    | 1.1      |         |     |

| and the second se |      |          |        |       |      | 1.1      |       |      |         |              |         |   |      |      |                  |     |       |       |      |       |      | 11   |        |          |         | 2   |

| A REAL PROPERTY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      |          |       |      |         |              |         |   |      |      |                  |     |       |       |      |       |      |      |        | 1,6      |         | 5   |

| C #1420386-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |          |        |       | 24   |          |       |      |         |              |         |   |      | . :  |                  |     |       |       |      |       |      |      | 11     |          |         |     |

| AFTENIA<br>REALOWER-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | ÷        |        |       |      |          |       |      |         |              |         |   | C    |      |                  | 2   |       |       |      |       |      |      |        |          |         | 5   |

| 5.0.51 Summer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | ÷.       | 3      |       | 11   |          |       |      |         |              |         | 1 |      |      |                  |     |       |       |      |       |      |      | :      |          |         | ò   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          | 1      |       |      |          |       |      |         |              |         |   |      | - 1  |                  |     |       | 11    |      |       |      |      | $\sim$ | - 1      |         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      | 1.1      |       |      |         |              |         |   | i an | - 28 |                  |     |       |       |      |       |      |      | 1      | $\neg$   | ÷.      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          | 8      |       |      |          |       |      |         |              |         |   |      |      |                  |     |       |       |      |       |      |      | ÷.     | · •      |         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      |          |       |      |         |              |         |   |      |      |                  |     |       |       |      |       |      |      | ŝ      | $\sim 1$ | 5       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •    | e (19    |        |       | 1.   |          |       |      |         |              |         |   |      | ::   | ::               |     |       |       |      |       |      |      | 6      | ~ 8      | - it.   | 5   |

| 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |          |        |       |      |          |       |      |         |              |         |   |      |      |                  |     |       |       |      |       |      |      |        |          |         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.   |          |        |       |      |          |       |      |         |              |         |   |      |      |                  |     |       | . ,   |      |       |      |      |        |          | د ز     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      |          |       |      |         |              |         |   |      |      |                  |     |       |       |      | \$ -  |      |      |        |          | 20      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          |        |       |      |          |       |      |         |              |         |   |      |      |                  |     |       |       |      |       |      |      |        |          |         |     |

| the second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -    | <i></i>  |        |       |      | ١        |       |      |         |              | 400     | 1 |      |      |                  |     | 1     |       |      |       | •    |      | •      |          | ر<br>با | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |          | î<br>H | П     |      |          |       | Π    | Ť       | i T          | <u></u> |   | •    |      |                  |     | 'n    |       |      | ,<br> |      |      |        |          | ,       | ā., |

Figure 7.13(d). 8-Mbyte Memory System: 32032 System with 8-Mbytes Dynamic RAM.

Chap. 7: Memory Systems

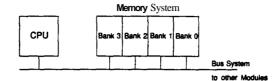

Figure 7.14. CPU with Four Bank Interleaved Memory System.

bus structure. The organization of the memory to access the addressed location can be done in a **1-D**, 2-D, or related fashion, as long as only one location is **actu-**ally enabled.

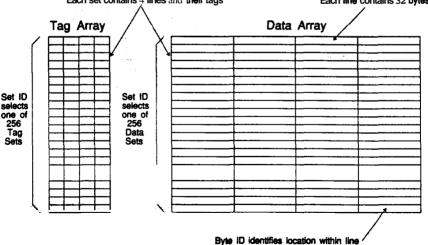

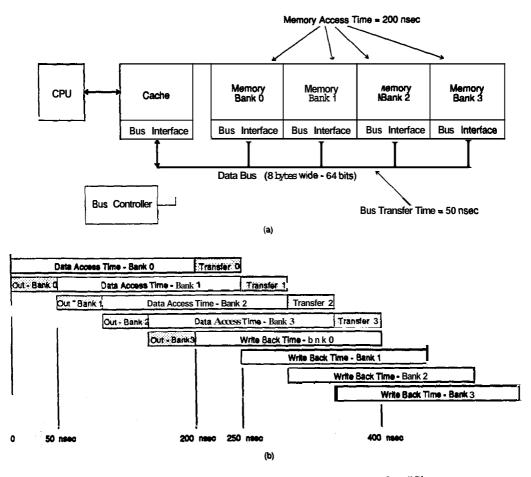

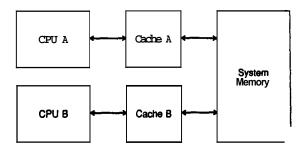

Creating larger memories. or memories with differing characteristics, can be accomplished by combinations of the mechanisms discussed here. For example, one of the figures of merit for a memory system is bus bandwidth, represented in **bytes/sec**. Since information **can** be transferred over a bus structure faster than it can be retrieved from a large memory, one of the ways to increase the bandwidth is to create memory in banks, and interleave the memory banks in time. Consider the system shown in Figure 7.14. The memory requests **are** sent to all four banks. and the response sent to the **processor** in different time slots. If the **bus** width is 4 bytes, and the memory access time is 200 nsec, and if 4 bytes can be sent every 50 nsec, then all four banks is individually organized as a random access system, and interfaces to the bus system in a manner which will allow the transfers to occur in a reasonable fashion. This requires more circuitry, but speeds up the overall data rates.

The choice of a memory organization and **the** technology in which it is implemented must reflect the constraints of **the** entire system. The choices will be based on optimizing performance for a given set of resources. If a major requirement is speed, then the designer *can* afford to put more resources (silicon **real** estate, board space, power, **etc.**) in the memory to **provide** for a minimum **response** time. If the critical resource is power, such as a battery operated system. then the complexity cannot be **increased**, and the parts and design **mechanisms** are optimized for minimal power **consumption**. Nevertheless, the system architect can choose **from** a variety of **memory** and **processor organizations** to create a system that will fit a **particular** need.

# 7.3. Virtual Memory Systems: The Illusion of a Memory Space

One of the principal tenets of stored program computers is that the program resides in a memory space, and the instructions are extracted from memory and executed. If the instruction calls for data manipulation, then the **data** is identified and **utilized** to perform whatever calculations **are** called for by the instruction. In **most** programs the data **also** resides in the memory, **at** least **at** the beginning of the **program**, when data is brought into the **system**, or at the end of the program, when data is **prepared** for output to the destination **device**. Thus, the program is **loaded** into the memory, **started**, and whatever data manipulations **are** called for by the program **are executed**. The program then terminates, and the system moves on to execute the next **program**.

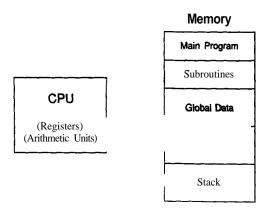

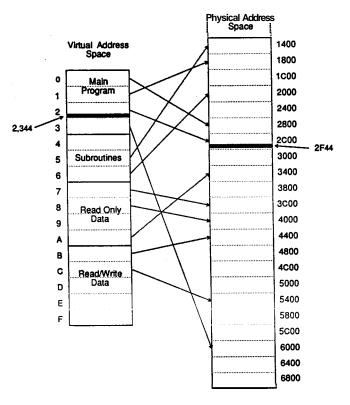

The statements made in the previous paragraph reflect some assumptions **often made** about the use of the computer. Most machines used today have a collection of system facilities that we have come to call the operating system **(OS)**. The operating system has the responsibility of doing many things, among them transferring programs and data to and from memory. When the program has been **loaded**, the operating system **starts** execution of the program at **scene** predetermined point. However, most users of computer systems do not consider the effect of what the OS is doing; rather, they have a "model" of what the machine is, and they **are** operating under the assumption that the model is at least functionally **correct**. Such a model may appear as shown in Figure 7.15.

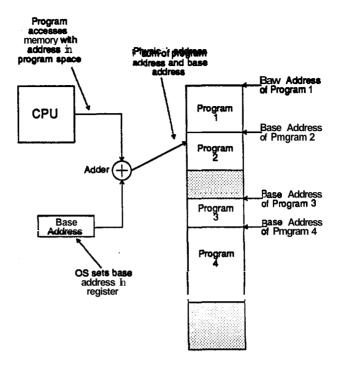

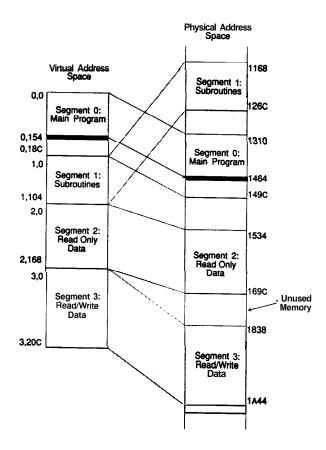

In multiprogrammed systems, we know that other programs will also be utilizing the machine, but generally we think of the machine as "ours," at least for the duration of our program. Knowing that a program will have a program section and a data section. we often think of the machine as shown in Figure 7.16. This simple block diagram shows only the memory and the processing capability. The possible connection between the two is identified by the instruction set. and using that instruction set we are able to perform work. where work is defined as manipulating data. The machine as seen in Figure 7.16 is what we think we have: hence, we call it a "vinual machine." In our mental model of the machine, the program starts at location zero and executes through the instructions in order. In the physical machine, the program was not loaded at location zero; rather, the operating system placed **the** information at a location which, for some reason, was available to be used. The operating system, then, is responsible for ascertaining what pans of memory are available: if no memory is available. then the OS makes some memory available. In a location known to the operating system there is kept a correspondence between the vinual space, which the program has the illusion of controlling, and the physical space, which contains the actual information being manipulated.

The mechanism used to define the relationship between the memory space that the program thinks it is **controlling**, and the actual memory locations being utilized, is called a "virtual memory mapping." The memory mapping mechanism

Figure 7.15. Block Diagram cf a "Model" Computer.

Figure 7.16. User Model for a Computer and Program

is therefore responsible for convening an address issued by **the program** (the virtual address) to an address that will be used by the memory system to access the **information** (the real address). Two common mechanisms often considered are segmentation and paging, and some systems utilize both concepts in their implementation. It is not our intention to discuss the pros and cons of one mechanism over another. That can be dealt with more effectively in a discussion of operating systems themselves [BrHa73, PeSi83, Deit84, BiSh88]. Rather, our interest is in the low level operations required to make **virtual** memory work.