EFOP-3.4.3-16-2016-00009

A felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása a Pannon Egyetemen

# FPGA-BASED EMBEDDED SYSTEM DEVELOPMENT

(VEMIVIB334BR)

SZÉCHENYI 2020

Created by Zsolt Voroshazi, PhD

voroshazi.zsolt@mik.uni-pannon.hu

Magyarország Kormánya

BEFEKTETÉS A JÖVŐBE

#### 5. VIVADO – EMBEDDED SYSTEM

Adding GPIO peripherals to BSB from IP Catalog

BEFEKTETÉS A JÖVŐBE

# **Topics covered**

- 1. Introduction Embedded Systems

- 2. FPGAs, Digilent ZyBo development platform

- 3. Embedded System Firmware development environment (Xilinx Vivado "EDK" Embedded Development)

- 4. Embedded System Software development environment (Xilinx VITIS "SDK")

- 5. Embedded Base System Build (and Board Bring-Up)

- 6. Adding GPIO Peripherals (from IP database) to BSB

- 7. Adding Custom (=own) Peripherals to BSB

- 8. Development, testing and debugging of software applications Xilinx VITIS (SDK)

- 9. Design and Development of Complex IP cores and applications (e.g. camera/video/audio controllers)

## **Important notes & Tips**

- Make sure that the path of the Vivado/VITIS project to be created does NOT contain accented letters or "White-space" characters!

- Have permissions on the drive you are working on:

- If possible, DO NOT work on a network / USB drive!

- The name of the project and source files should NOT start with a number, but they can contain a number! (due to VHDL)

- Use case-sensitive letters consistently in source file and project!

- If possible, the name of the project directory, project and source file(s) should be different and refer to their function for easier identification of error messages.

- The directory path should be no longer than 256 characters!

#### XILINX VIVADO DESIGN SUITE

Adding IP cores to the Embedded Base System

BEFEKTETÉS A JÖVŐBE

#### Task

- Vivado Block Designer

- Add IP (Intellectual Property) cores to the formerly elaborated block design (Embedded Base System) from the IP Catalog,

- Parameterize IP blocks, set connections, interfaces, address, and external ports (modify .XDC if needed),

- VITIS SDK

- Customize compiler settings,

- Creating a software application (from pre-defined template)

#### Main steps to solve the task

- Create a new project based on previous laboratory (04.) by using the Xilinx Vivado (IPI) embedded system designer,

- LAB01 project → Save as... → LAB02\_A

- Select and add GPIO peripherals to the base system

- Parameterize and connect them, make external ports

- Overview of the created project,

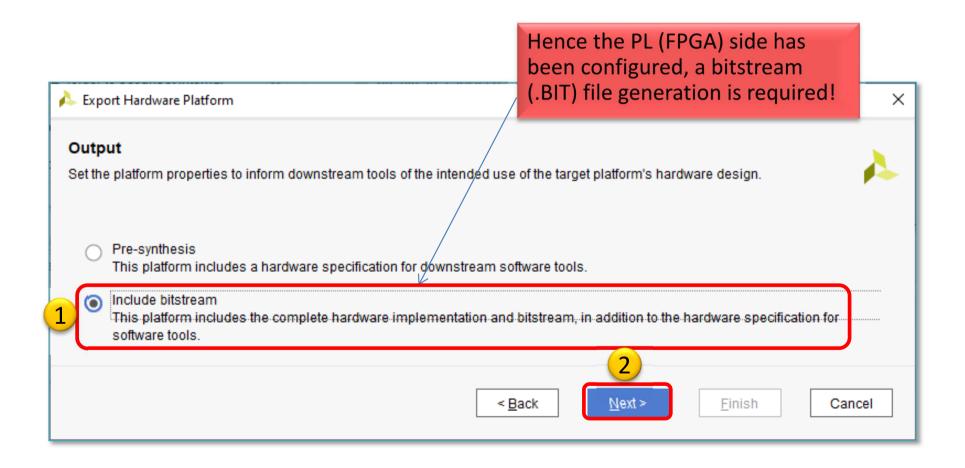

- Implementation and Bitstream generation (.BIT) is now necessary, because PL side will also be configured!

- Create peripheral "TestApp" software application(s) running on ARM by using the Xilinx VITIS environment (~SDK),

- Verify the operation of the completed embedded system and software application test on Digilent ZyBo.

#### XILINX VIVADO DESIGN SUITE

LAB02\_A. PUSH BUTTONS, DIP SWITCHES (GPIOs)

BEFEKTETÉS A JÖVŐBE

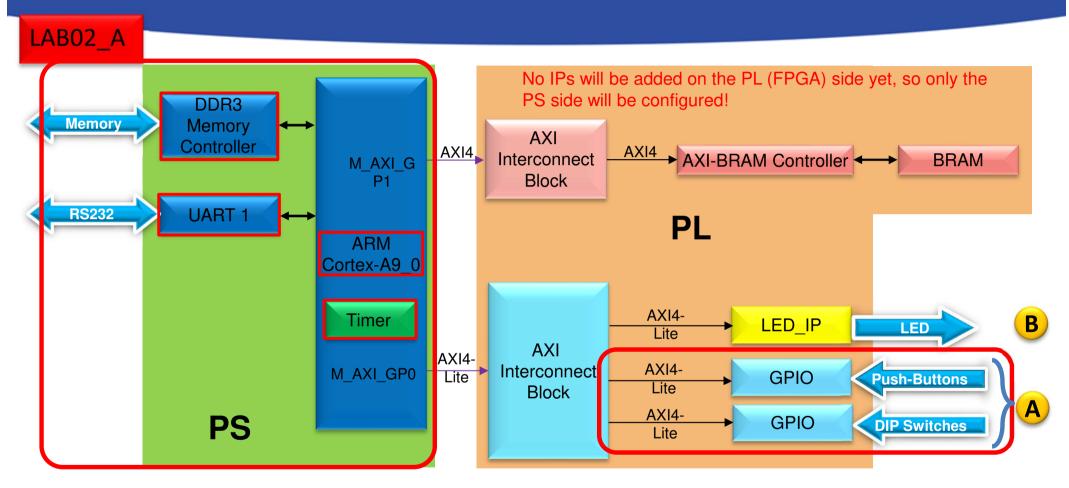

#### Test system to be implemented

#### PS side:

- ARM hard-processor (Core0)

- Internal OnChip-RAM controller

- UART1 (serial) interface

- External DDR3 memory controller

- Global Timer

#### PL (FPGA)

- (A) LAB02\_A: GPIO inputs

- PBSs: Push Button (nyomógomb kezelő)

- DIPs: Switches (kapcsoló kezelő)

- (B) LAB02\_B: GPIO outputs

- Custom LED controller

#### Project – Open / Save as...

- Start Vivado

- Start menu → Programs → Xilinx Design Tools → Vivado 2020.1

- Open the previous project! (LAB01)

- File → Project → Open... / Open Recent...

- - ctdir>/LAB01/<system\_name>.xpr → Open

- File → Project → Save As... → LAB02\_A

- (This will save former project LAB01 as LAB02\_A)

# Modify Zynq PS settings

- Open Design Sources → system.bd blokk design (double click)

- Open Processing\_system7\_0

- PS-PL configuration:

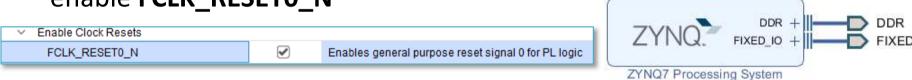

- > General → Enable Clock Resets: enable FCLK\_RESETO\_N

Design Sources (1)

✓ ■ \*\* system\_wrapper(STRUCTURE) (system\_wrapper.vhd)

system(STRUCTURIII) (system.vhd) (1)

processing system7 0

... system\_i : system (system.bd) (1)

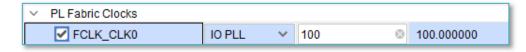

- > AXI Non Secure Enablement: GP Master AXI interface enable M\_AXI\_GP0 port!

- Clock configuration:

- PL Fabric Clocks: enable FCLK\_CLKO (100 MHz IO PLL)

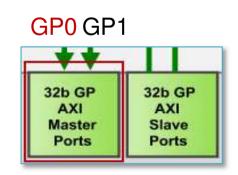

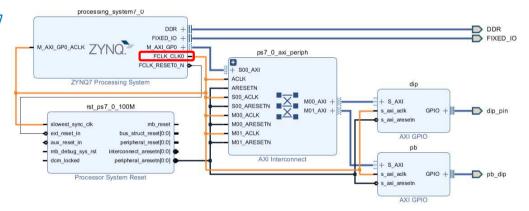

# Zynq PS – Block diagram

- Examine, that the previously enabled ports:

- GPO AXI Master interface,

- FCLK\_CLKO PL-side clock,

- FCLK\_RESETO\_N reset port are visible now?

— What do you think about their functionality?

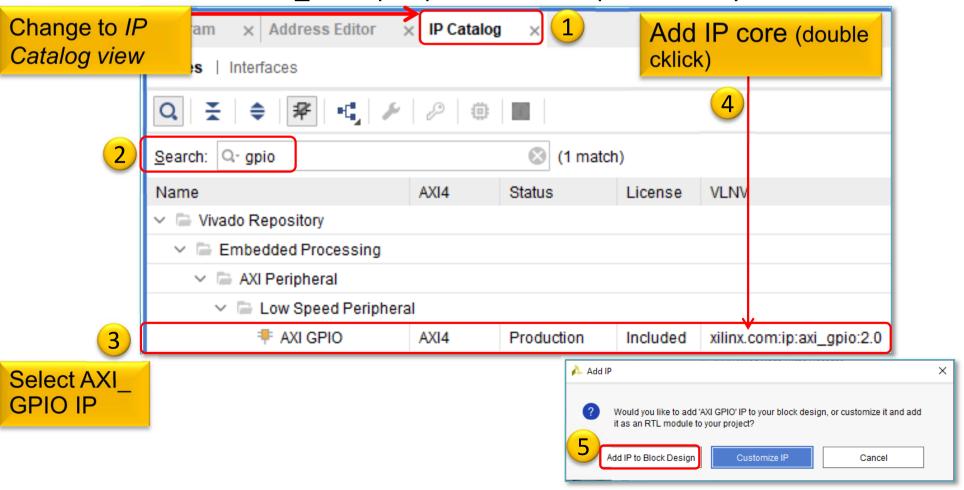

# Adding and connecting AXI GPIO peripherals to the PL-side

- Adding new IP cores possible ways:

- a) Block Diagram View → Add IP 🕕 OR

- b) Open IP Catalog → Select IP → Double click Add IP to Block Design 📭

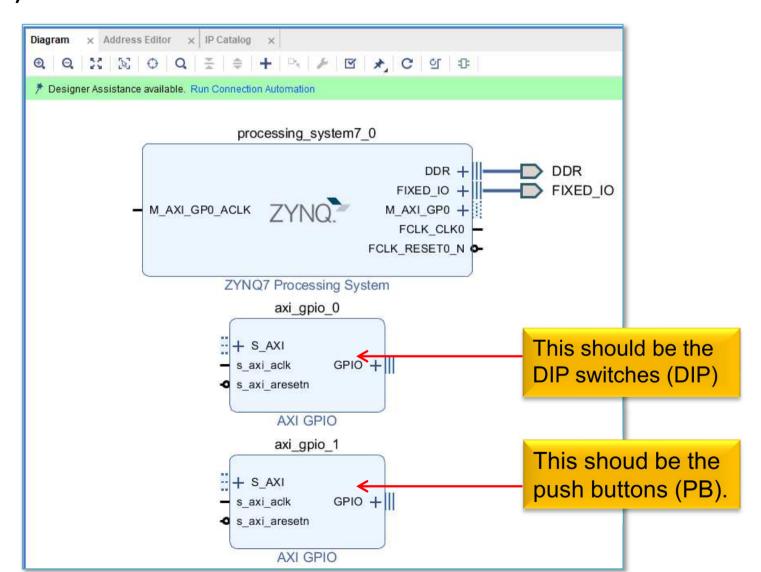

- Add 2 PL side AXI\_GPIO peripherals to the processor system

# Adding and connecting AXI GPIO peripherals to the PL-side (cont.)

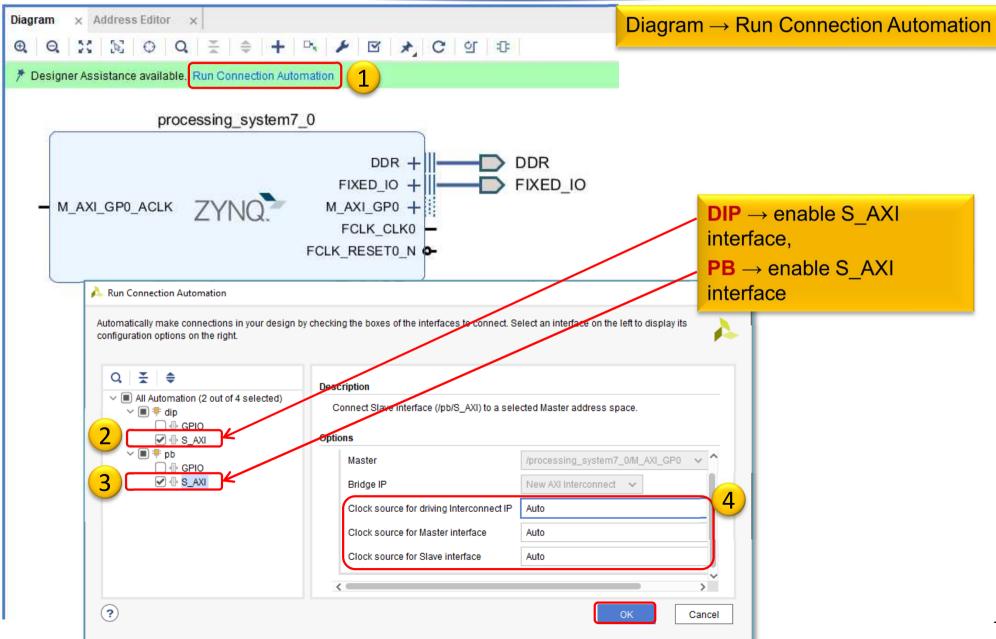

- For each IP modul (e.g. AXI\_GPIO) the following should be set:

- a.) interface connection between the IP modul and bus system (AXI),

- b.) mapping IP modul to the PS address space (Base-High Addresses),

- c.) assigning I/O ports of IP modules to external ports,

- d.) finally, assigning external ports to physical

FPGA pins (.XDC editing) I/O planning.

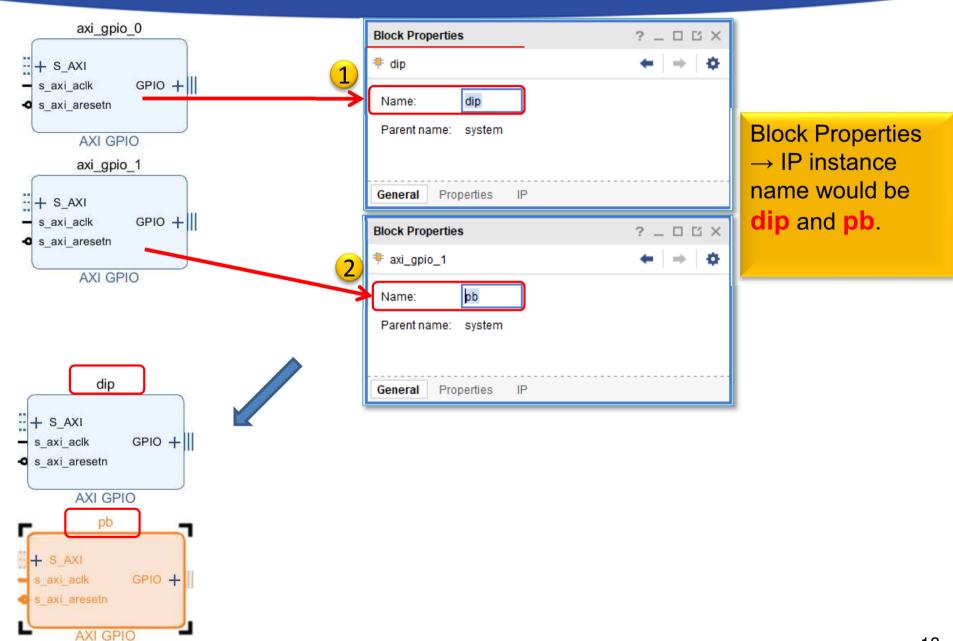

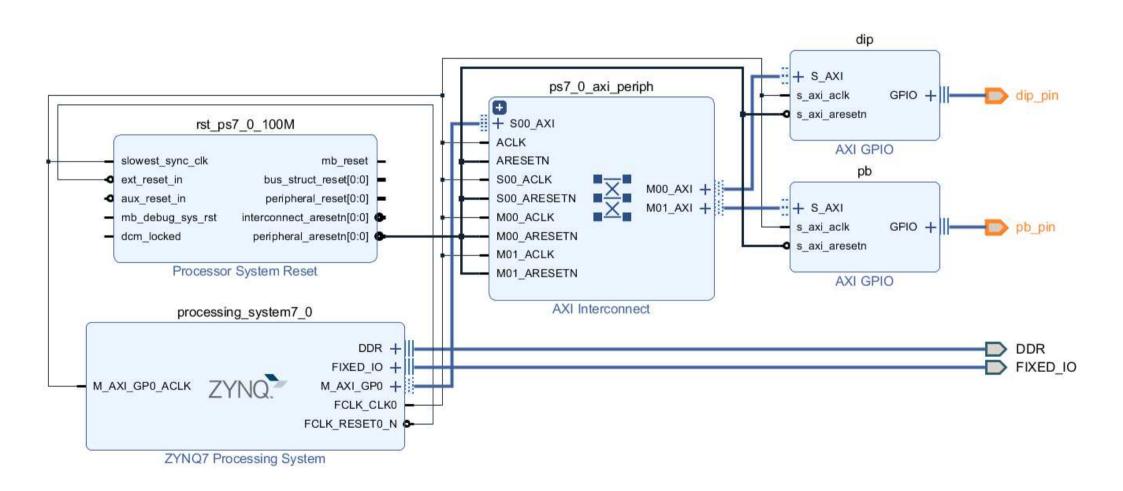

#### Adding GPIOs – Block Diagram view

AXI GPIO\_0 as DIP switches (DIP) and AXI\_GPIO\_1 as push buttons (PB).

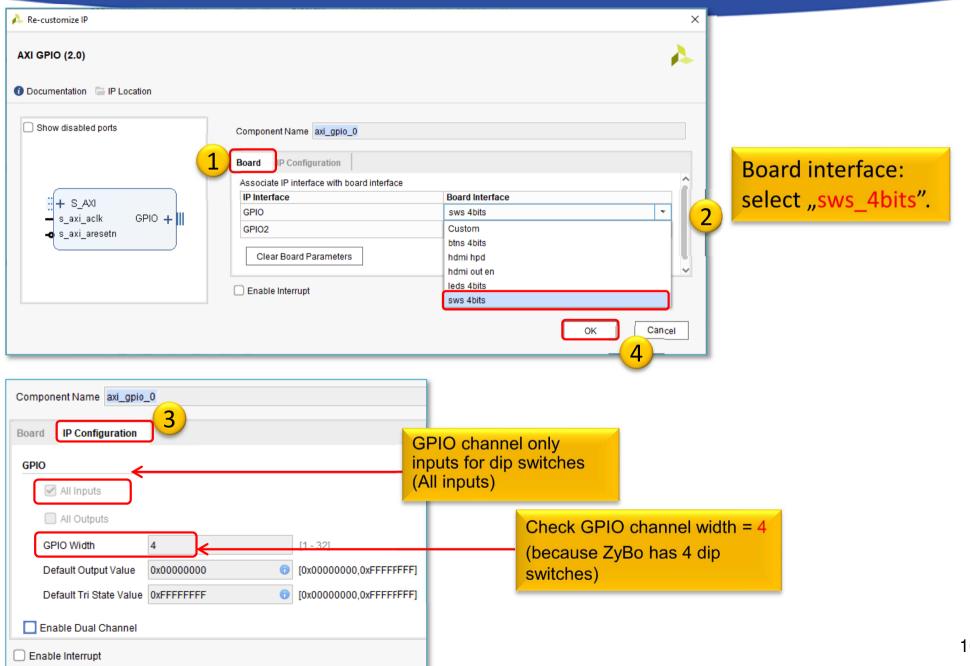

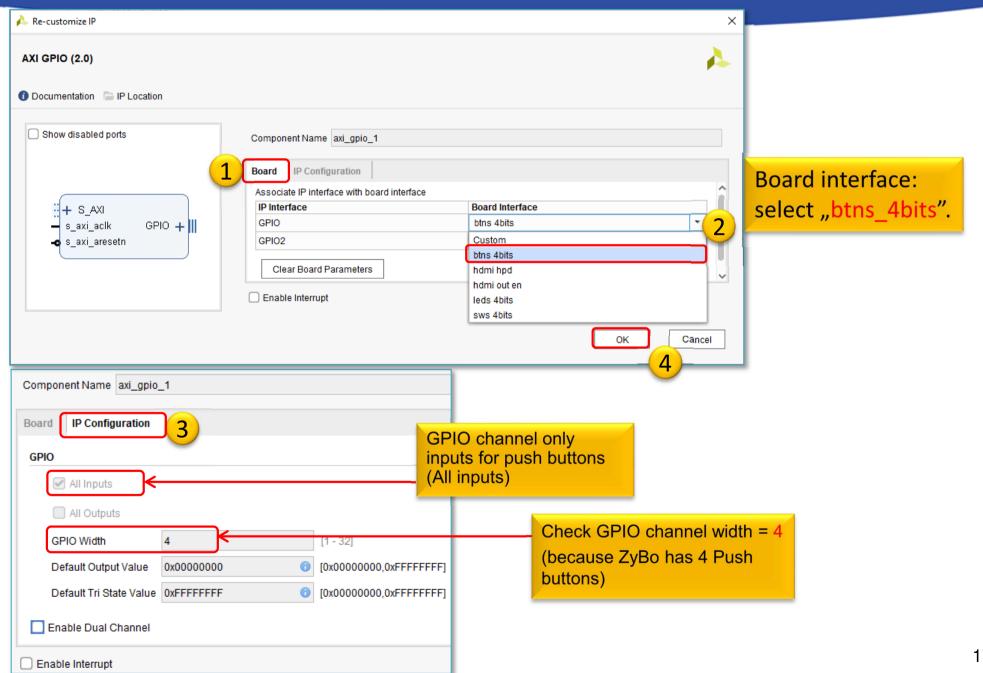

#### Set AXI\_GPIO peripheral - Dip switches

#### Set AXI\_GPIO peripheral - Push buttons

# Renaming AXI GPIO peripherals

# Connecting AXI GPIOs (autorouter)

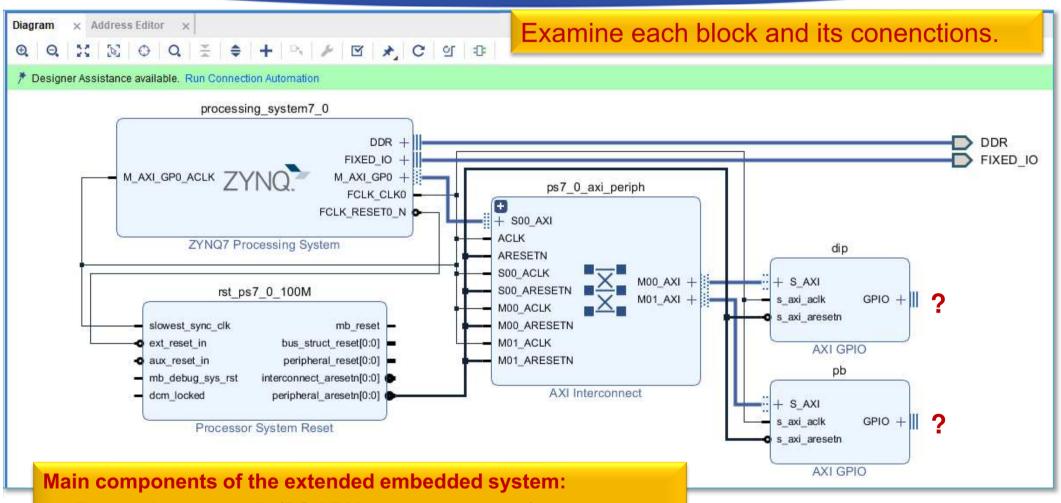

# Block Design – Analyzis

- Processing system7: (PS ARM processor system)

- Processing system7 axi periph: AXI bus interface

- Rst\_processing\_system7\_100M: PS/PL reset generator

- dip: AXI GPIO for DIP switches (PL side)

- pb: AXI GPIO for PB push buttons (PL side)

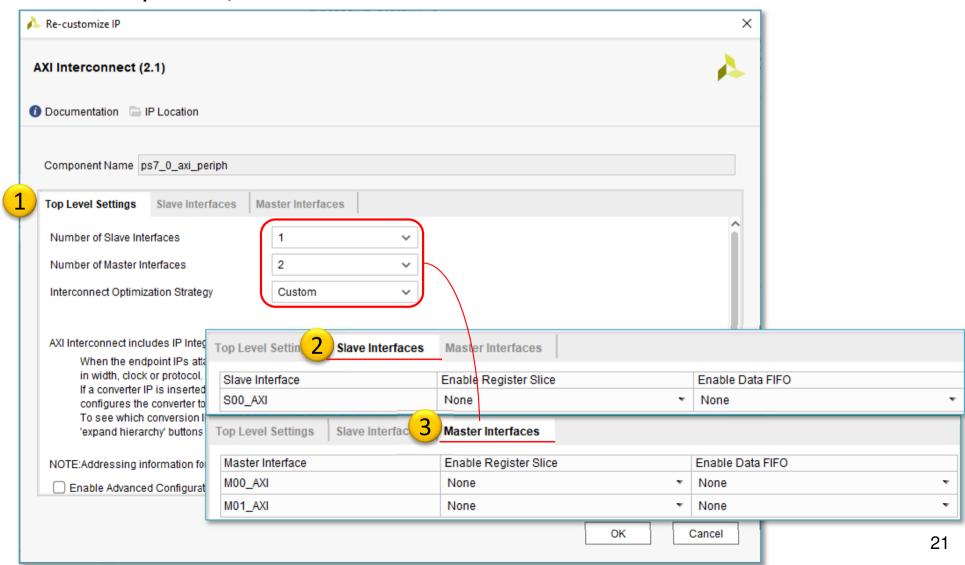

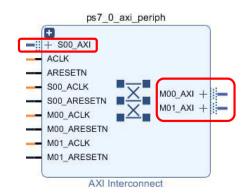

### Analyzis - Processing\_system7\_axi\_periph

#### Analyze the parameters of AXI peripheral interface:

• How many slave-, and master interfaces does it have?

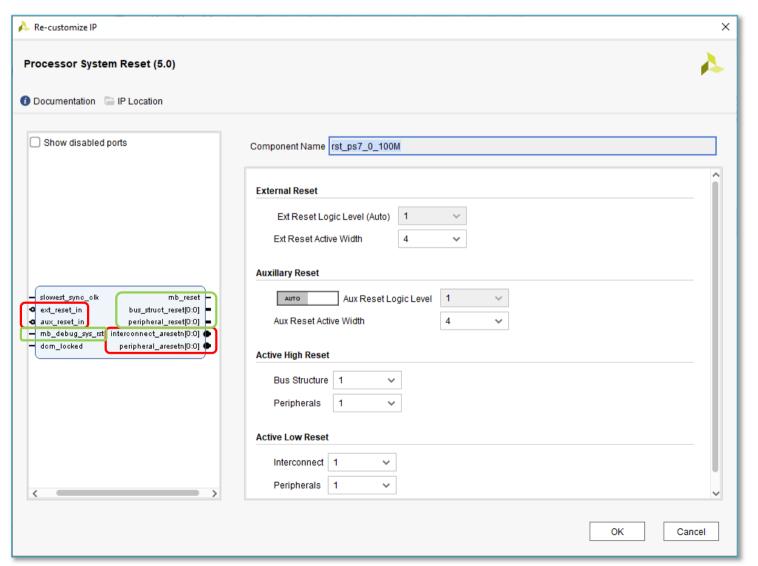

#### Analyzis – Rst\_Processing\_system7 (Reset)

#### Analyze the parameters of AXI reset generator:

How many low-/and high assertion reset signals does it have?

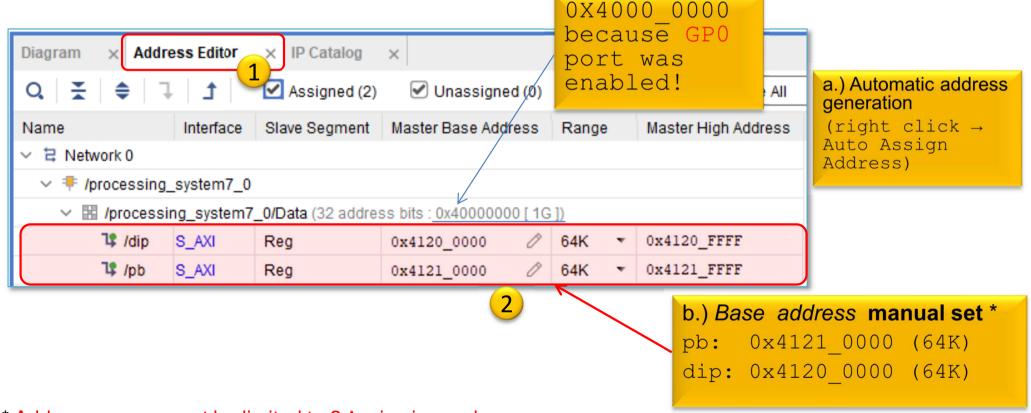

## Set memory addresses – AXI GPIO

- Block Design → select "Address Editor" tab

- Map "unmapped" GPIO IP peripherals into the memory address space (automatically or manually)

<sup>\*</sup> Address ranges must be limited to 2 ^ n in size and must not overlap!

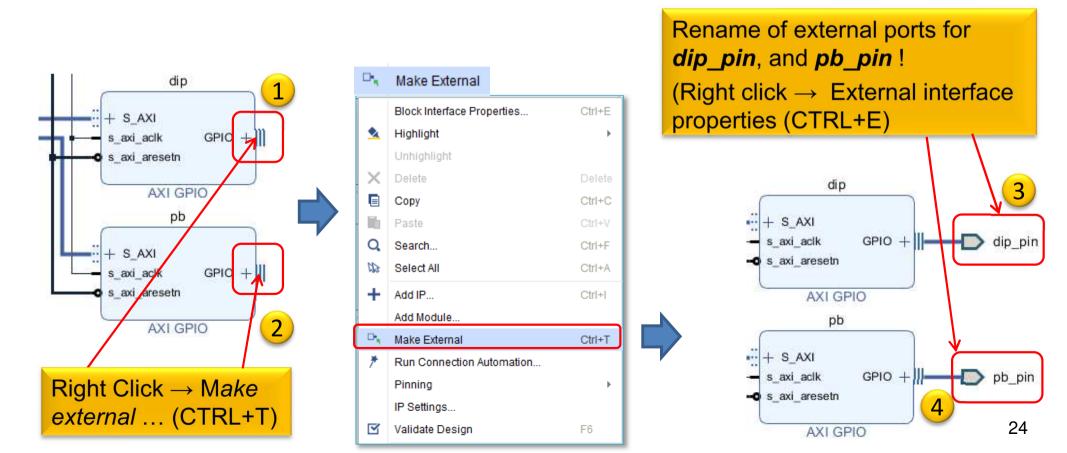

### Making external ports – AXI GPIO

The dip and pb GPIO instances must be connected to the physical FPGA pins of the (dip) switches and (pb) pushbuttons on the ZyBo platform:

- 1. The data ports of GPIO instances must also be connected to external FPGA pins,

- 2. We also define the names of the external ports (e.g. ending in \_pin),

- 3. In the <system> .XDC file the proper FPGA pin must be specified.

#### **Block Design – Layout synthesis**

- Update the Block Design:

- Regenerate Layout

- Validate Design (DRC)

- 区

- Flow Navigator → Run Synthesis

- Open Synthesized Design, OK

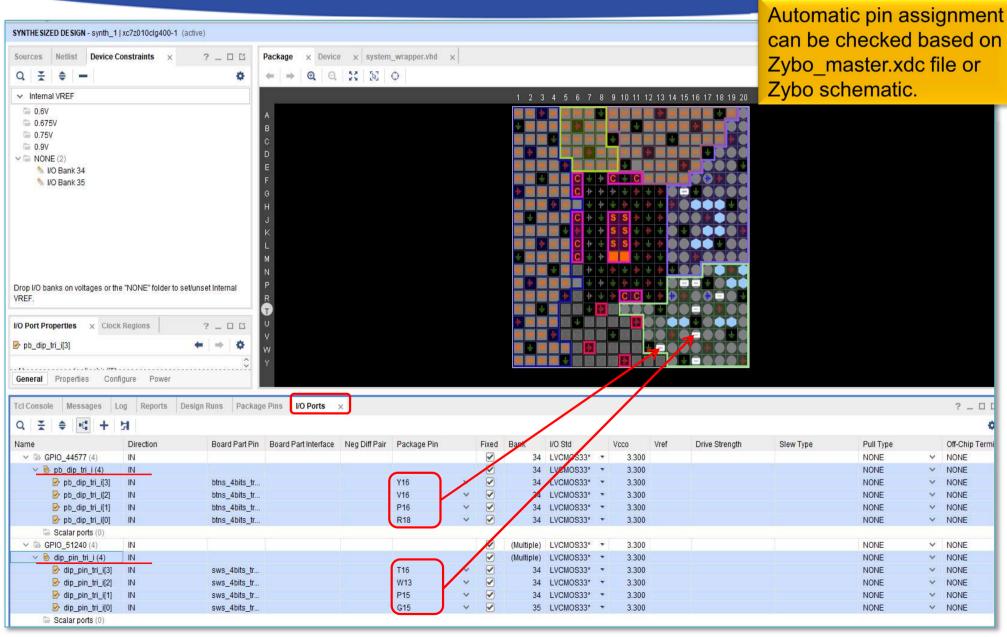

- At the final step, the FPGA I/O pins must also be assigned to the two external ports

assigned to the two external ports

(dip\_pin and pb\_pin, respectively)!

Layout menu → I/O Planning layout view

# Block Design – Full view

# I/O Planning – Pin assignment

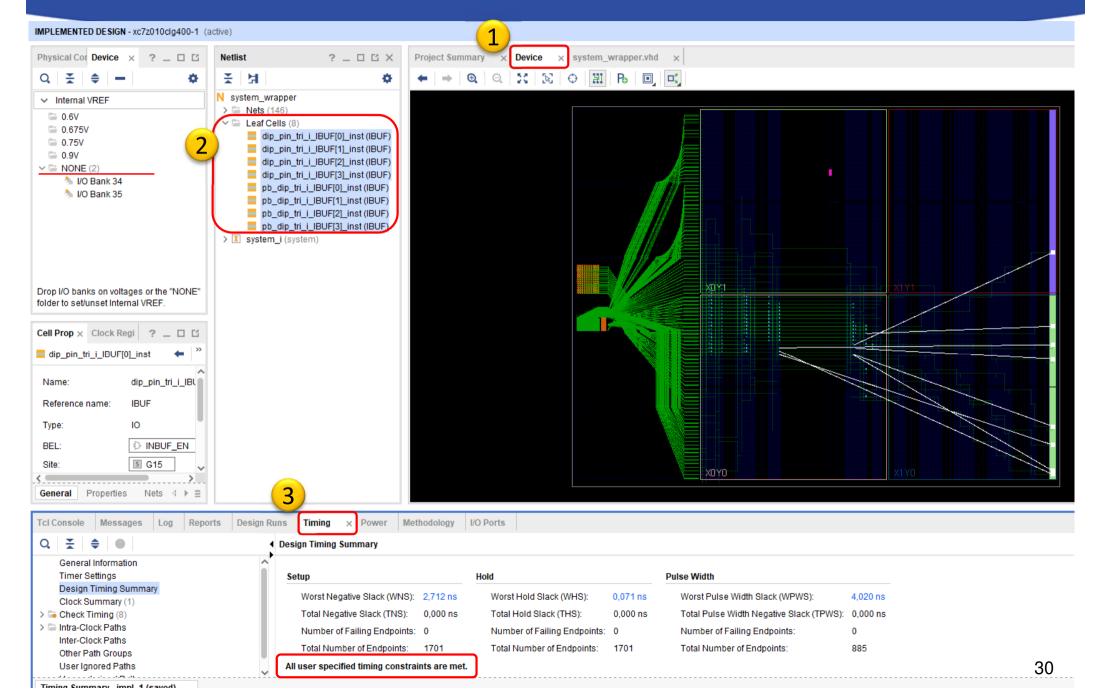

# Implementation and Bitstream generation

Flow Navigator menu → Run Implementation

- It can filters out possible wrong assignments / errors,

- Warning messages are allowed (the design can be implemented),

- Some floating wires are also allowed (e.g. Peripheral Reset, etc.).

- While Vivado is working you can check out the synthesis/implementation reports!

Finally, run the Bitstream generation:

Flow Navigator → Generate Bitstream

### Q & A 1.)

What is the physical package pin value of the push buttons (pb)?

```

- R18 = pb_pin_tri_i[0]

- P16 = pb_pin_tri_i[1]

- V16 = pb_pin_tri_i[2]

- Y16 = pb_pin_tri_i[3]

```

What is the physical package pin value of the dip switches (dip):

```

- G15 = dip_pin_tri_i[0]

- P15 = dip_pin_tri_i[1]

- W13 = dip_pin_tri_i[2]

- T16 = dip_pin_tri_i[3]

```

- What are their directions?

- All "IN" as INput direction

# Layout Editor – Floorplanning

#### XILINX VIVADO DESIGN SUITE

LAB02\_A. ANALYZING BLOCK DIAGRAM AND RIPORTS

BEFEKTETÉS A JÖVŐBE

## **Analyzing Block Diagram**

- Question 1.) (buses, internal signals)

- Which IP peripheral instance(s) are associated with the clock named processing\_system7\_0\_FCLK\_CLK0?

- What is its frequency?

- Which IP peripheral instance(s) are connected to the AXI Lite bus interface?

- Question 2.) (addresses)

- Outline a full memory space / map of the system by specifying instance names!

- Question 3.) (resource utilization)

- How many resources are utilized on the PL/FPGA side?

# **Analyzing Block Diagram (cont.)**

- Question 1.) Solution

- Which IP peripheral <u>instance(s)</u> are associated with the clock named processing\_system7\_0\_FCLK\_CLK0 ?

- processing\_system7 (feedback)

- rst\_processing\_system7

- dip

- pb

- ps7\_axi\_periph

- Clock processing\_system7\_0\_FCLK\_CLK0 is:

- 100 MHz! (Just check it: ZynqPS → Clock Configuration → PL Fabric Clock)

- Which IP peripheral instance(s) are connected to the AXI Lite bus interface?

- processing\_system7

- dip

- pb

# **Analyzing Block Diagram (cont.)**

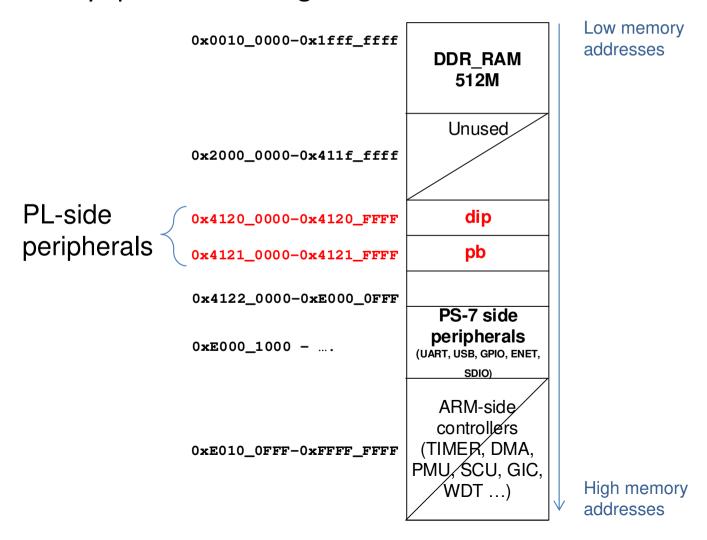

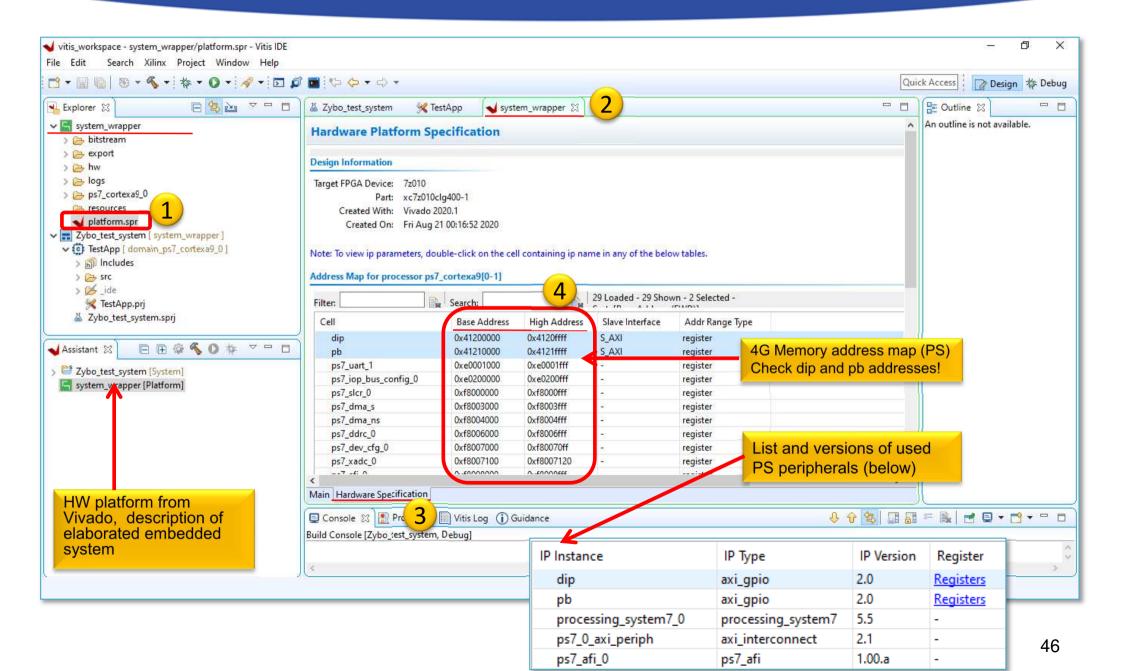

- Question 2.) Solution

- memory space: Block Diagram → Address Editor or VITIS .XSA

# **Analyzing Block Diagram (cont.)**

- Question 3.) Solution

- How many resources are utilized on the PL/FPGA side?

- Reports tab → Report Utilization (vagy Project Summary ∑)

| +                      | +    | <b></b> |           | <b></b> |

|------------------------|------|---------|-----------|---------|

| Site Type              | Used | Fixed   | Available | Util%   |

| +                      | +    | H       |           | +       |

| Slice LUTs             | 566  | 0       | 17600     | 3.22    |

| LUT as Logic           | 504  | 0       | 17600     | 2.86    |

| LUT as Memory          | 62   | 0       | 6000      | 1.03    |

| LUT as Distributed RAM | 0    | 0       |           |         |

| LUT as Shift Register  | 62   | 0       |           |         |

| Slice Registers        | 815  | 0       | 35200     | 2.32    |

| Register as Flip Flop  | 815  | 0       | 35200     | 2.32    |

| Register as Latch      | 0    | 0       | 35200     | 0.00    |

| F7 Muxes               | 0    | 0       | 8800      | 0.00    |

| F8 Muxes               | 0    | 0       | 4400      | 0.00    |

| ++                     |      |         |           |         |

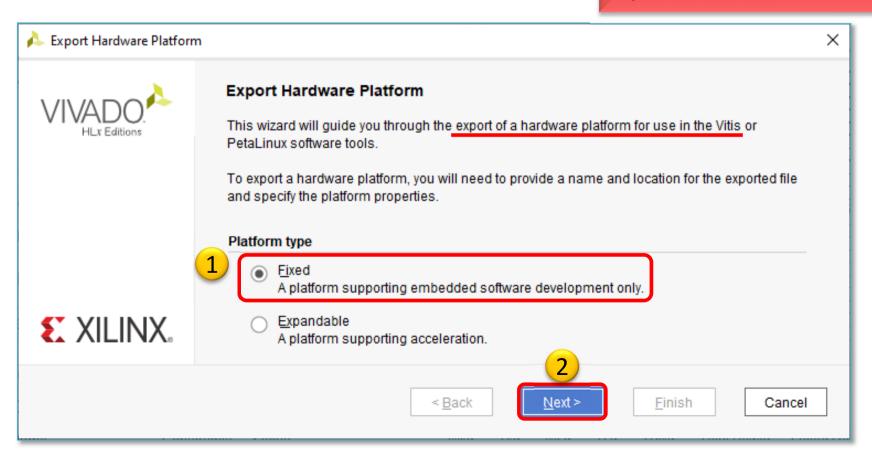

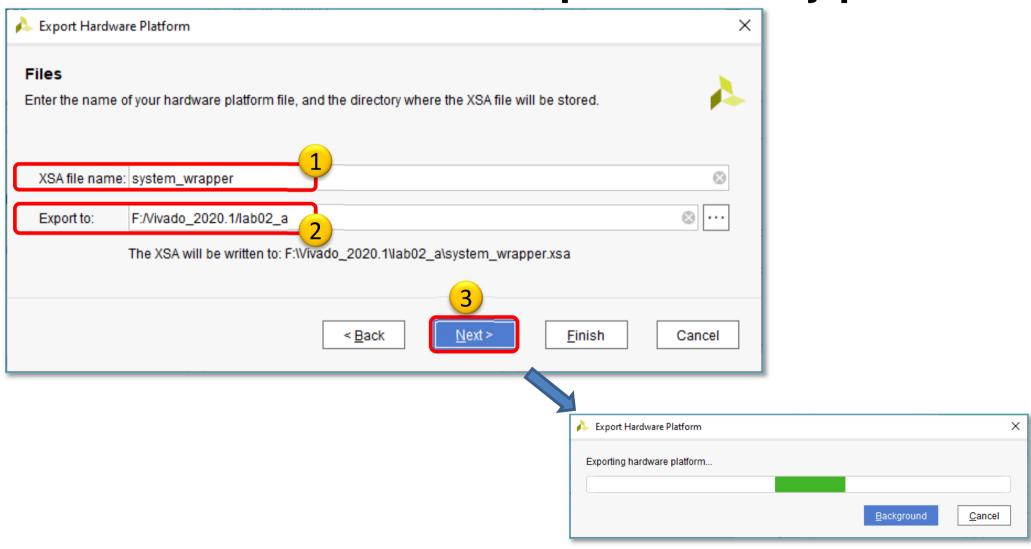

#### VIVADO Export HW → VITIS (~SDK)

• File  $\rightarrow$  Export  $\rightarrow$  Export Hardware...

2020.x: at least an Elaborated Design must be able to be exported to HW!

#### VIVADO Export HW -> VITIS (cont.)

#### Select "Include bitstream" option as output:

#### Export HW → VITIS (cont.)

Set XSA\* file name and export directory path:

#### **USING XILINX VITIS**

LAB02\_A. Creating a software test application

BEFEKTETÉS A JÖVŐBE

# VITIS – General steps of application development

- 1. Creating a Vivado project, then Export HW  $\rightarrow$  VITIS,  $\sqrt{\phantom{a}}$

- Creating a new application or an application generated from a C/C ++ template (e.g. *TestApp* peripheral test):

- a. Importing .XSA

- b. Generating and compiling an application project containing a platform and a domain inside (~BSP: Board Support Package),

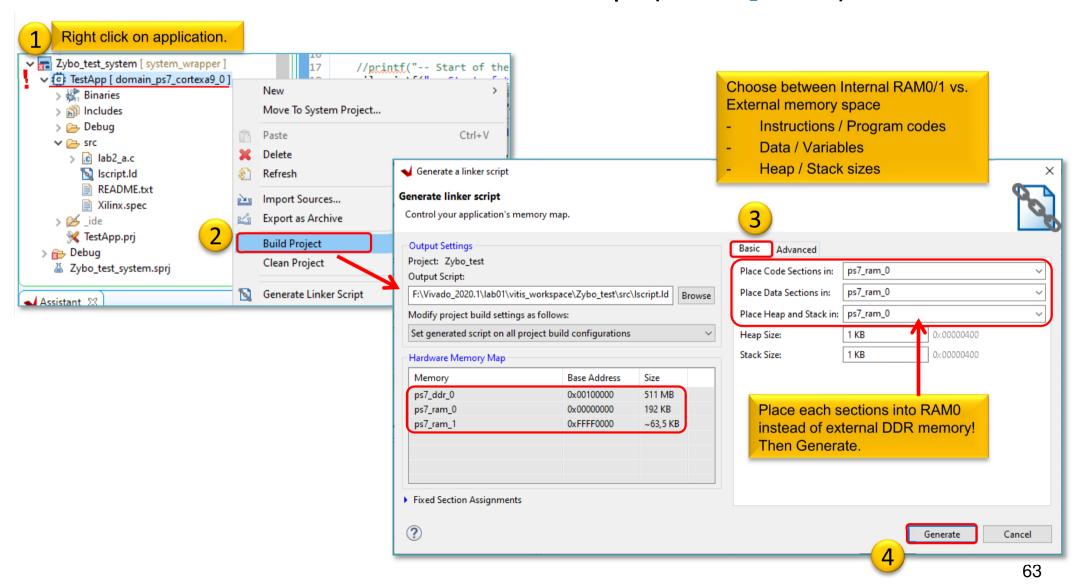

- c. Generating a Linker Script (specifying memory sections, .LD),

- d. Writing / generating and compiling the SW application

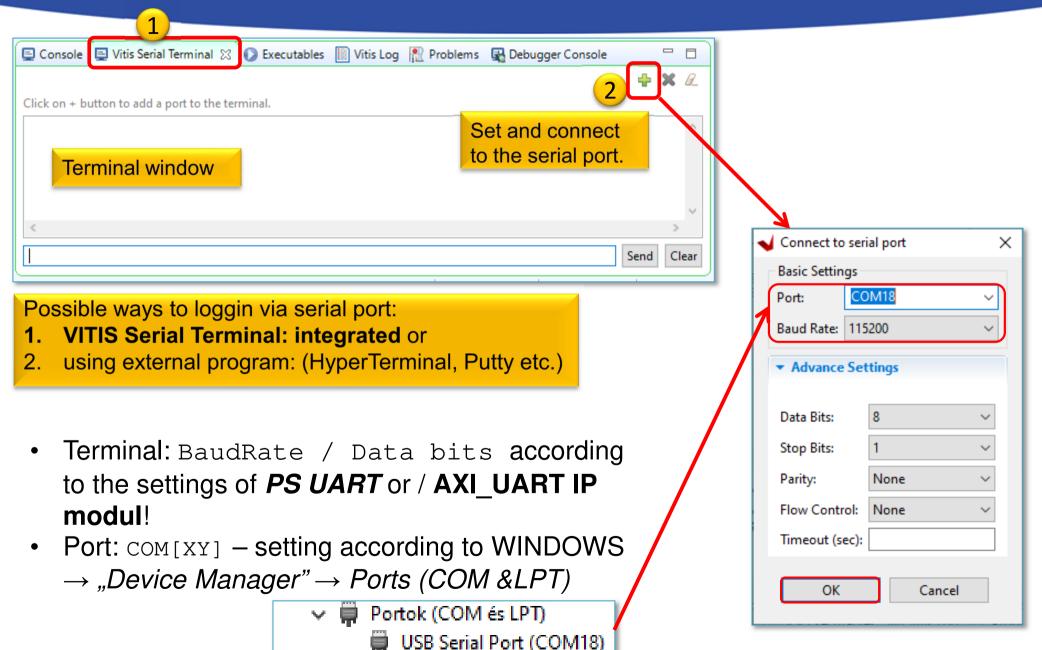

- 3. Setup a Serial terminal/Console (USB-serial port),

- 4. Connecting and setup a JTAG-USB programmer,

- Configuring the FPGA (.BIT if PL-side existing)

- 5. Creating a 'Debug Configuration' for hardware debugging

- 6. Debug (insert breakpoints, stepping, run, etc.)

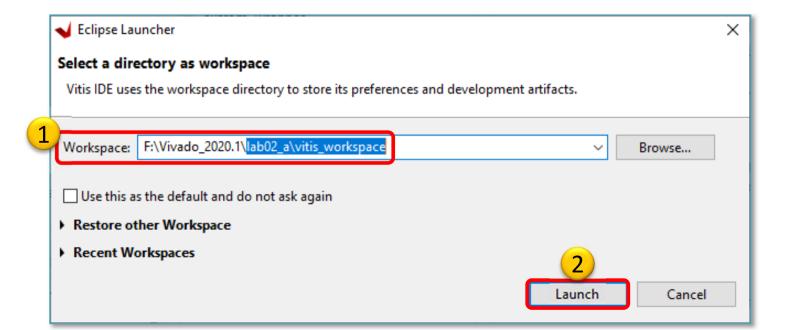

#### **Starting VITIS**

From Vivado: Tools menu → Launch VITIS IDE

OR externally

Start menu → Programs → Xilinx Design Tools → Xilinx VITIS 2020.1

Do Not run Xilinx VITIS HLS 2020.1!

- Set workspace directory properly (1ab02\_a):

- Recommended to use <u>vitis\_workspace</u> as a subdirectory in your lab folder. Then Launch...

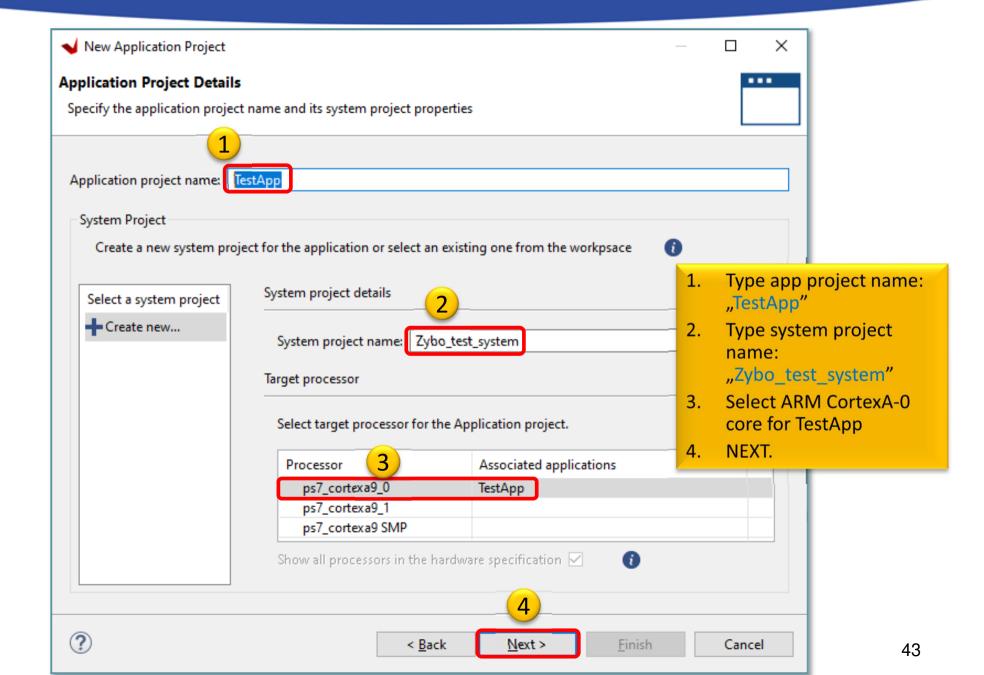

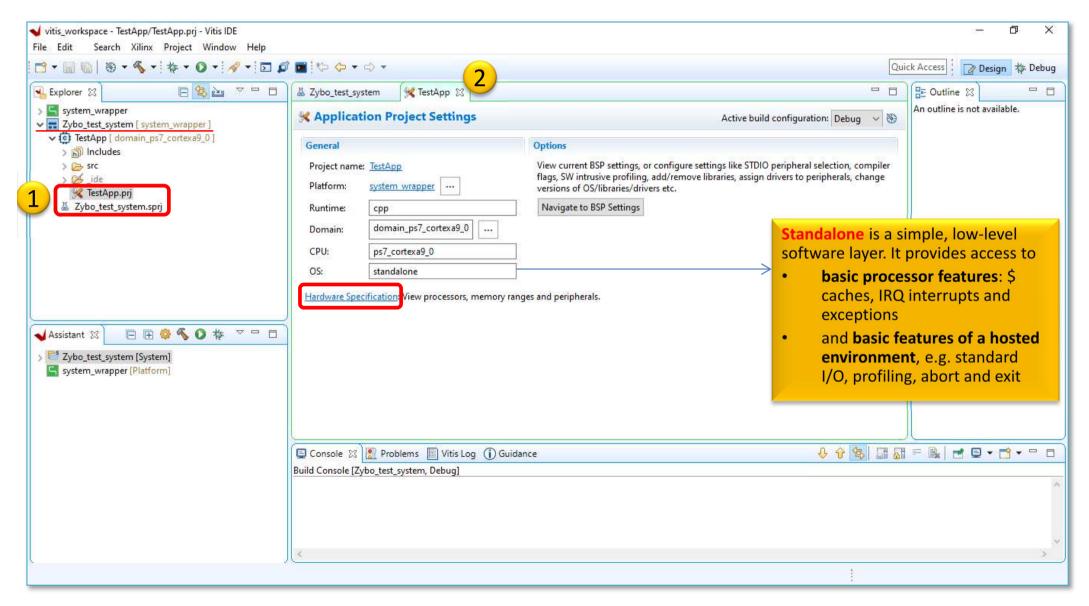

#### Xilinx VITIS – Create Application

#### Recall the steps of the former LAB01!

#### 1. Create a new application project

- File  $\rightarrow$  New  $\rightarrow$  Application Project...

#### 2. Platform – Create a new platform from HW (XSA)

- Browse... for LAB02 system\_wrapper.xsa. Open it.

- Do not select the "Generate boot components"

#### 3. Application project details

- Type "TestApp" as project name

- Type "Zybo\_test\_system" as system project name

- Select ps7\_cortexa9\_0 as target ARM core 0

#### 4. Domain: leave settings as default (standalone)

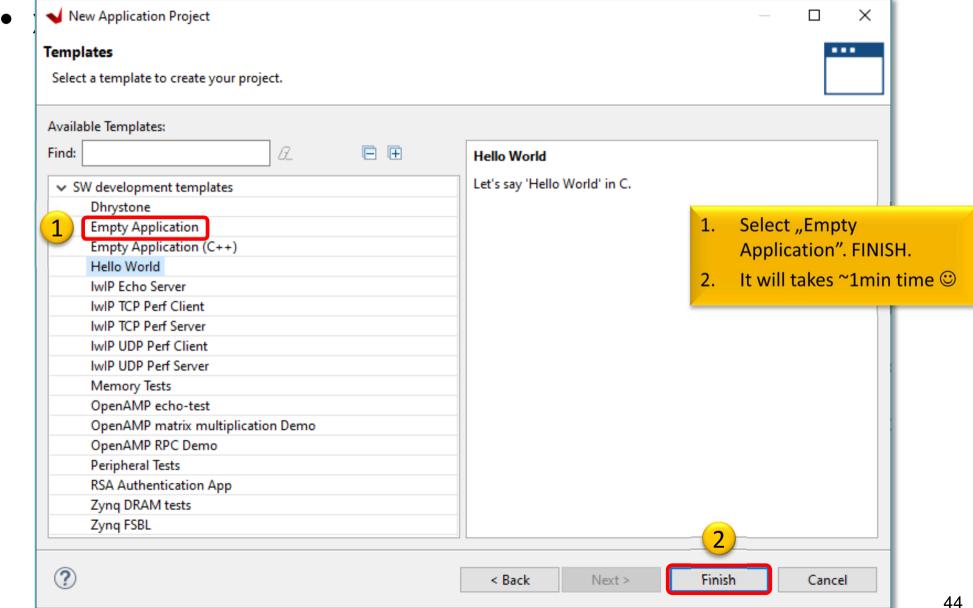

#### **Create Application (cont)**

# **Example I.) Creating TestApp** application

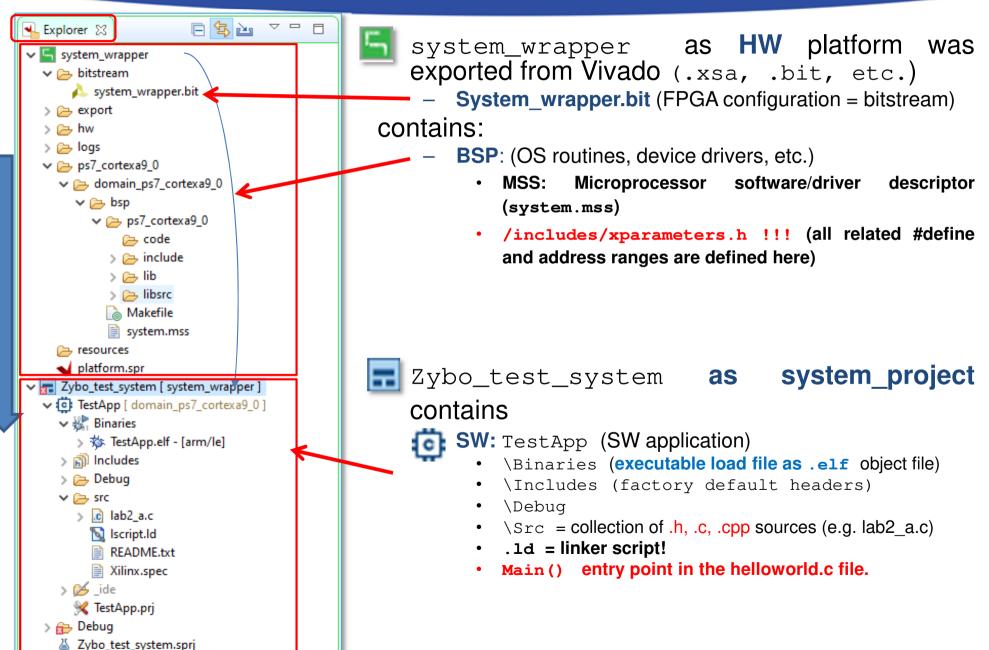

#### VITIS GUI – Main window

#### VITIS – HW platform

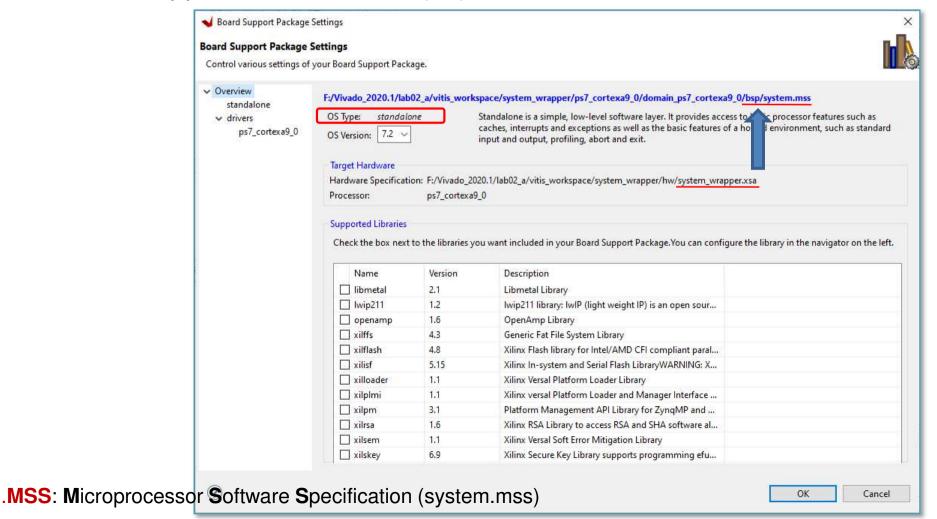

#### VITIS – BSP Board Support Package

#### Software Platform Settings

- Selected OS: standalone vs. freertos\_10 (or 3rd Party OS)

- Supported SW libraries (lib)

#### Q & A 1.)

What is the IP type and IP version of "dip" and "pb" instances?

```

axi_gpio,

```

- v2.0

- What is the driver name of them?

- gpio

- Calculate what size they are?

```

- dip: 0x4120 0000-0x4120 ffff = 64 KByte

```

- pb: 0x4121 0000-0x4121 ffff = 64 KByte

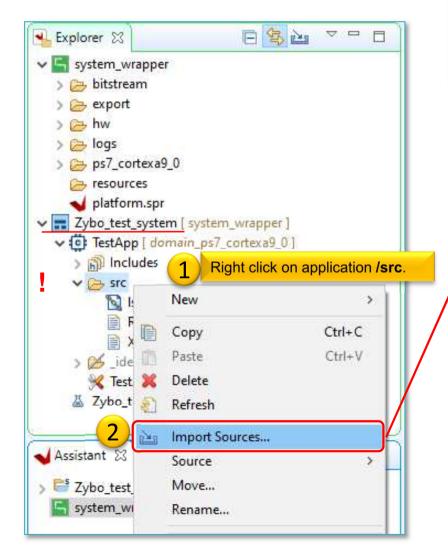

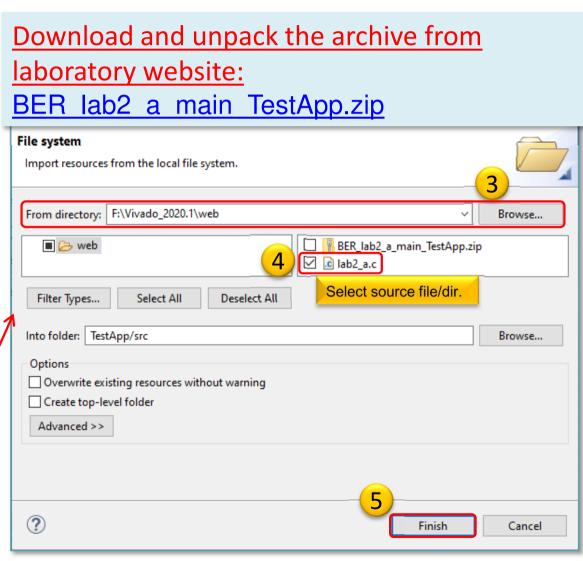

#### Add C/C++ source(s)

Add/Create new source (lab2\_a.c) to the application

project

49

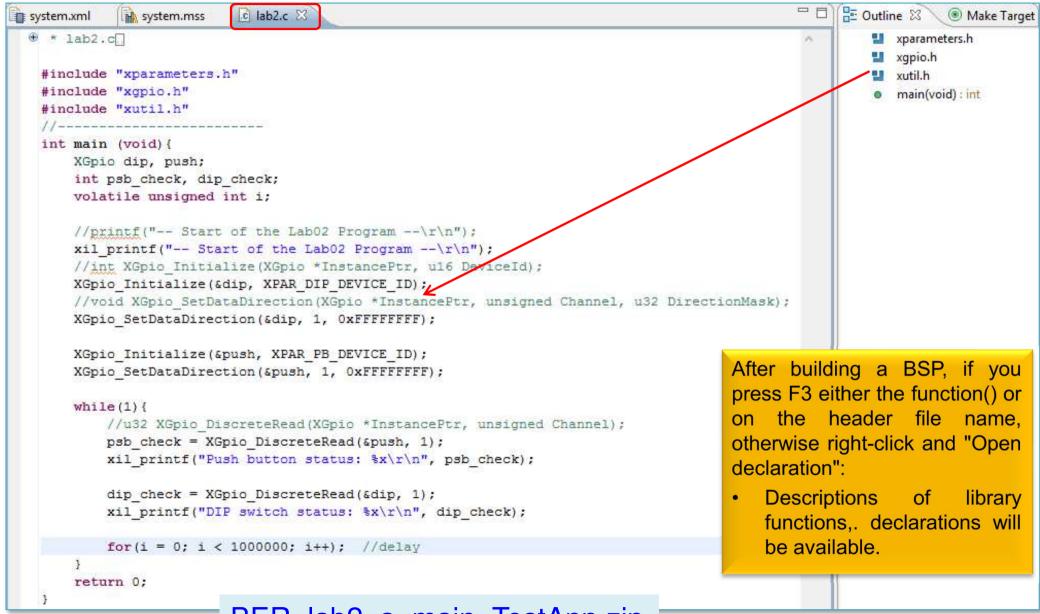

#### TestApp – source code

## VITIS – Project Explorer / Hierarchy

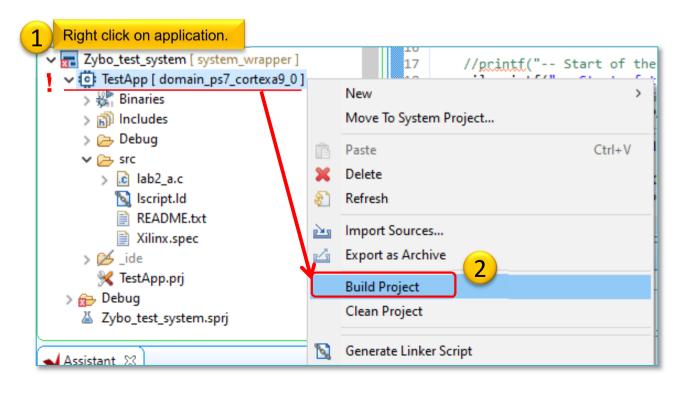

#### **Build project**

- 1. Select Application project (e.g. TestApp)

- 2. Project menu → Build Project... in two steps:

- Build BSP (system\_wrapper)

- Build software application (lab2\_a.c)

# Build project – Result (Console)

```

'Building target: TestApp.elf'

'Invoking: ARM v7 gcc linker'

arm-none-eabi-gcc -mcpu=cortex-a9 -mfpu=vfpv3 -mfloat-abi=hard -Wl,-

build-id=none -specs=Xilinx.spec -Wl,-T -Wl,../src/lscript.ld -

LF:/Vivado 2020.1/lab02 a/vitis workspace/system wrapper/export/syste

m_wrapper/sw/system_wrapper/domain_ps7_cortexa9_0/bsplib/lib -o

"TestApp.elf" ./src/lab2_a.o -Wl,--start-group,-lxil,-lgcc,-lc,--

end-group

'Finished building target: TestApp.elf'

'Invoking: ARM v7 Print Size'

arm-none-eabi-size TestApp.elf

tee "TestApp.elf.size"

data

dec

hex filename

text

bss

22840

1176 22584 46600

b608 TestApp.elf

'Finished building: TestApp.elf.size'

```

**Decimal size: 46600 byte** ~46 KByte. The entire program can be placed both the internal on-chip RAM 0/1 and the external DDR RAM. (On the PL / FPGA-side, however, this amount of BRAM memory should be reserved). Therefore, the executable .elf file was also generated successfully.

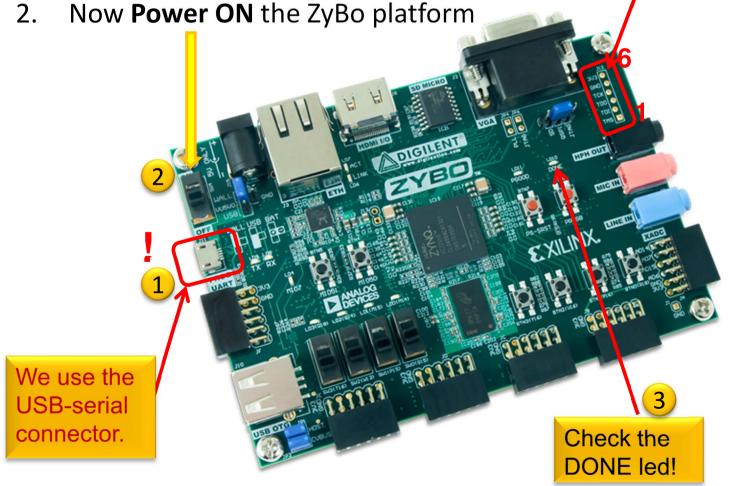

# Embedded system and software test verification

**Connect** the USB-serial cable (power+programmer functionality). Please

check:

JP7 jumper = USB power!

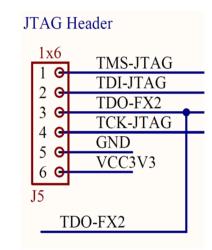

JTAG programming port (optional, but we don't use it!) JP5 jumper = JTAG mode!

ZyBo - Xilinx USB programming cable VCC3V3 - red VREF (6) GND - black GND (5) TDO-FX2 - lilac - TDO (3) TDI-JTAG – white TDI (2) TMS-JTAG - green TMS (1)

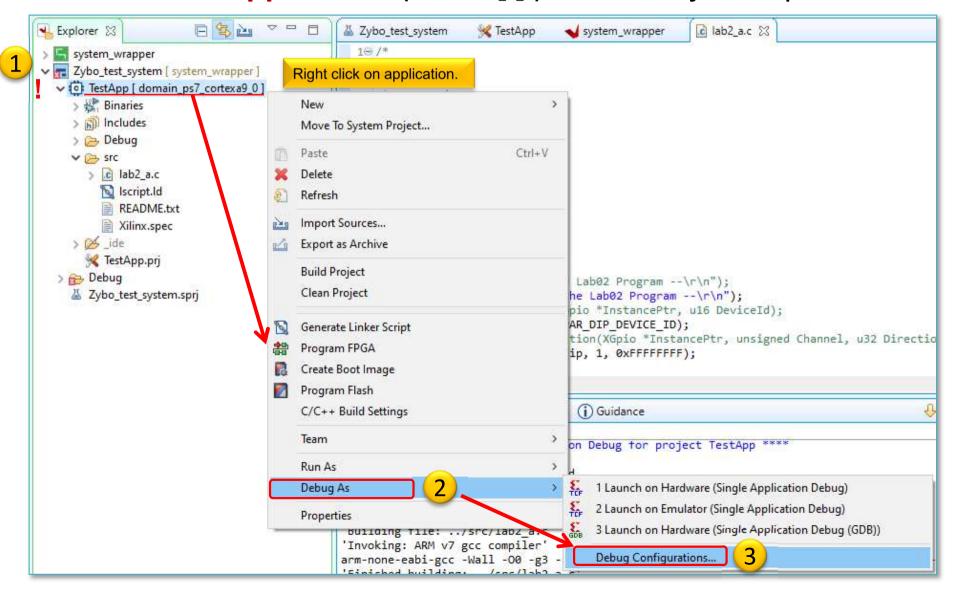

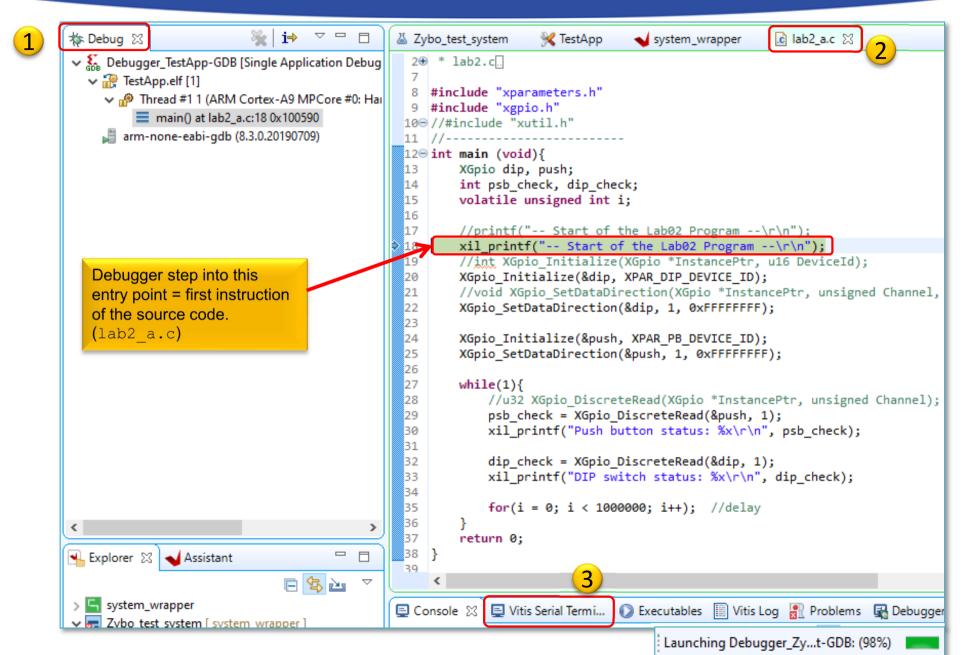

#### **Creating Debug Configuration**

Select the application (TestApp) in the Project Explorer

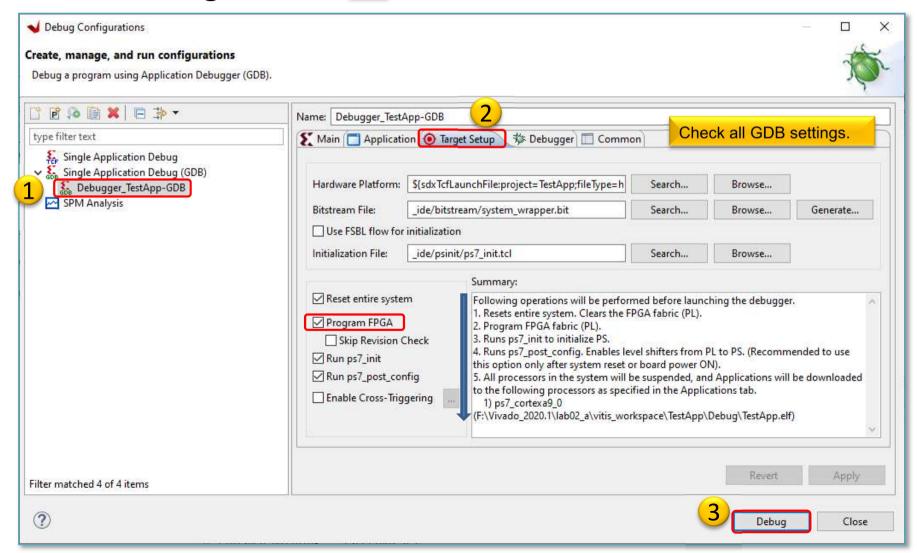

#### Create a new GDB configuration

Select "Single Application Debug (GDB)" option

New configuration

#### **Lunching Debugger**

# Set Debug-serial port (VITIS terminal)

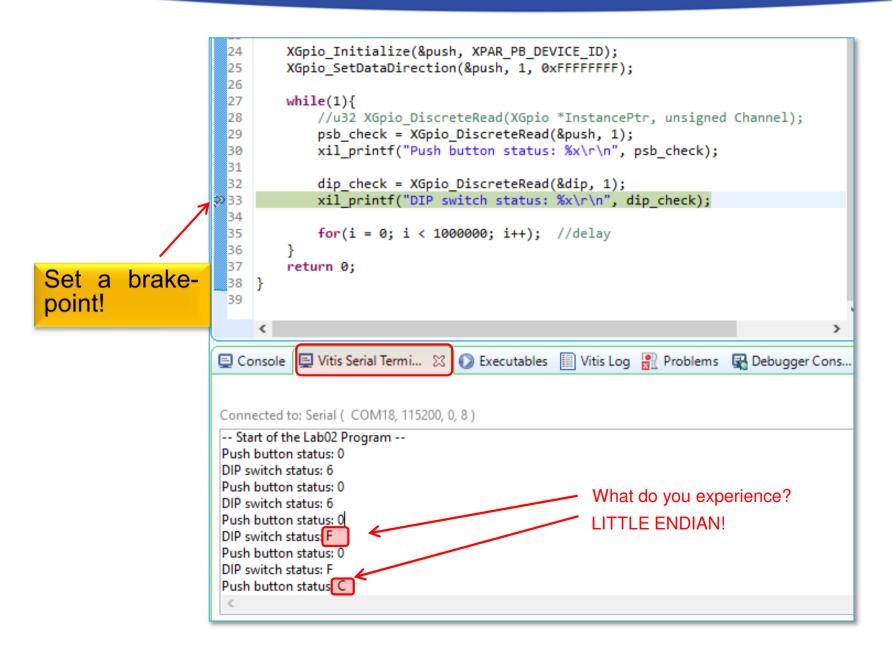

#### TestApp – Verification result

#### TestApp – Verification result

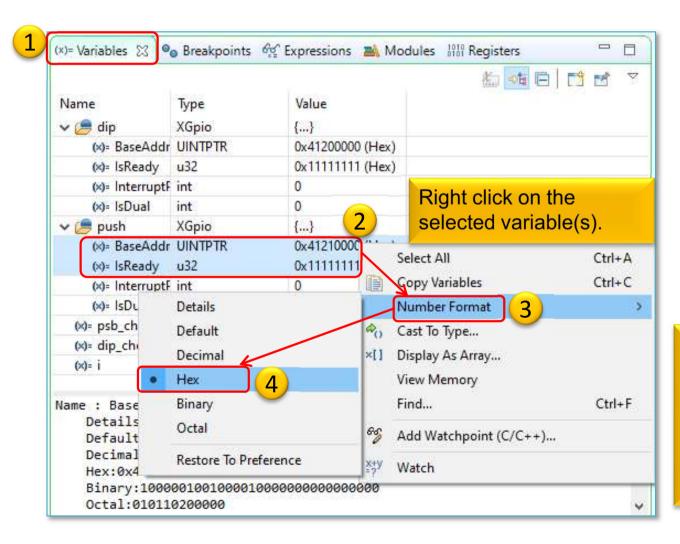

During active debug process set in the Variables window both the BaseAddress / IsReady parameters of the pb / push variables to Hexadecimal format.

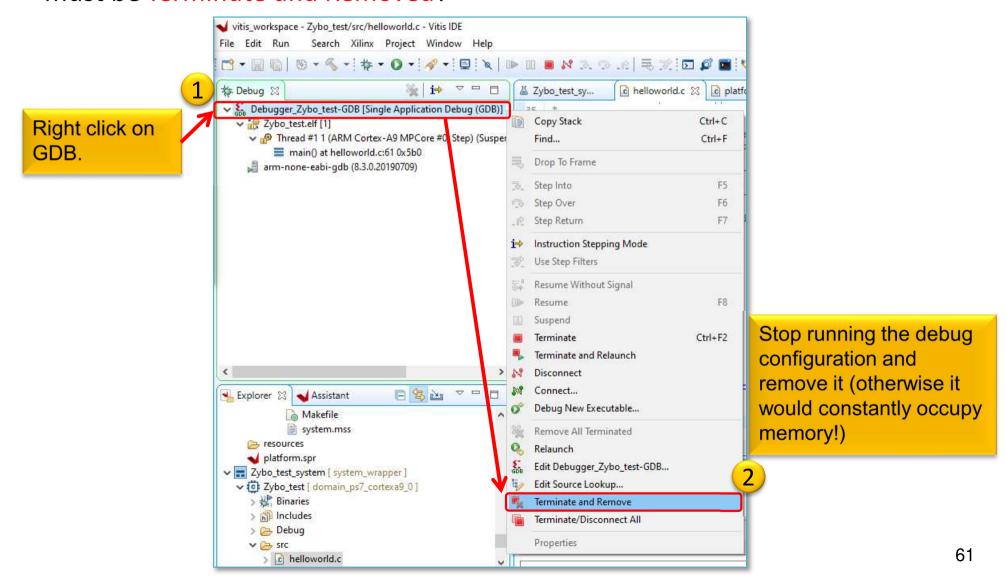

#### **Terminate Debug process**

• IMPORTANT! At the end of the HW debug, the running debug configuration must be *Terminate and Removed*!

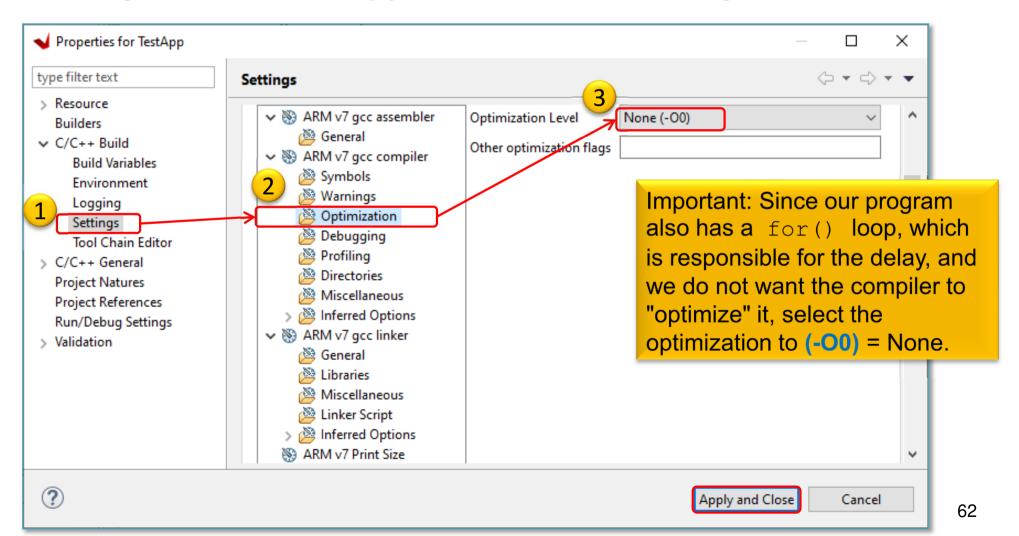

#### Compiler settings

- Check compiler settings:

- Right click on TestApp → C/C++ Build Settings

#### Linker Script generation (Basic)

• Xilinx menu → Generate Linker Script (lscript.ld) → RAMO

# **Example II.) Peripheral Test**

- 1. File  $\rightarrow$  New  $\rightarrow$  Application Project ...

- 2. Select system\_wrapper.xsa as platform

- 3. Add "Peripheral\_test" as application project name

- + Create a new system project (leave Peripheral Test\_system by default)

- Select ps7\_cortexa9\_0 ARM core-0

- 4. Leave domain settings as default

- 5. Templates: select "Peripheral Test". FINISH.

## **Example II.) Build and Debug**

- 1. Build the built-in *Peripheral Test* application (.elf)

- 2. Lunch the proper Debug configuration (GDB) for hardware debugging

- 3. Setup the VITIS serial terminal/Console (USB-serial port),

- 4. Connecting and setup a JTAG-USB programmer,

- Configuring the FPGA (.BIT if PL-side existing)

- 5. Debug procedure (insert breakpoints, stepping, run, etc.)

- Watching variables and examine memory monitor!

- 6. At the end of debug procedure do not forget to Terminate and Remove the actual Debug configuration (GDB)!

- 7. That's all:D

#### **Example II.) Questions & Answers**

- What is the size of the Peripheral\_test application?

- − ~82 Kbyte

```

'Invoking: ARM v7 Print Size'

arm-none-eabi-size Peripheral_test.elf | tee

"Peripheral_test.elf.size"

text data bss dec hexfilename

46796 1992 33440 82228

14134Peripheral_test.elf

'Finished building: Peripheral_test.elf.size'

```

- Generate the linker script to RAM1 (ps7\_ram1) address space! What do you experience?

- Linking ERROR. Why?

#### HW debugging steps – Peripheral\_test

- 1. Create a new Debug Configuration (GDB) for Peripheral\_test

- Lunch Debugger

- Set-up Debug-serial port (VITIS terminal)

- 4. HW debug Peripheral\_test

- 5. Examine results serial logs

- 6. Terminate and remove debug process!

```

Connected to COM18 at 115200

---Entering main---

Running ScuGicSelfTestExample() for ps7_scugic_0...

ScuGicSelfTestExample PASSED

ScuGic Interrupt Setup PASSED

Running GpioInputExample() for dip...

GpioInputExample PASSED. Read data:0xD

Running GpioInputExample() for pb...

GpioInputExample PASSED. Read data:0x4

Running DcfgSelfTestExample() for ps7_dev_cfg_0...

DcfgSelfTestExample PASSED

......

---Exiting main---

```

#### LAB02 – Summary

- To the ARM-AXI base system created in the previous (4. LAB01), we added two PL-side **AXI GPIO** peripherals from the **Vivado** IP catalog.

- Peripherals were properly configured and connected to the external I/O pins of the FPGA.

- We examined both the Block Diagram and the report files.

- The DIP switches (4) and PB pushbuttons (4) on the ZyBo card have been assigned to the pin assignments.

- Finally, we verified the completed embedded system (HW+FW) and the correct operation of the SW application (TestApp, and Peripheral Test) in VITIS unified environment.

EFOP-3.4.3-16-2016-00009

A felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása a Pannon Egyetemen

# THANK YOU FOR YOUR KIND ATTENTION!

BEFEKTETÉS A JÖVŐBE