EFOP-3.4.3-16-2016-00009

A felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása a Pannon Egyetemen

# EMBEDDED SYSTEM DEVELOPMENT

(MISAM154R)

Created by Zsolt Voroshazi, PhD

voroshazi.zsolt@virt.uni-pannon.hu

Magyarország Kormánya

BEFEKTETÉS A JÖVŐBE

#### 6. VIVADO – EMBEDDED SYSTEM

Adding peripherals to BSB from IP Catalog #2 (PMOD, GPIO)

BEFEKTETÉS A JÖVŐBE

## **Topics covered**

- 1. Introduction Embedded Systems

- 2. FPGAs, Digilent ZyBo development platform

- 3. Embedded System Firmware development environment (Xilinx Vivado "EDK" Embedded Development)

- 4. Embedded System Software development environment (Xilinx VITIS "SDK")

- 5. Embedded Base System Build (and Board Bring-Up)

- 6. Adding Peripherals (from IP database) to BSB

- 7. Adding Custom (I2C IP and XADC) Peripherals to BSB

- 8. Development, testing and debugging of software applications Xilinx VITIS (SDK)

- 9. Design and Development of Complex IP cores and applications (e.g. camera/video/audio controllers)

#### **Important notes & Tips**

- Make sure that the path of the Vivado/VITIS project to be created does NOT contain accented letters or "White-space" characters!

- Have permissions on the drive you are working on:

- If possible, DO NOT work on a network / USB drive!

- The name of the project and source files should NOT start with a number, but they can contain a number! (due to VHDL)

- Use case-sensitive letters consistently in source file and project!

- If possible, the name of the project directory, project and source file(s) should be different and refer to their function for easier identification of error messages.

#### XILINX VIVADO DESIGN SUITE

Adding IP cores to the Embedded Base System

BEFEKTETÉS A JÖVŐBE

#### Task

- Vivado Block Designer

- Add IP (Intellectual Property) cores to the formerly elaborated block design (Embedded Base System) from the IP Catalog,

- Parameterize IP blocks, set connections, interfaces, address, and external ports (modify .XDC if needed),

- VITIS SDK

- Customize compiler settings,

- Creating a software application (from pre-defined template)

#### Main steps to solve the task

- Create a new project based on previous laboratory (slide 05.)

by using the Xilinx Vivado (IPI) embedded system designer,

- LAB02\_A project → Save as... → LAB02\_B

- Select and add GPIO (LED) peripherals to the base system

- Parameterize and connect them, make external ports

- Overview of the created project,

- Implementation and Bitstream generation (.BIT) is now necessary, because PL side will also be configured!

- Create peripheral "TestApp" software application(s) running on ARM by using the Xilinx VITIS environment (~SDK),

- Verify the operation of the completed embedded system and software application test on Digilent ZyBo.

#### XILINX VIVADO DESIGN SUITE

LAB02\_A. LED controller (GPIOs)

BEFEKTETÉS A JÖVŐBE

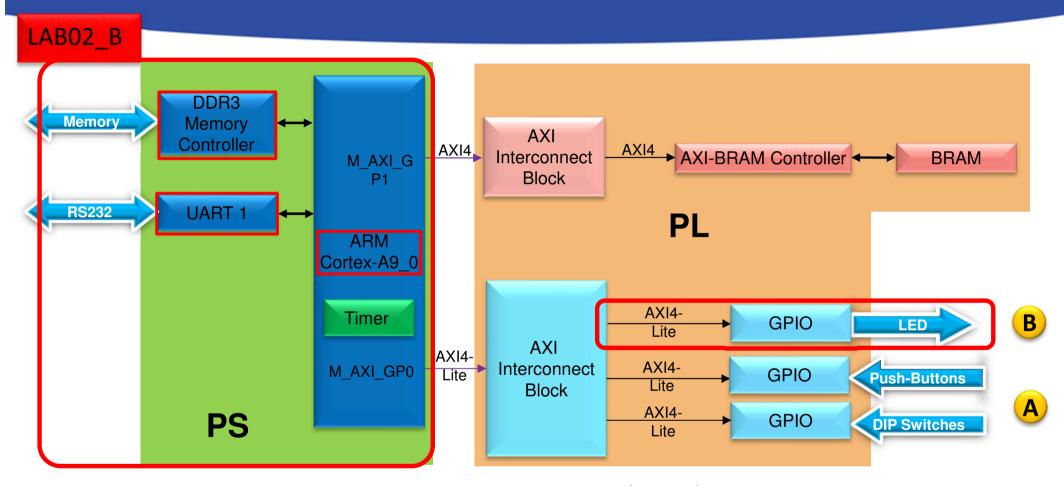

#### Test system to be implemented

#### PS side:

- ARM hard-processor (Core0)

- Internal OnChip-RAM controller

- UART1 (serial) interface

- External DDR3 memory controller

#### PL (FPGA)

- (A) LAB02\_A: GPIO inputs

- PBSs: Push Button

- DIPs: Switches

- (B) LAB02\_B: GPIO outputs

- LED controller

#### Project – Open / Save as...

- Start Vivado

- Start menu → Programs → Xilinx Design Tools → Vivado

2020.1

- Open the previous project! (LAB02\_A)

- File → Project → Open... / Open Recent...

- - open

Open

- File → Project → Save As... → LAB02\_B

- (This will save the former project LAB02\_A as LAB02\_B)

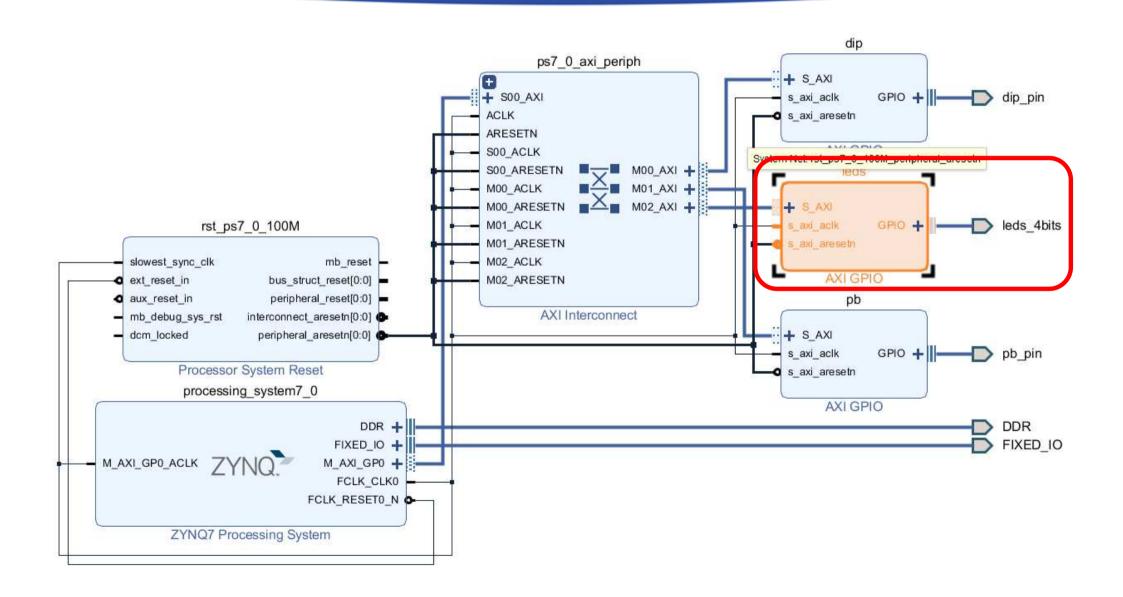

#### Task 1.) Adding LED controller

#### Vivado:

- LED controller: integrate and connect AXI\_GPIO peripherals selected from the Vivado IP catalog to the base system (4 pieces of LEDs),

- GPIO IP instance should be named as "leds".

- GPIO Board interface: select "leds\_4bits".

- Base Address: 0x4123\_0000 (size: 64 K)

- Assign external GPIO LED port to FPGA pins (led\_pin),

- Examine Block Design and Generate Bitstream

#### VITIS (~SDK):

- Create a Peripheral test application (PeriphTest) in the VITIS

SDK environment (based on the former app lab02.c!),

- Test verification of FW-SW plans on the ZyBo platform.

## Vivado – Completed design

## Task 2.) LED counter(s)

- Modify the Peripheral Test SW application (lab02\_a.c) in order to flash the LEDs by increasing the value of a 4-bit counter.

- Apply the PeripheralTest template (see GpioOutputExample () function)

#### Help:

- Use the built-in data types (e.g. u8)

- Since sys\_clk = 100 MHz, delay the LEDs up / down (by using a

for() cycle) so that the flash time can be percebtible: ~1 sec.

- Using macros from the xparameters.h file if a possible build error(s) occurs

- set LED\_DELAY, GPIO\_BITWIDTH!

- BER\_lab2b\_led8bit\_count.zip

## Task 3.) LED strings

- Modify the application of the Peripheral Test SW in the former Task 2.) so that the value of the LEDs is always shifted by one position to the left (as an ascending binary weight counter)

- Help: BER lab2b led8bit shift.zip

## Task 4.) "Knight Rider" LED strings

- Modify the application of the Peripheral Test SW in the former Task e 3.) so that the value of the LEDs is always shifted by one position to the left and then when it reaches the end it moves backwards to the right (using an increasing and then decreasing binary weight counter).

- Help: BER\_lab2b\_led8bit\_knightrider.zip

#### XILINX VIVADO DESIGN SUITE

LAB2\_C. PMOD\_TMP temperature measurement (AXI\_I2C controller / PS\_I2C controller).

BEFEKTETÉS A JÖVŐBE

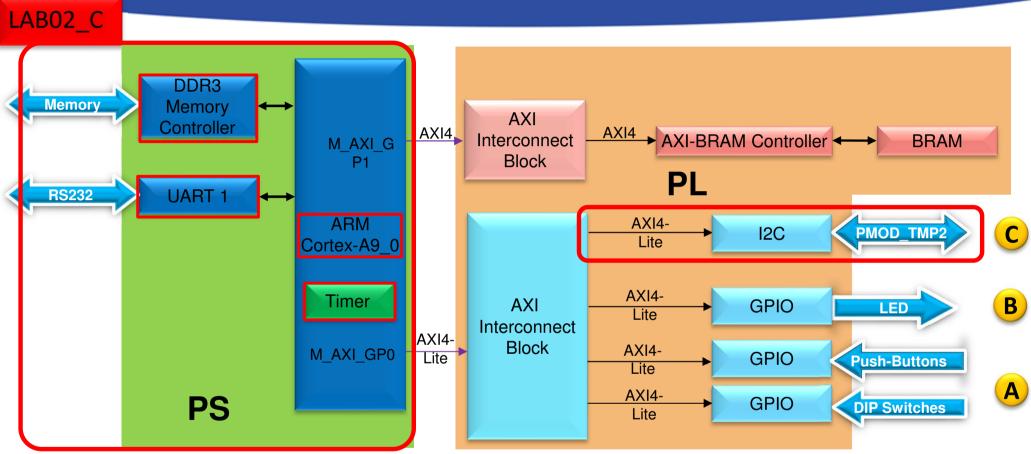

#### Test system to be implemented

#### PS side:

- ARM hard-processor (Core0)

- Internal OnChip-RAM controller

- UART1 (serial) interface

- External DDR3 memory controller

#### PL (FPGA)

- (A) LAB02\_A: GPIO inputs

- PBSs: Push Button (nyomógomb kezelő)

- DIPs: Switches (kapcsoló kezelő)

- (B) LAB02\_B: GPIO outputs

- LED controller

- (C) LAB03\_C: I2C component

#### Main steps to solve the task

- Create a new project based on previous laboratory (slide 05.) by using the Xilinx Vivado (IPI) embedded system designer,

- LAB02\_A project → Save as... → LAB02\_C

- Select and add AXI\_I2C (or PS\_I2C) peripheral controller to the base system

- Parameterize and connect them, make external ports

- Overview of the created project,

- Implementation and Bitstream generation (.BIT) is now necessary, because PL side will also be configured!

- Create peripheral "TestApp" software application(s) running on ARM by using the Xilinx VITIS environment (~SDK),

- Verify the operation of the completed embedded system and software application test on Digilent ZyBo.

#### References

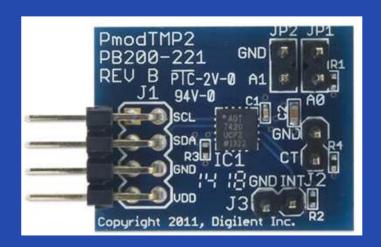

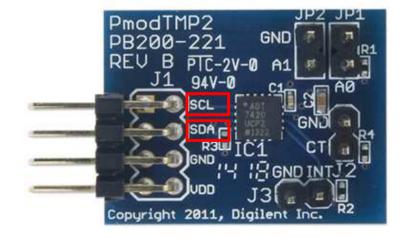

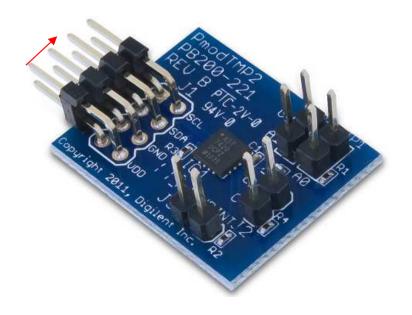

- Digilent PMOD TMP2 temperature sensor modul (I<sup>2</sup>C):

- https://store.digilentinc.com/pmod-tmp2-temperature-sensor/

- https://reference.digilentinc.com/reference/pmod/pmodtmp2/reference-manual

- Analog Devices ADT7420 sensor IC:

- http://www.analog.com/media/en/technical-documentation/data-sheets/ADT7420.pdf

- Analog Devices Digilent Wiki page:

- http://wiki.analog.com/resources/alliances/digilent

Reference design for FPGA (inc. SW drivers)

- http://wiki.analog.com/resources/fpga/xilinx/pmod/adt7420

- I<sup>2</sup>C standard:

- Dr. Fodor Attila, Dr. Vörösházi Zsolt: Beágyazott rendszerek, TÁMOP 4.1.2 (PE MIK, Villamosmérnöki és Információs Rendszerek Tanszék) 2011. in hungarian <a href="http://tananyagfejlesztes.mik.uni-pannon.hu/">http://tananyagfejlesztes.mik.uni-pannon.hu/</a>

- 12C Wikipedia: <a href="https://en.wikipedia.org/wiki/l%C2%B2C">https://en.wikipedia.org/wiki/l%C2%B2C</a>

#### **Digilent PMOD\_TMP2**

- I<sup>2</sup>C alapú based temperature sensor and temperature controller peripheral module

- $-T_{\Delta} = -40^{\circ}C \dots +150^{\circ}C$

- max. scalable to 16-bit resolution,

- An average accuracy better than 0.25 °C,

- 13 = 9+4 bit mode:  $1/2^4 = 0.0625$  °C,

- 16 = 9+7 bit mode:  $1/2^7 = 0.0078$  °C,

- $I^2C$  interface, 4 selectable (jumper) with  $I^2C$  address ( $A_1$ - $A_0$ )

- "Daisy Chain" option (7/10 bit addressing)

- Continuous conversion in every 240ms,

- Programmable treshold (max/min CT), external pins as threshold (INT),

- 3.3V or 5V interface support,

- No calibration required!

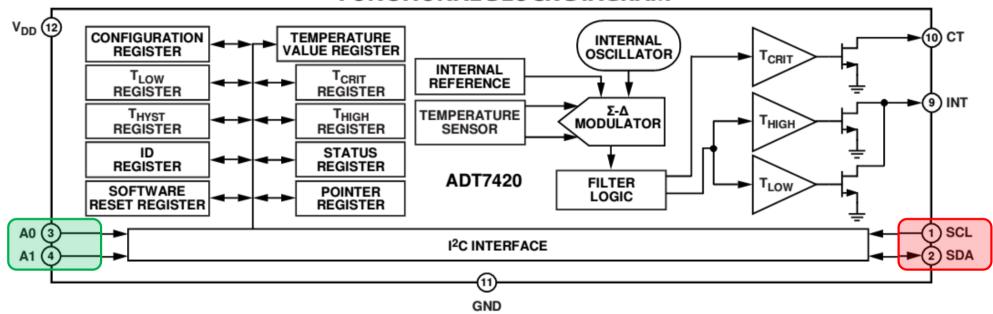

#### **ADT 7420**

• Block diagram:

#### **FUNCTIONAL BLOCK DIAGRAM**

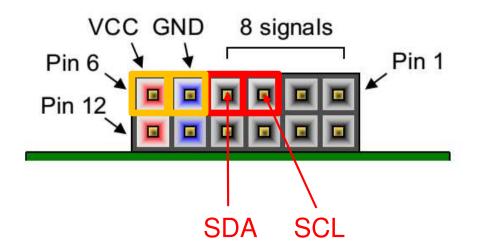

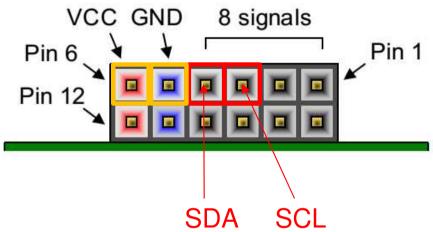

• PMOD\_TMP2 signals / I<sup>2</sup>C addresses:

| Connector J1 – I2C Communications |        |                        |  |  |

|-----------------------------------|--------|------------------------|--|--|

| Pin                               | Signal | Description            |  |  |

| 1,2                               | SCL    | I2C Clock              |  |  |

| 3,4                               | SDA    | I2C Data               |  |  |

| 5, 6                              | GND    | Power Supply Ground    |  |  |

| 7, 8                              | VCC    | Power Supply (3.3V/5V) |  |  |

|             | Addresses |         |                                |  |  |  |

|-------------|-----------|---------|--------------------------------|--|--|--|

|             | JP2       | JP1     | Address                        |  |  |  |

| <b>&gt;</b> | Open      | Open    | 0x4B (0b1001011)               |  |  |  |

|             | Open      | Shorted | 0x4A (0b1001010)               |  |  |  |

|             | Shorted   | Open    | 0x49 (0b10010 <mark>01)</mark> |  |  |  |

|             | Shorted   | Shorted | 0x48 (0b1001000)               |  |  |  |

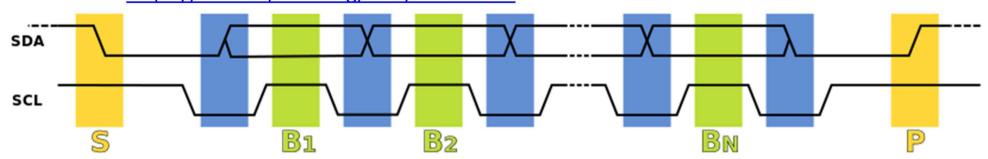

#### Philips I<sup>2</sup>C standard (1982)

Web: https://en.wikipedia.org/wiki/I%C2%B2C

- 1. Data Transfer is initiated with a *START bit* (S) signaled by **SDA** being pulled **low** while SCL stays high (pull-down).

- 2. SDA sets the 1st data bit level while keeping **SCL low** (during **blue** bar time).

- 3. The data is sampled (received) when **SCL** rises (green) for the first bit (B1).

- 4. This process repeats, SDA transitioning until **SCL** is low again, and the data being read while **SCL** is high (B2, Bn).

- 5. A STOP bit (P) is signaled when SDA is pulled high while **SCL** is **high**.

| Reserved Address | 8 Bit Byte    |            |           |                                   |

|------------------|---------------|------------|-----------|-----------------------------------|

| Index            | 7 bit Address |            | R/W Value | Description                       |

|                  | MSB (4bit)    | LSB (3bit) | 1 bit     |                                   |

| 1                | 0000          | 000        | 0         | General Call                      |

| 2                | 0000          | 000        | 1         | START BYTE                        |

| 3                | 0000          | 001        | X         | CBUS Address                      |

| 4                | 0000          | 010        | X         | Reserved For Different Bus Format |

| 5                | 0000          | 011        | X         | Reserved For Future Purpose       |

| 6                | 0000          | 0XX        | X         | HS-mode Master Code               |

| 7                | 1111          | 1XX        | 1         | Device ID                         |

| 8                | 1111          | 0XX        | Х         | 10-bit slave addressing           |

"Master write(0) to / read(1) from the Slave"

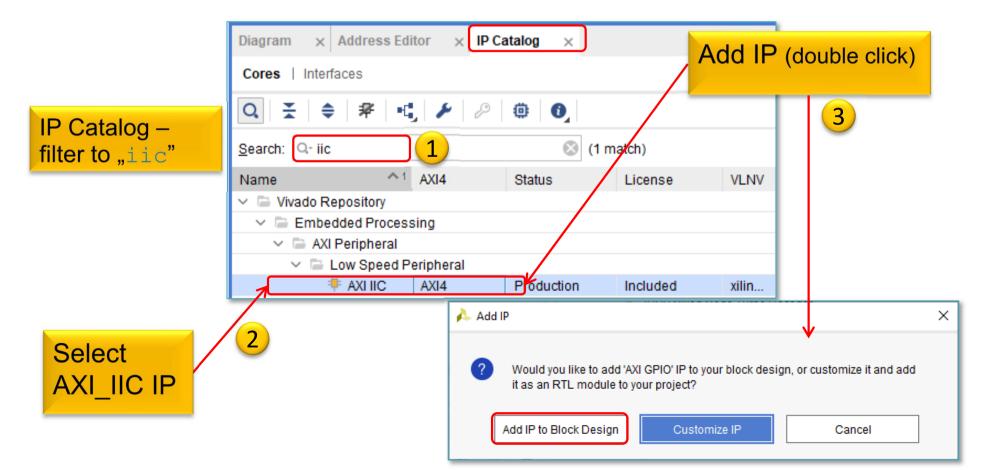

#### Adding I<sup>2</sup>C controller to the Base System I.

- Add I<sup>2</sup>C controller two possible ways by

- a.) adding PL-side AXI\_I2C IP core, OR

- b.) enabling PS-side (PS\_I2CO/1) IIC controller in Zynq PS7

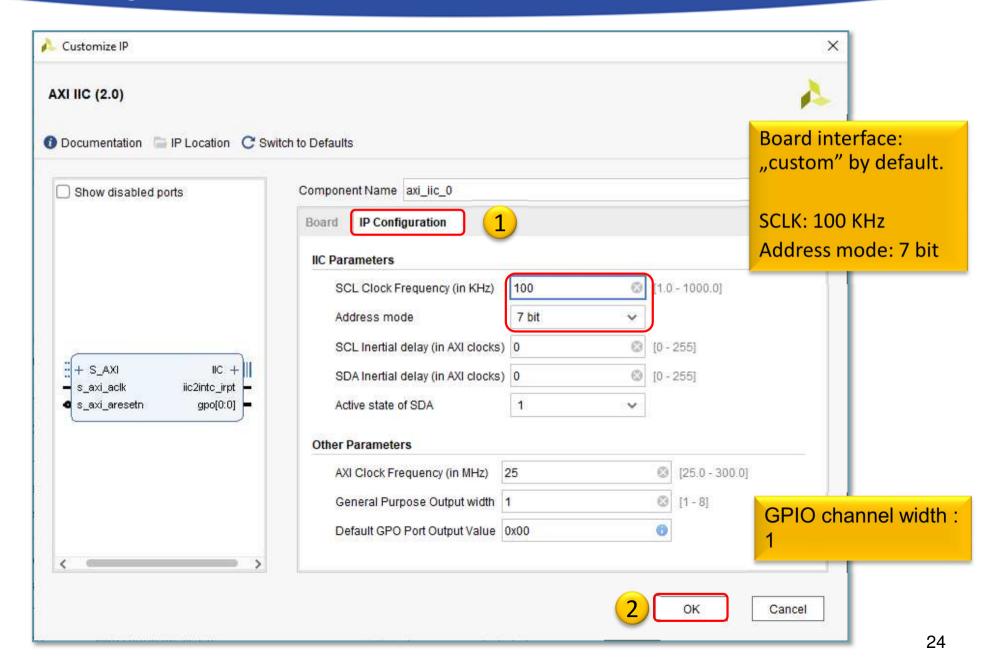

- Add an AXI\_IIC controller to the Block Diagram (IP Catalog)

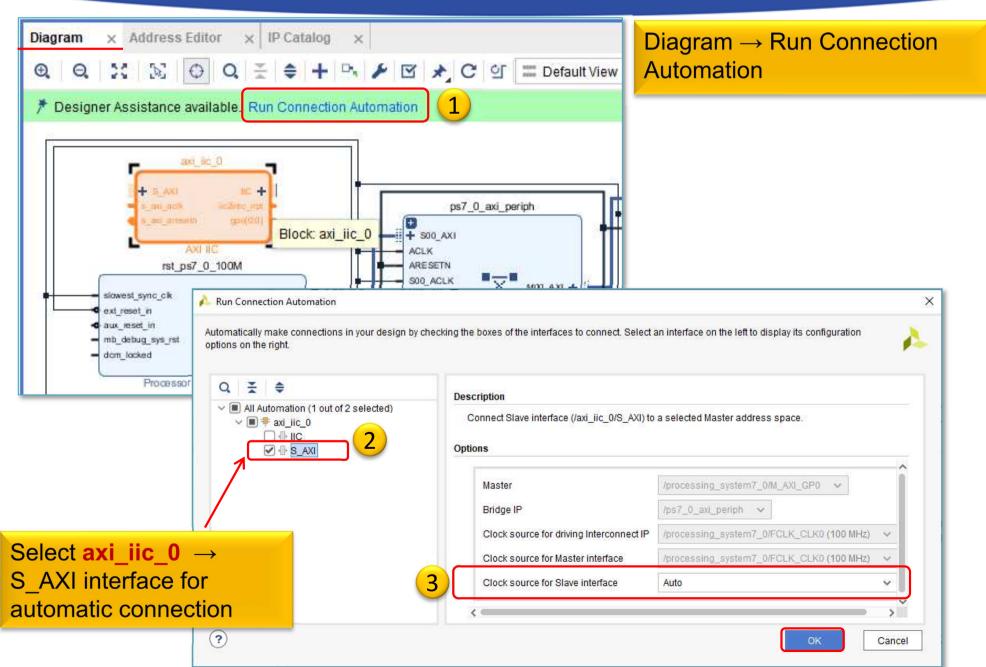

## Adding AXI IIC peripheral interface to the Base System II.

## Run Autorouter (AXI\_IIC)

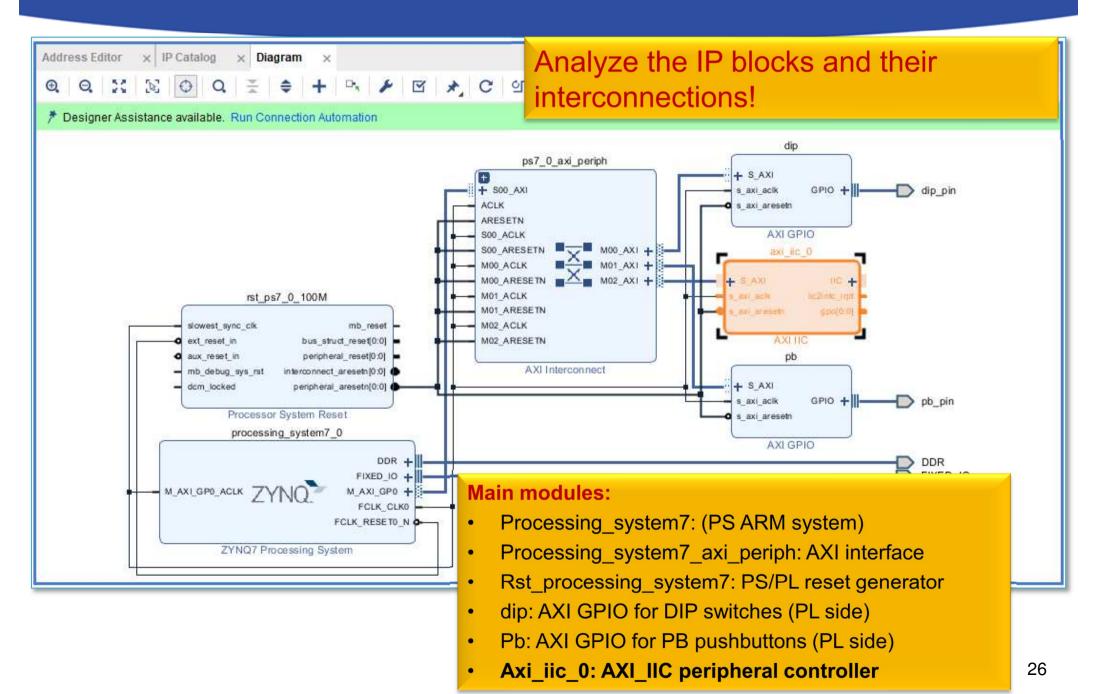

## Block Design – Analyze

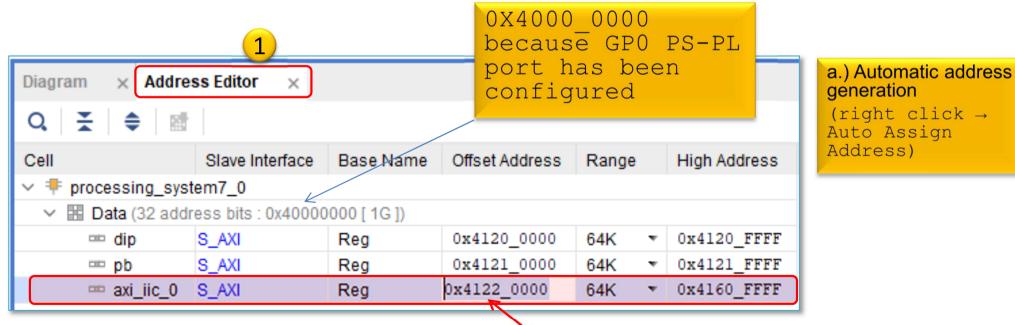

#### AXI IIC – Set memory address

- Block Design → select "Address Editor" view

- Assign "UnMapped" IP peripherals to the ARM's address range:

- a.) automatic vs. b.) manual address generation

2

b.) Base address manual set\*

Address ranges must be set to the size of 2<sup>n</sup> and cannot be overlapped!

Axi\_iic: 0x4122\_0000 (64K)

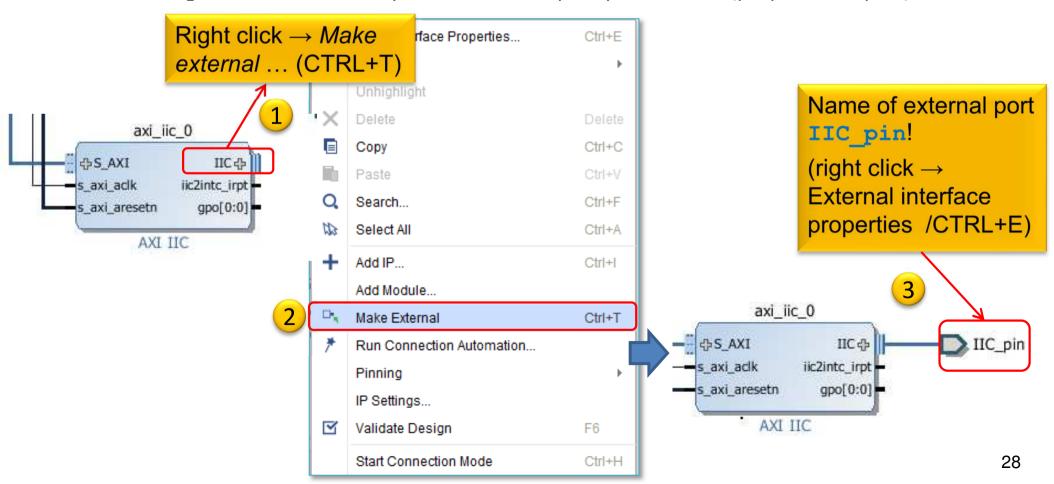

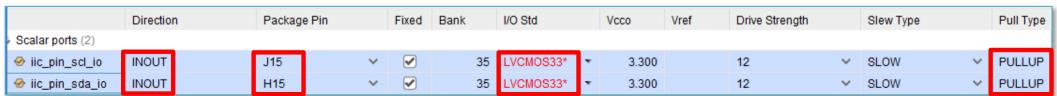

#### AXI IIC – Assign ports to external pins

The **AXI\_IIC** instance must be connected to the FPGA (PL-side) pins on the ZyBo card (PMOD JE 3-4 signals):

- 1. The AXI\_IIC ports must also be connected to the external physical FPGA pins,

- 2. If necessary, we also define the names of the external ports (ending in \_pin), then

- 3. In the <system> .XDC file you will need to specify constraints (proper FPGA pins).

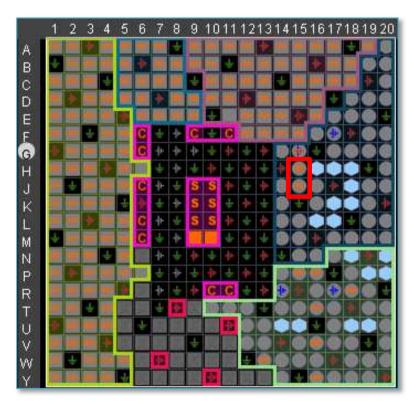

#### **Block Design – Layout synthesis**

- Block Design must be updated:

- Regenerate Layout

Validate Design (DRC)

Flow Navigator → Run Synthesis

- Then Open Synthesized Design , OK

- Finally, two FPGA I/O pins must also be assigned to the external ports (IIC\_pin)!

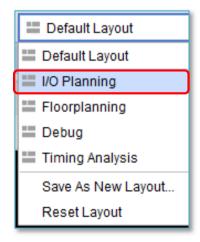

- Layout menu → "IO Planning" layout view

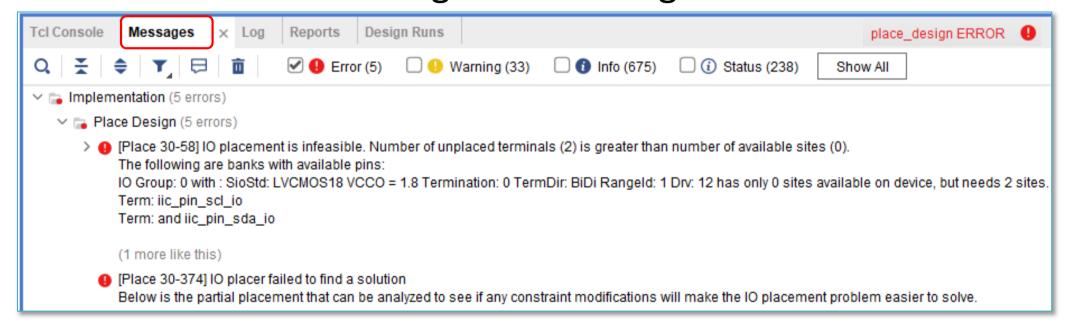

#### 10 Planning - Incorrect pin assignment

Note: If you immediately start the "Run Implementation" without constraining pins, you will receive the following error message:

- Cause: Vivado tryed to assign the I2C signals

- But assigned bad pin location and IO Standard (LVCMOS 1.8V)

30

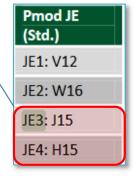

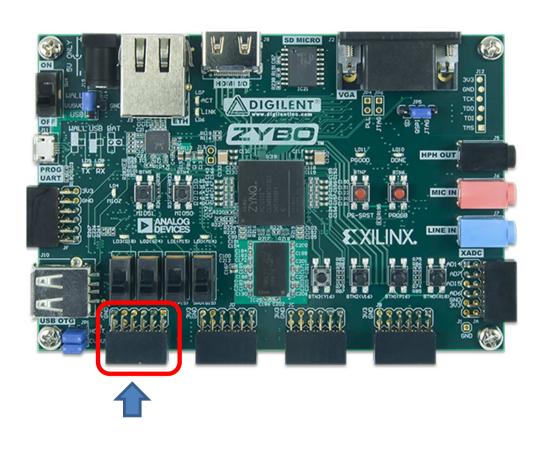

#### **ZyBo - PMOD connectors**

| Pmod JA<br>(XADC) | Pmod JB<br>(Hi-Speed) | Pmod JC<br>(Hi-Speed) | Pmod JD<br>(Hi-Speed) | Pmod JE<br>(Std.) | Pmod JF<br>(MIO) |

|-------------------|-----------------------|-----------------------|-----------------------|-------------------|------------------|

| JA1: N15          | JB1: T20              | JC1: V15              | JD1: T14              | JE1: V12          | JF1: MIO-13      |

| JA2: L14          | JB2: U20              | JC2: W15              | JD2: T15              | JE2: W16          | JF2: MIO-10      |

| JA3: K16          | JB3: V20              | JC3: T11              | JD3: P14              | JE3: J15          | JF3: MIO-11      |

| JA4: K14          | JB4: W20              | JC4: T10              | JD4: R14              | JE4: H15          | JF4: MIO-12      |

| JA7: N16          | JB7: Y18              | JC7: W14              | JD7: U14              | JE7: V13          | JF7: MIO-0       |

| JA8: L15          | JB8: Y19              | JC8: Y14              | JD8: U15              | JE8: U17          | JF8: MIO-9       |

| JA9: J16          | JB9: W18              | JC9: T12              | JD9: V17              | JE9: T17          | JF9: MIO-14      |

| JA10: J14         | JB10: W19             | JC10: U12             | JD10: V18             | JE10: Y17         | JF10: MIO-15     |

Now we use the standard PMOD **JE** 3-4 connector pins:

i2c\_scl : **J15**

i2c\_sda: **H15**

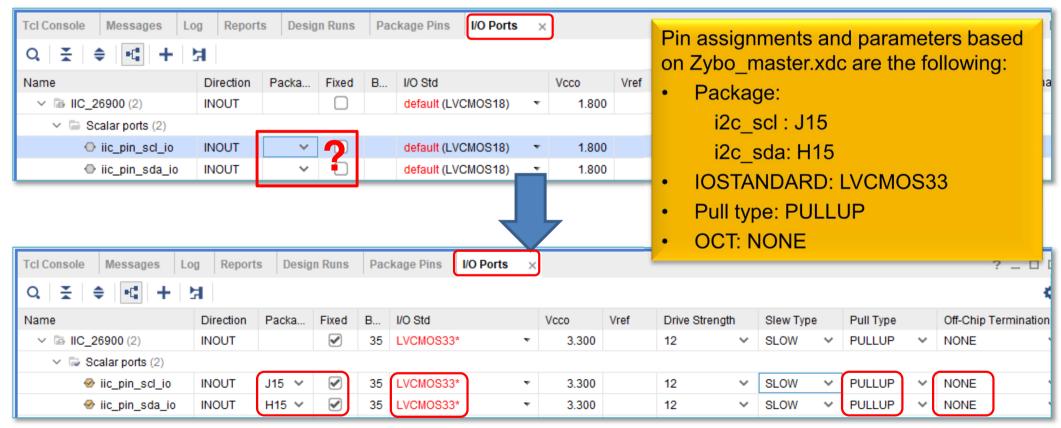

#### I/O Planning - Correct pin assignment I.

One option is to use Vivado IO Planning (GUI)

SYNTHESIS → Open Synthesized Design → I/O Planning

Finally *File* → *Save Constraints* or **CTRL+S**.

• Name the file: "lab02c.xdc"

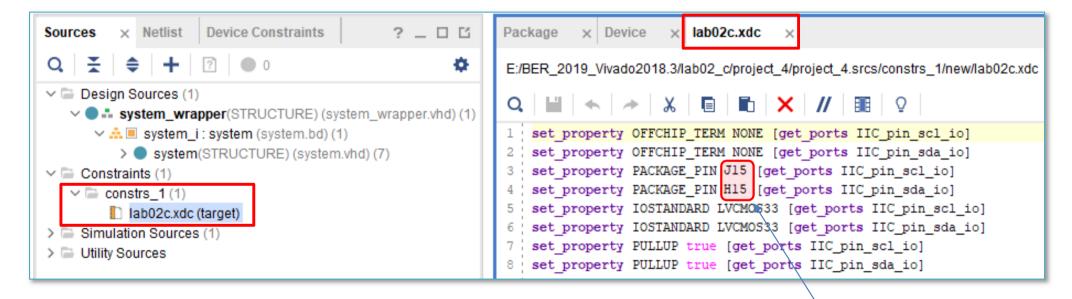

#### 10 Planning - Correct pin assignment II.

- 2. Another option is to edit .XDC constraints

- File  $\rightarrow$  Add Sources  $\rightarrow$  Add or Create constraints

- Create File, then giva a name: "lab02c.xdc"

Finally *File* → *Save Constraints* or CTRL+S.

Name the file: "lab02c.xdc"

## Implementation and Bitstream generation

Flow Navigator menu → Run Implementation

- It can filter out possible wrong assignments / errors,

- Warning messages are allowed (the design can be implemented),

- Some floating wires are also allowed (e.g. Peripheral Reset, etc.).

- While Vivado is working you can check out the synthesis/implementation reports!

Finally, run the Bitstream generation:

Flow Navigator → Generate Bitstream

#### Q&A 1.) Reports

How many resources are occupied on PL-side?

Reports → Report Utilization (or Project Summary Σ)

| +                                                                                                                                                                                                         | <br>  Used                                                                   | +<br>  Fixed                                | <br>Available                                                     | ++<br>  Util%  <br>++ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------|-----------------------|

| Slice LUTs<br>  LUT as Logic<br>  LUT as Memory<br>  LUT as Distributed RAM<br>  LUT as Shift Register<br>  Slice Registers<br>  Register as Flip Flop<br>  Register as Latch<br>  F7 Muxes<br>  F8 Muxes | 971  <br>899  <br>72  <br>0  <br>72  <br>1196  <br>1196  <br>0  <br>8  <br>4 | 0  <br>0  <br>0  <br>0  <br>0  <br>0  <br>0 | 17600<br>17600<br>6000<br>35200<br>35200<br>35200<br>8800<br>4400 | 1.20  <br>            |

| LUT - 6%  LUTRAM - 1%  FF - 3%  IO - 10%  BUFG - 3%                                                                                                                                                       |                                                                              |                                             |                                                                   | +                     |

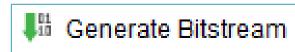

## Q&A 2.) I/O Planning

- Check where the I2C pins are located on the FPGA?

- Package Pins?

- Direction?

- I/O Standard?

- Pull type?

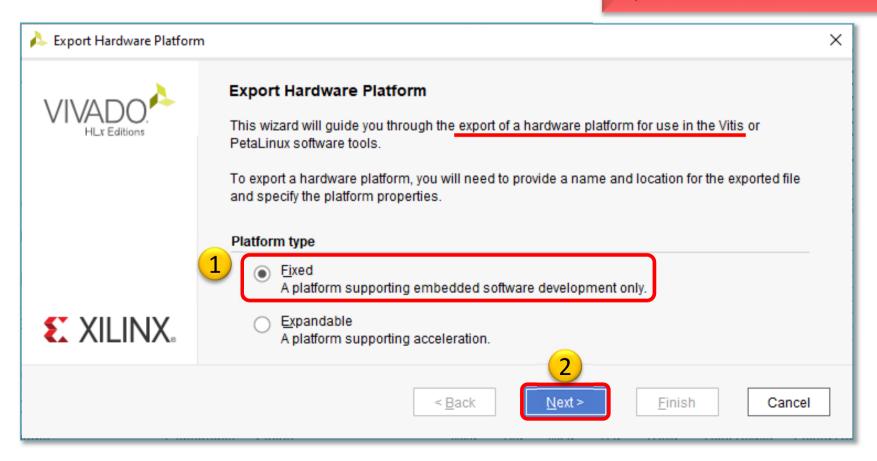

#### VIVADO Export HW → VITIS (~SDK)

• File  $\rightarrow$  Export  $\rightarrow$  Export Hardware...

2020.x: at least an Elaborated Design must be able to be exported to HW!

#### VIVADO Export HW → VITIS (cont.)

#### Select "Include bitstream" option as output:

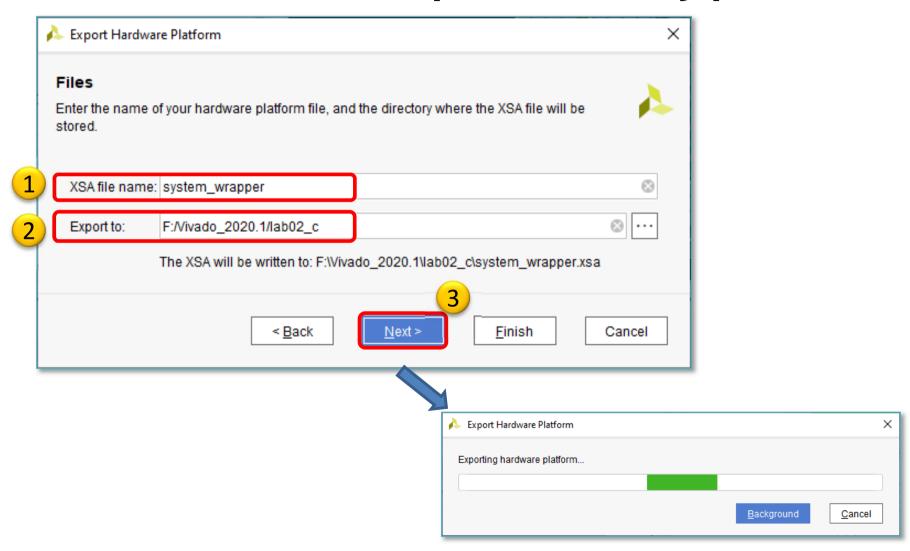

#### Export HW → VITIS (cont.)

#### Set XSA\* file name and export directory path:

#### **USING XILINX VITIS**

LAB02\_C. Creating a software test application

BEFEKTETÉS A JÖVŐBE

# VITIS – General steps of application development

- 1. Creating a Vivado project, then Export HW  $\rightarrow$  VITIS,  $\sqrt{\phantom{a}}$

- 2. Creating a new application or an application generated from a C/C ++ template (e.g. *TestApp* peripheral test):

- a. Importing .XSA

- b. Generating and compiling an application project containing a platform and a domain inside (~BSP: Board Support Package),

- c. Generating a **Linker Script** (specifying memory sections, . LD),

- d. Writing / generating and compiling the **SW** application

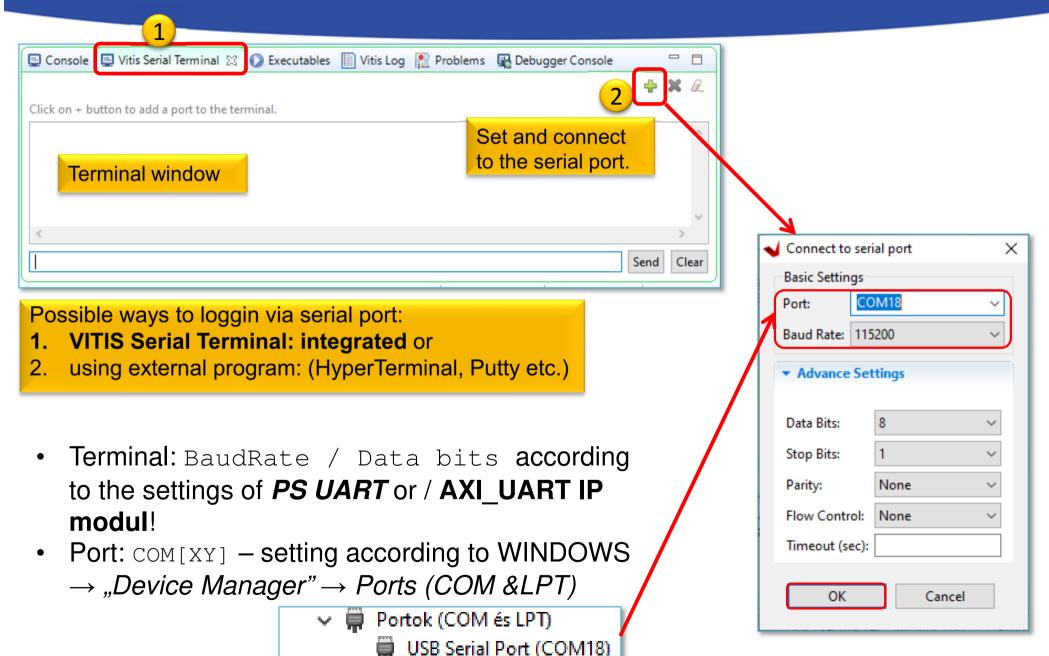

- 3. Setup a Serial terminal/Console (USB-serial port),

- 4. Connecting and setup a JTAG-USB programmer,

- Configuring the FPGA (.BIT if PL-side existing)

- 5. Creating a 'Debug Configuration' for hardware debugging

- 6. Debug (insert breakpoints, stepping, run, etc.)

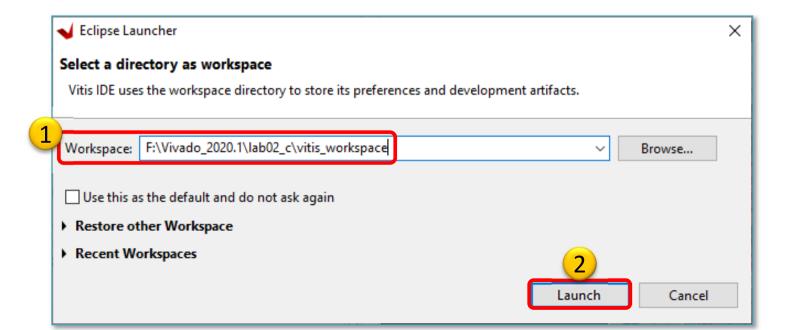

#### **Starting VITIS**

From Vivado: Tools menu → Launch VITIS IDE

OR externally

Start menu → Programs → Xilinx Design Tools → Xilinx VITIS 2020.1

Do Not run Xilinx VITIS HLS 2020.1!

- Set workspace directory properly (1ab02\_c):

- Recommended to use <u>vitis\_workspace</u> as a subdirectory in your lab folder. Then Launch...

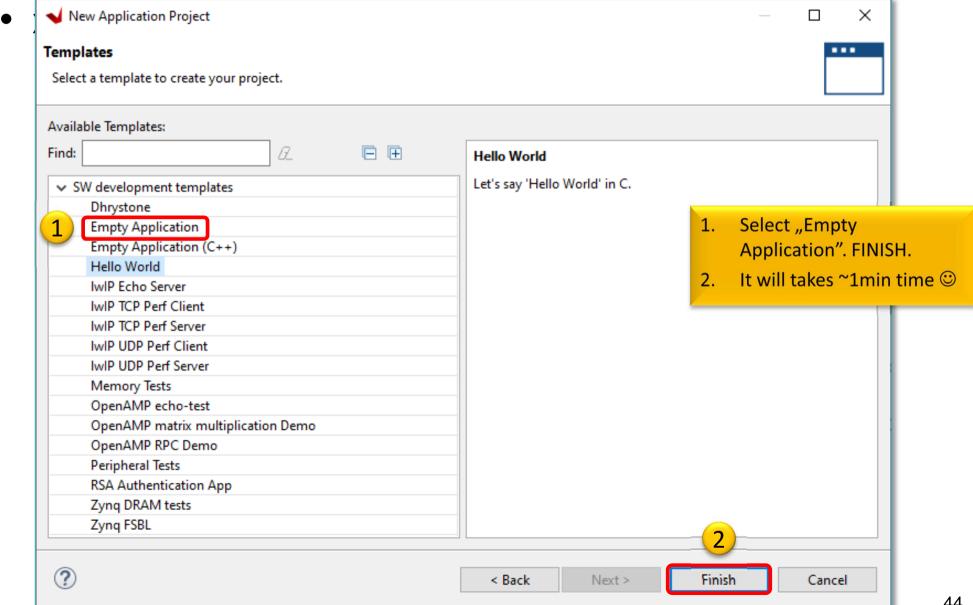

#### Xilinx VITIS – Create Application

#### Recall the steps of the former LAB01/LAB02\_A!

#### 1. Create a new application project

File → New → Application Project...

#### 2. Platform – Create a new platform from HW (XSA)

- Browse... for LAB02\_C system\_wrapper.xsa. Open it.

- Do not select the "Generate boot components"

#### 3. Application project details

- Type "TestApp" as project name

- Type "TestApp\_system" as system project name

- Select ps7\_cortexa9\_0 as target ARM core 0

#### 4. Domain: leave settings as default (standalone)

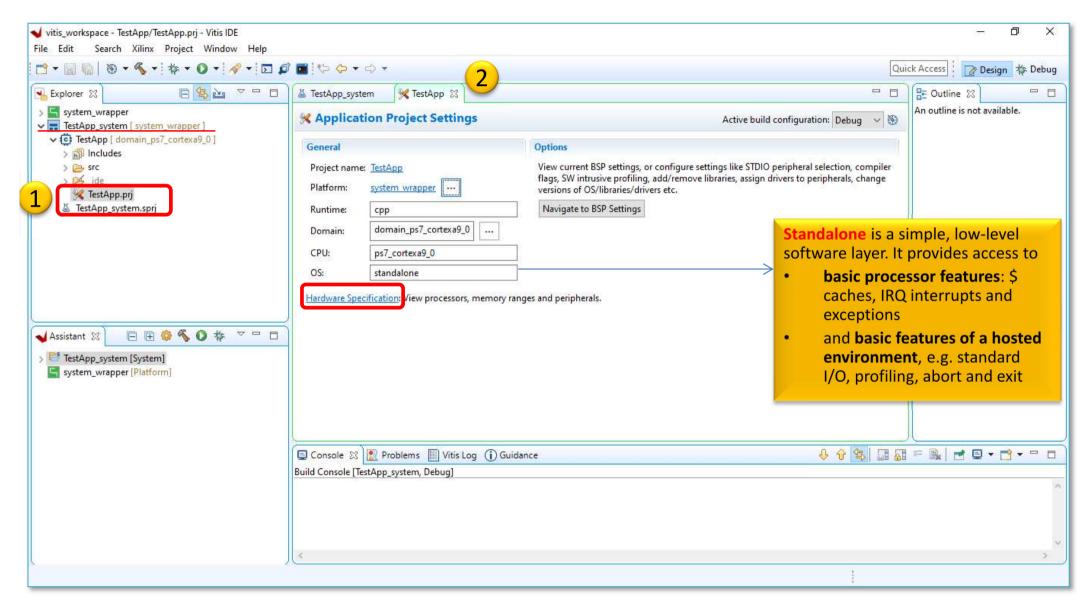

# **Example I.) Creating TestApp** application

#### VITIS GUI – Main window

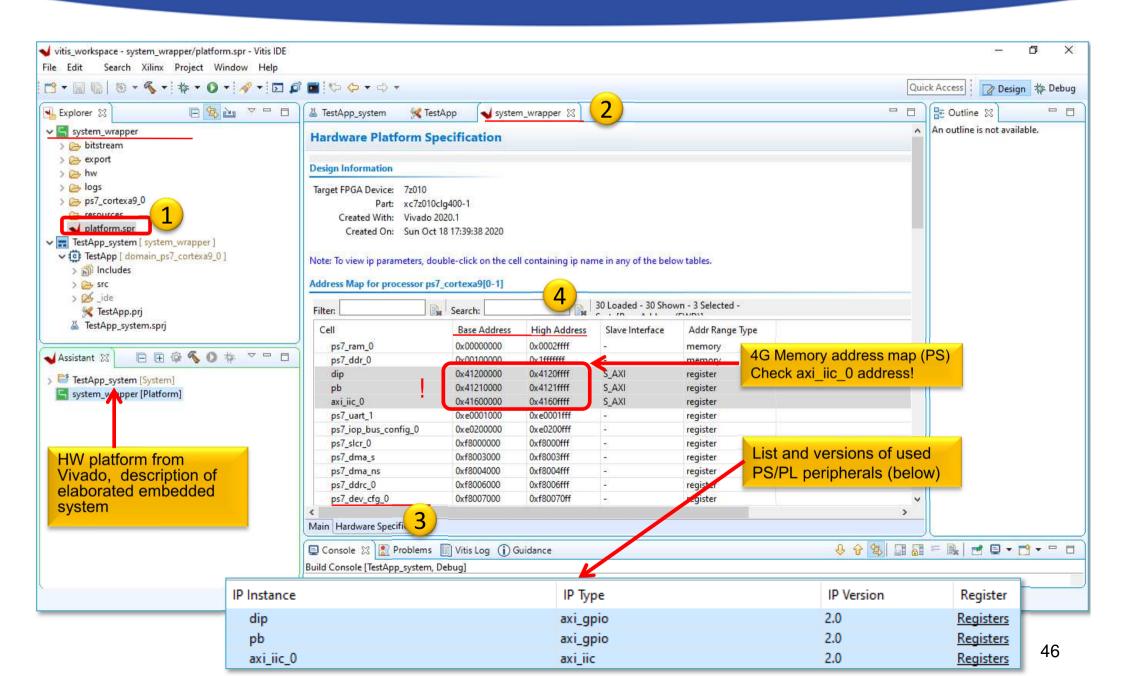

#### VITIS – HW platform

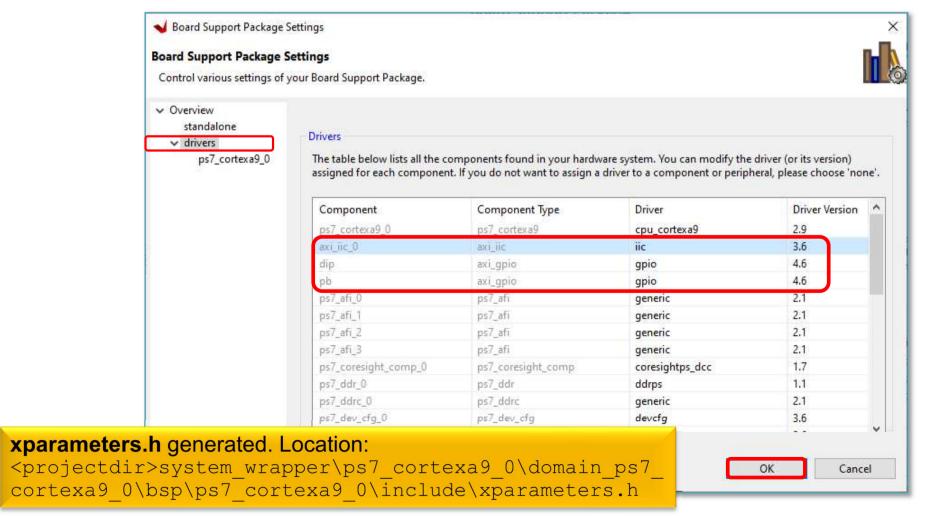

#### VITIS – BSP Board Support Package

#### Software Platform Settings

- Selected OS: standalone

- Check the supported SW drivers (and its version): "axi\_iic"

#### Q & A 1.)

What is the *IP type* and *IP version* of "axi\_iic\_0" instance?

```

axi_iic,

```

- v2.0

- What is the driver name and version of it?

- iic,

- v3.6

- Calculate what size they are?

- $axi_ic_0: 0x4160 0000-0x4160 ffff = 64 KByte$

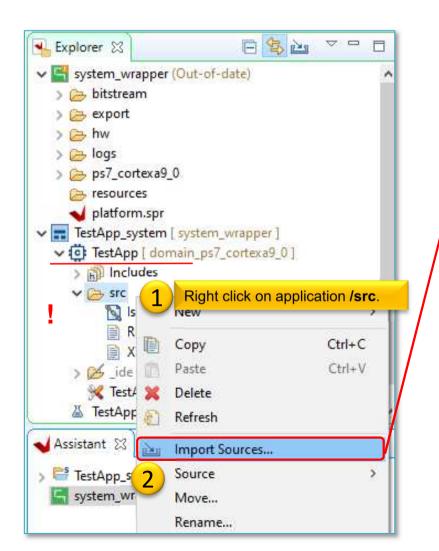

# Import C/C++ source(s)

1. Download and unpack the .zip archive

Download the archive from lab's website:

BER PmodTMP2 DriverFiles.zip

2. Import all sources to the application project

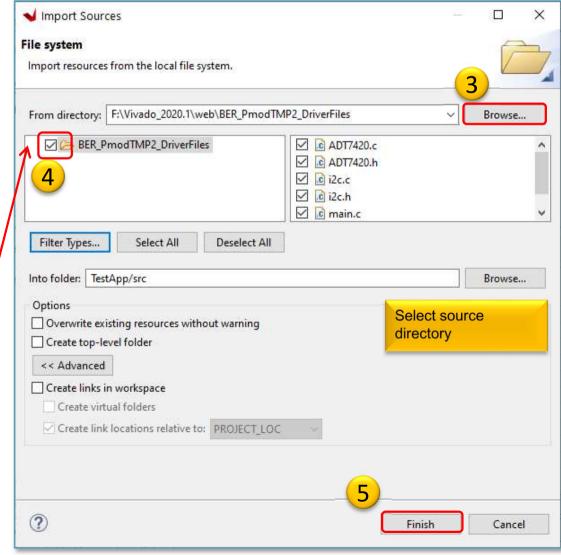

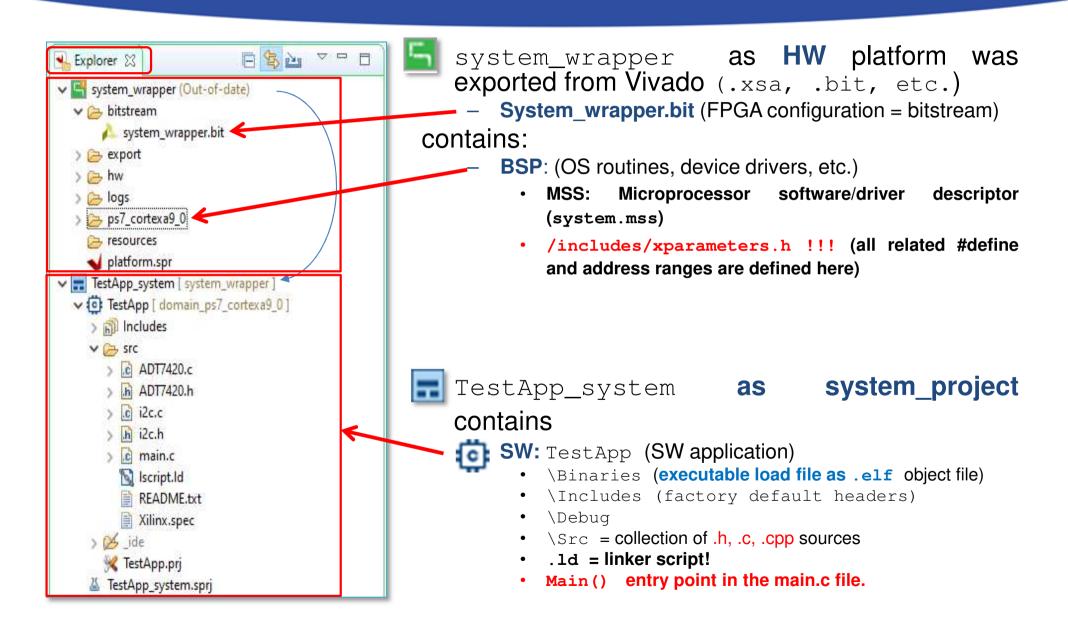

# VITIS – Project Explorer / Hierarchy

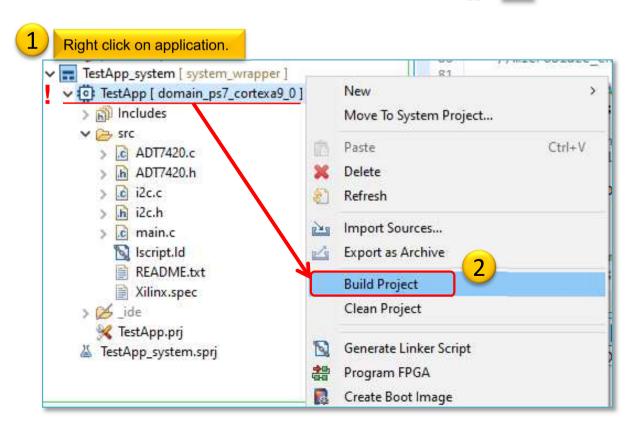

# **Build project**

- 1. Select Application project (e.g. TestApp)

- 2. Project menu → Build Project... in two steps:

- a) Build BSP (system\_wrapper)

- b) Build software application (main.c) 🧔 📰

# Build project – Result (Console)

```

'Building target: TestApp.elf'

'Invoking: ARM v7 gcc linker'

arm-none-eabi-gcc -mcpu=cortex-a9 -mfpu=vfpv3 -mfloat-abi=hard -Wl,-

build-id=none -specs=Xilinx.spec -Wl,-T -Wl,../src/lscript.ld -

LF:/Vivado 2020.1/lab02 a/vitis workspace/system wrapper/export/syste

m_wrapper/sw/system_wrapper/domain_ps7_cortexa9_0/bsplib/lib -o

"TestApp.elf" ./src/lab2 a.o -Wl,--start-group,-lxil,-lgcc,-lc,--

end-group

'Finished building target: TestApp.elf'

'Invoking: ARM v7 Print Size'

arm-none-eabi-size TestApp.elf

|tee "TestApp.elf.size"

data

dec

hex filename

text

bss

22840

1176 22584 46600

b608 TestApp.elf

'Finished building: TestApp.elf.size'

```

**Decimal size: 46600 byte** ~46 KByte . The entire program can be placed both the internal on-chip RAM 0/1 and the external DDR RAM. (On the PL / FPGA-side, however, this amount of BRAM memory should be reserved). Therefore, the executable .elf file was also generated successfully.

#### **Correct TestApp**

```

In file included from ../src/ADT7420.c:49:0:

../src/ADT7420.c: In function 'ADT7420_Init':

../src/ADT7420.h:49:22: error: 'XPAR_AXI_IIC_BASEADDR' undeclared (first use in this function)

#define IIC_BASEADDR XPAR_AXI_IIC_BASEADDR

```

Solution: check and correct the XPAR\_AXI\_IIC\_BASEADDR define in the ADT7420.h based on xparameters.h file

```

2.) ../src/ADT7420.h:53:28: error: expected expression before '<' token #define ADT7420_IIC_ADDR <address>

```

Solution: examine the ADT7420\_IIC\_ADDR for correct addressing (see PMOD TMP2 datasheet and former slide 20-21 pp)

```

3.) ../src/main.c: In function 'main':

|../src/main.c:78:12: error: 'XPAR_RS232_UART_1_BASEADDR' undeclared (first use in this function)

| Xil_Out32(XPAR_RS232_UART_1_BASEADDR+0x0C, (1 << 4));</p>

```

Solution: find and check the define in ADT7240.h file

If they has been successfully corrected uncomment lines 90-94 (while) in the main.cpp.

#### Build

- Generate Linker Script to the interanal on-chip PS7 RAM0

- Set the Heap / Stack size to 2KB!

- Now rebuild the TestApp again.

#### Q: What is the size of TestApp.elf binary?

```

'Invoking: ARM v7 Print Size'

arm-none-eabi-size TestApp.elf | tee "TestApp.elf.size"

text data bss dec hexfilename

27468 1144 10296 38908 97fcTestApp.elf

'Finished building: TestApp.elf.size'

```

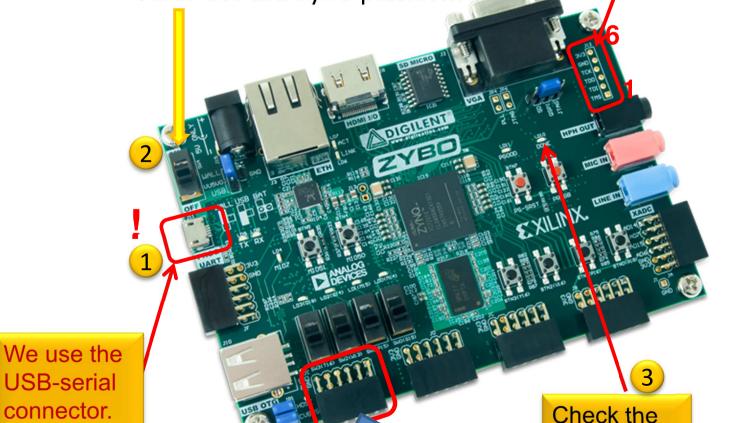

# **Connect PMOD TMP2 to ZyBo**

• Be sure the proper connection for PMOD JE conn.

# Embedded system and software test verification

JTAG programming port

(optional, but we don't

**DONE led!**

use it!)

**Connect** the USB-serial cable (power+programmer functionality). Please

check:

**USB-serial**

connector.

JP7 jumper = USB power!

JP5 jumper = JTAG mode!

2. Now **Power ON** the ZyBo platform

```

ZyBo - Xilinx USB programming

cable

VCC3V3 - red VREF (6)

GND - black GND (5)

TDO-FX2 - lilac - TDO (3)

TDI-JTAG – white TDI (2)

TMS-JTAG - green TMS (1)

```

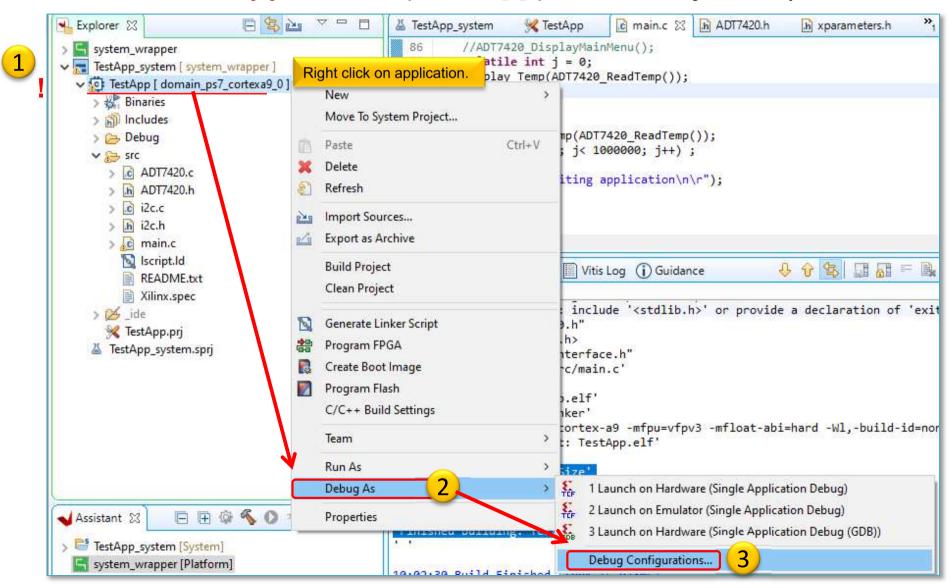

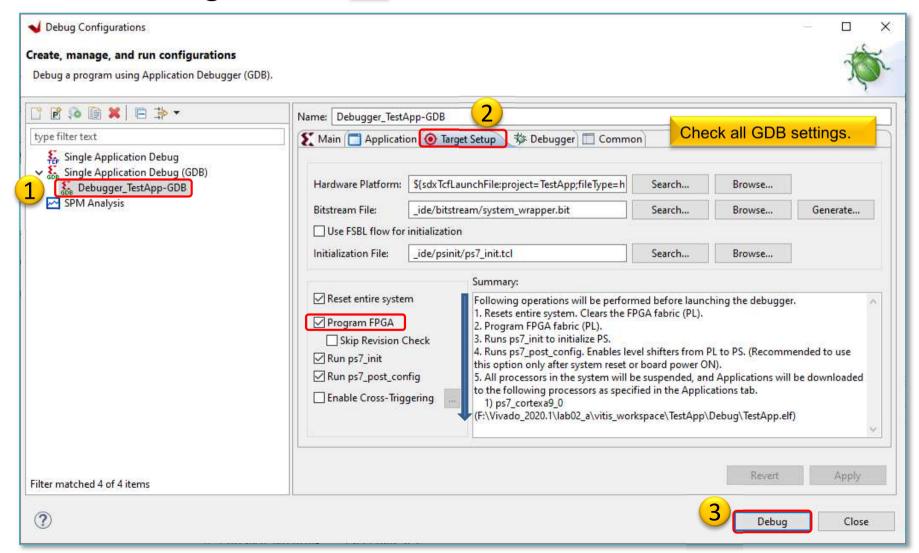

# **Creating Debug Configuration**

Select the application (TestApp) in the Project Explorer

#### Create a new GDB configuration

Select "Single Application Debug (GDB)" option

New configuration

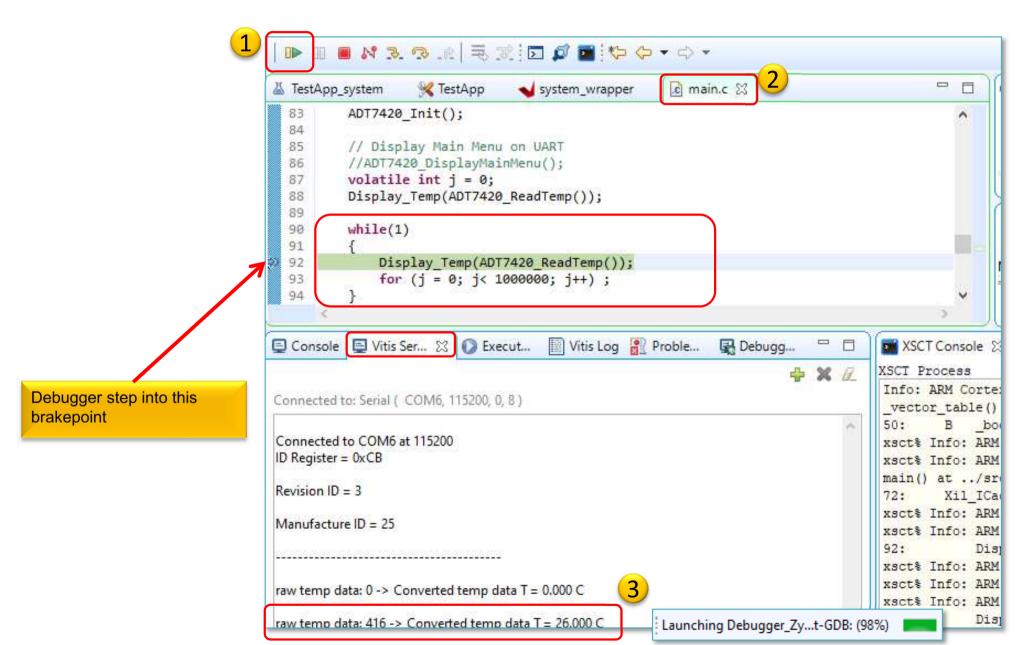

# Launching Debugger

# Set Debug-serial port (VITIS terminal)

#### TestApp – Verification result

Check debug output on VITIS terminal. What did you experience?

```

ID Register = 0xCB

Revision ID = 3

Manufacture ID = 25

raw temp data: 0 -> Converted temp data T = 0.000 C

raw temp data: 416 -> Converted temp data T = 26.000 C

raw temp data: 416 -> Converted temp data T = 26.000 C

raw temp data: 419 -> Converted temp data T = 26.187 C

raw temp data: 419 -> Converted temp data T = 26.187 C

raw temp data: 419 -> Converted temp data T = 26.187 C

```

Analyze the source code! What is the difference between raw data vs. converted temperature data?

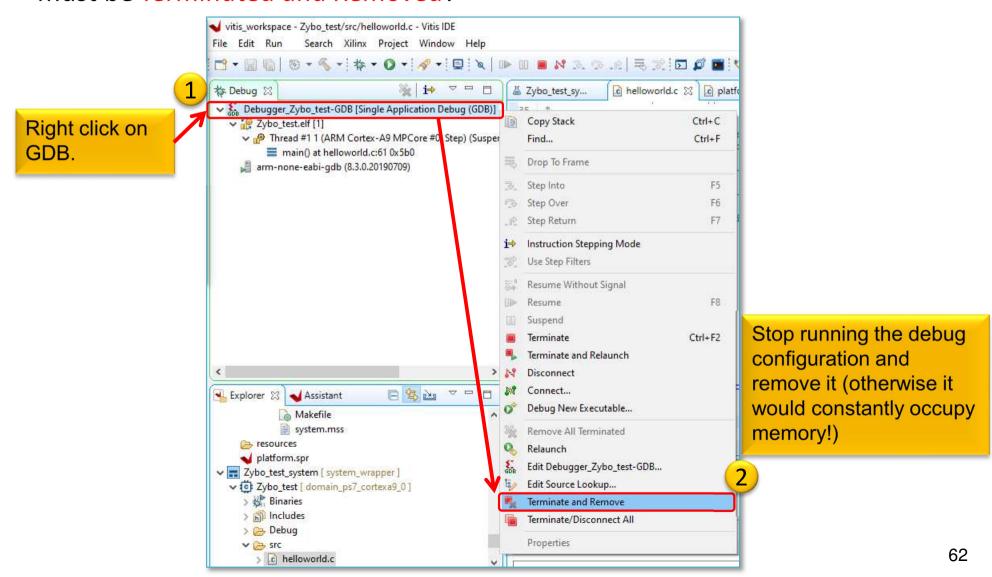

#### **Terminate Debug process**

• IMPORTANT! At the end of the HW debug, the running debug configuration must be *Terminated and Removed*!

# LAB02\_B and C – Summary

- To the ARM-AXI based system created in the previous (5. LAB02\_A), here we added new PL-side AXI GPIO and AXI IIC peripherals from the Vivado IP catalog.

- Peripherals were properly configured and connected to the external I/O pins of the FPGA.

- We examined both the Block Diagram and the report files.

- **LED displays** (4) and **IIC interfaces** (2) on the ZyBo card have been assigned to the pin assignments.

- Finally, we verified the completed embedded system (HW+FW) and the correct operation of various SW applications (TestApp, and Peripheral Test) in VITIS unified environment.

EFOP-3.4.3-16-2016-00009

A felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása a Pannon Egyetemen

# THANK YOU FOR YOUR KIND ATTENTION!

BEFEKTETÉS A JÖVŐBE